基于Verilog有限状态机实现的LED按键灯项目

- 项目实现功能

- 项目环境

- 具体代码

- 仿真代码及波形图

- 约束文件代码

- 过程中遇到的错误及解决方法

- 上板实验

项目实现功能

通过按键控制,模仿市面上的台灯开关,即通过按键控制灯的状态。该项目假设led按键灯共有四种状态,分别是红灯,黄灯,蓝灯。 通过按键按下,改变当前led灯的状态。例:当前为熄灭状态,按下按键后红灯亮起。

项目环境

1.vivado 2019.1

2.xilinx Fpga AX7035开发板

具体代码

下面展示具体实现代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/04/19 15:50:32

// Design Name:

// Module Name: Led

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module Led(

input key,

input reset,

output reg [2:0]led

);

parameter Led_off=2'b00;

parameter Led_red=2'b01;

parameter Led_yellow=2'b10;

parameter Led_blue=2'b11;

reg [1:0]current_state;

reg [1:0]next_state;

always @(posedge key or negedge reset)

begin

if(~reset)

begin

current_state <= Led_off;

// led <= 3'b000;

end

else

current_state <= next_state;

$display ("curr_state is %d",current_state);

end

always@( current_state or reset )

begin

begin

case (current_state)

Led_off: next_state = Led_red;

Led_red: next_state = Led_yellow;

Led_yellow: next_state = Led_blue;

Led_blue: next_state = Led_off;

default: next_state = Led_off;

endcase

end

end

always @(current_state or reset )

begin

case( current_state)

Led_off : led = 3'b111;

Led_red : led = 3'b110;

Led_yellow : led = 3'b101;

Led_blue: led = 3'b011;

default: led =3'b111;

endcase

end

endmodule

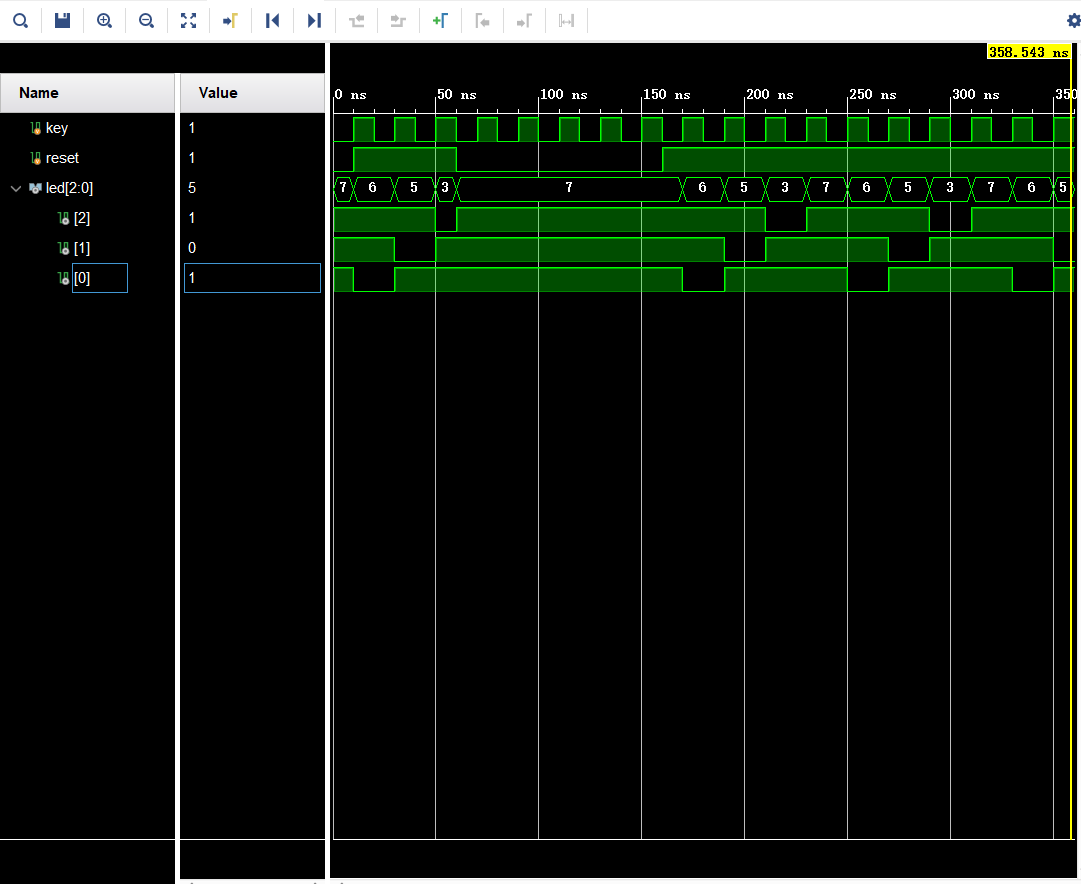

仿真代码及波形图

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/04/19 16:10:38

// Design Name:

// Module Name: Sim_led

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module Sim_led;

reg key,reset;

wire [2:0]led;

Led l1(key,reset,led);

initial

begin

key=0;

reset= 0;

#10 reset=1;

#50 reset =0;

#100 reset = 1;

#200 $stop;

end

always #10 key = ~key;

endmodule

约束文件代码

############## NET - IOSTANDARD ##################

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

#############SPI Configurate Setting##################

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

############## clock and reset define##################

#create_clock -period 20 [get_ports {clk}]

#set_property IOSTANDARD LVCMOS33 [get_ports {clk}]

#set_property PACKAGE_PIN Y18 [get_ports {clk}]

set_property IOSTANDARD LVCMOS33 [get_ports {reset}]

set_property PACKAGE_PIN F20 [get_ports {reset}]

#############LED Setting#############################

set_property PACKAGE_PIN F19 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN E21 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property PACKAGE_PIN D20 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

############## key define##############################

set_property PACKAGE_PIN M13 [get_ports key]

set_property IOSTANDARD LVCMOS33 [get_ports key]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets key]

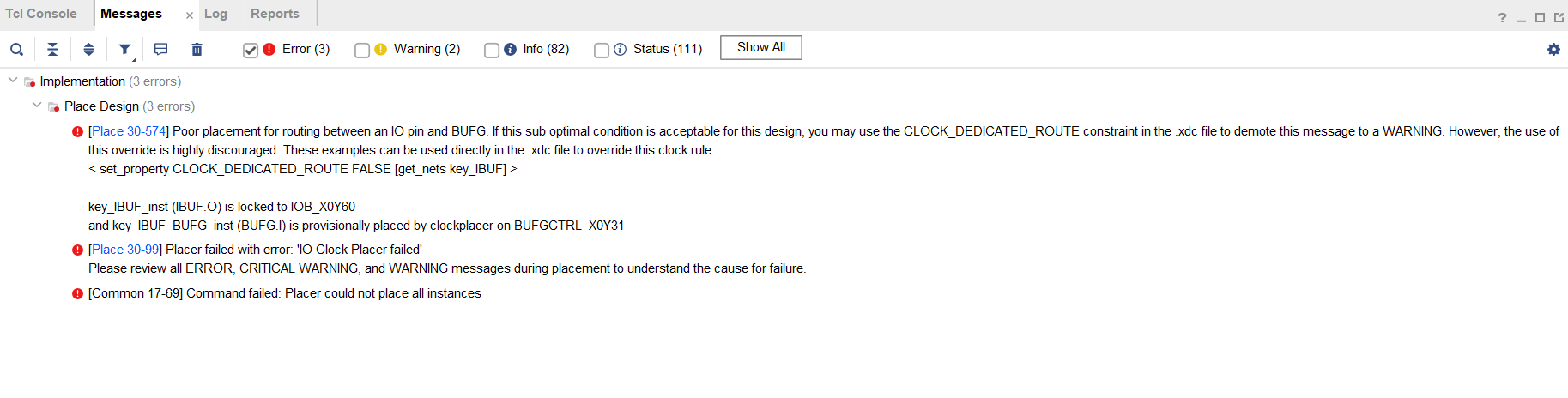

过程中遇到的错误及解决方法

[Place 30-574] Poor placement for routing between an IO pin and BUFG.

If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets key_IBUF] >

key_IBUF_inst (IBUF.O) is locked to IOB_X0Y60

and key_IBUF_BUFG_inst (BUFG.I) is provisionally placed by clockplacer on BUFGCTRL_X0Y31

经过查阅资料,发现是该项目并未使用fpga开发板原置的内部晶振作为时钟,而是通过按键模拟时钟信号导致.

解决方法:

在约束文件中加入如下语句:

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets key]

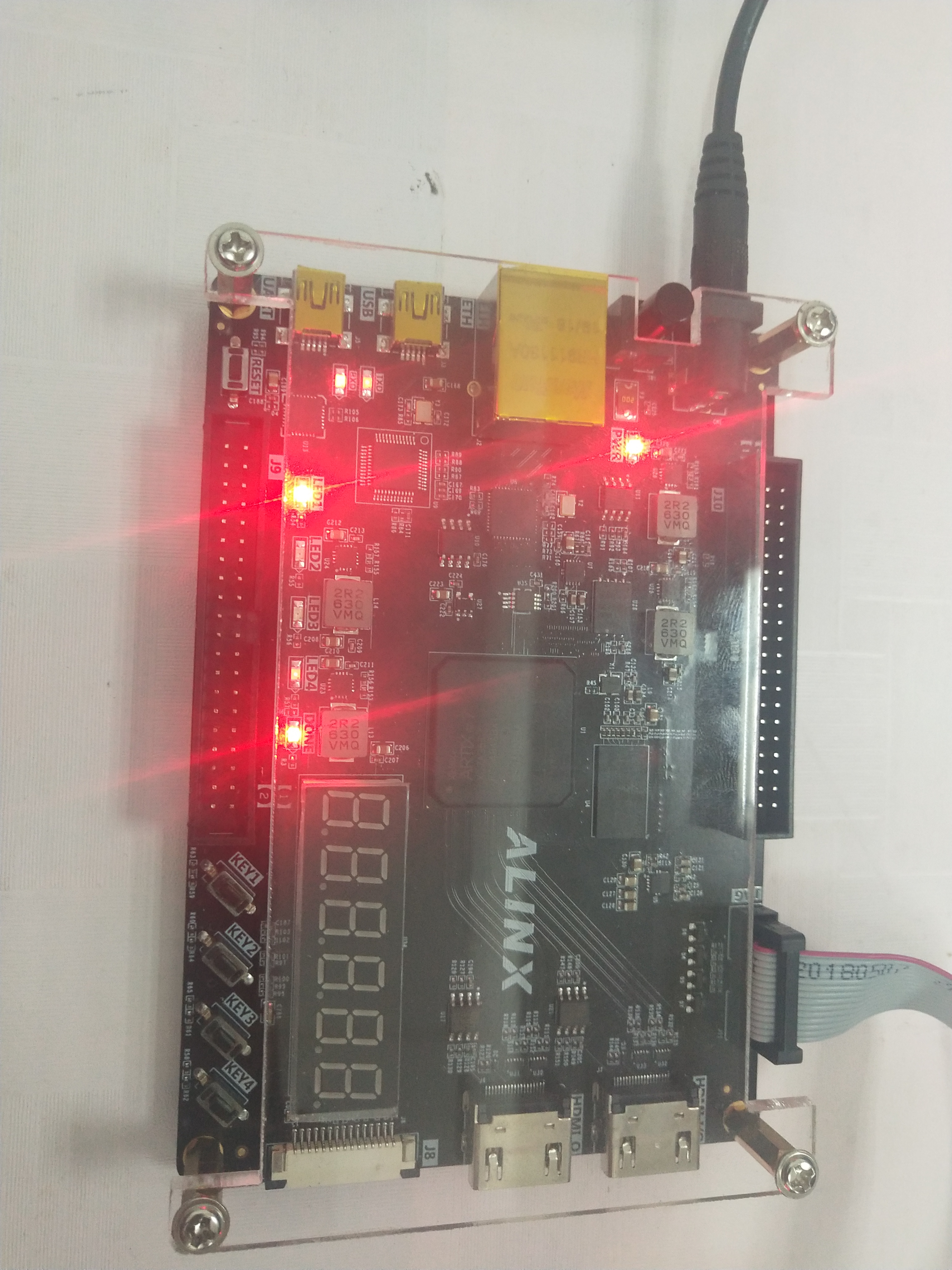

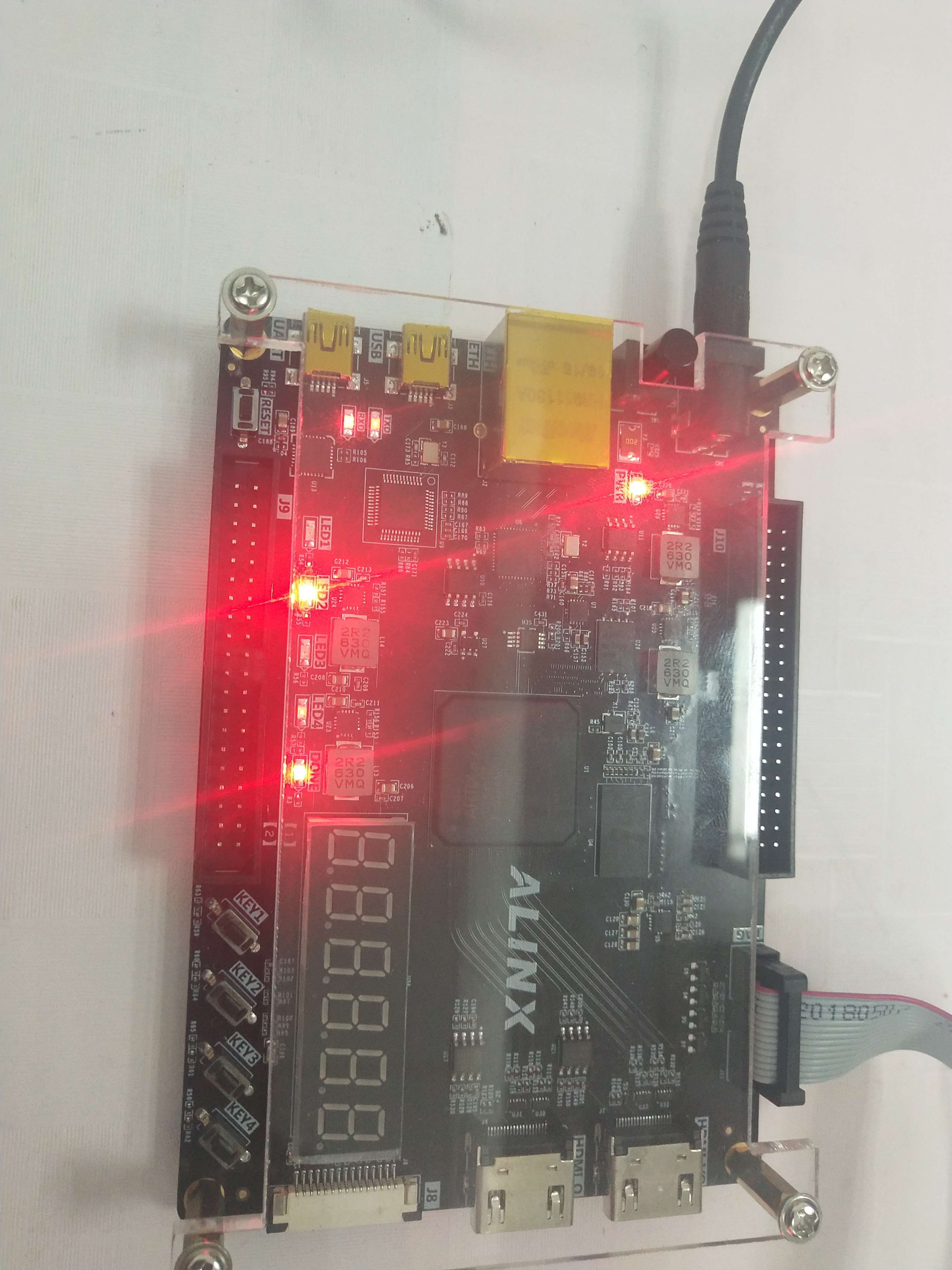

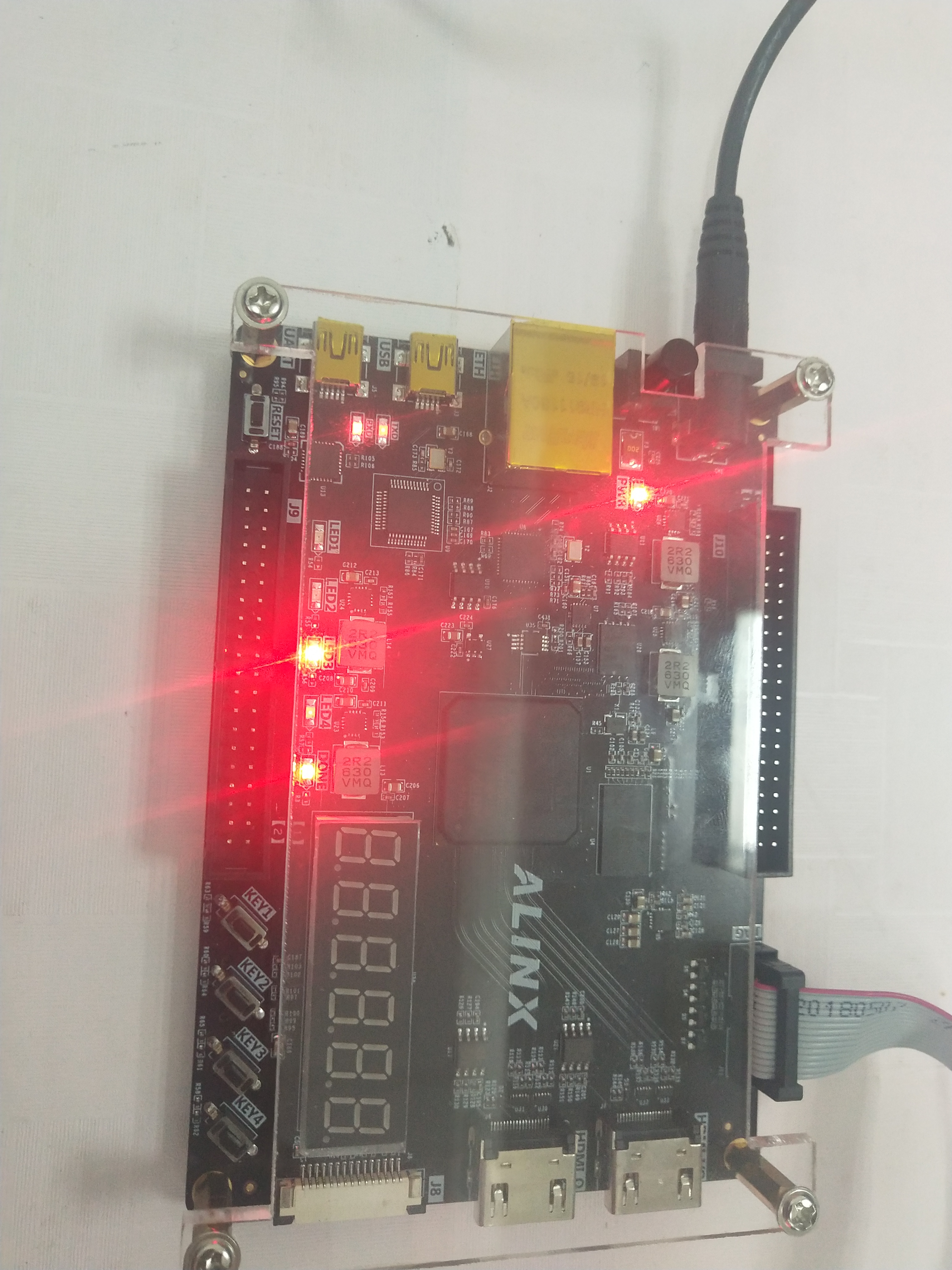

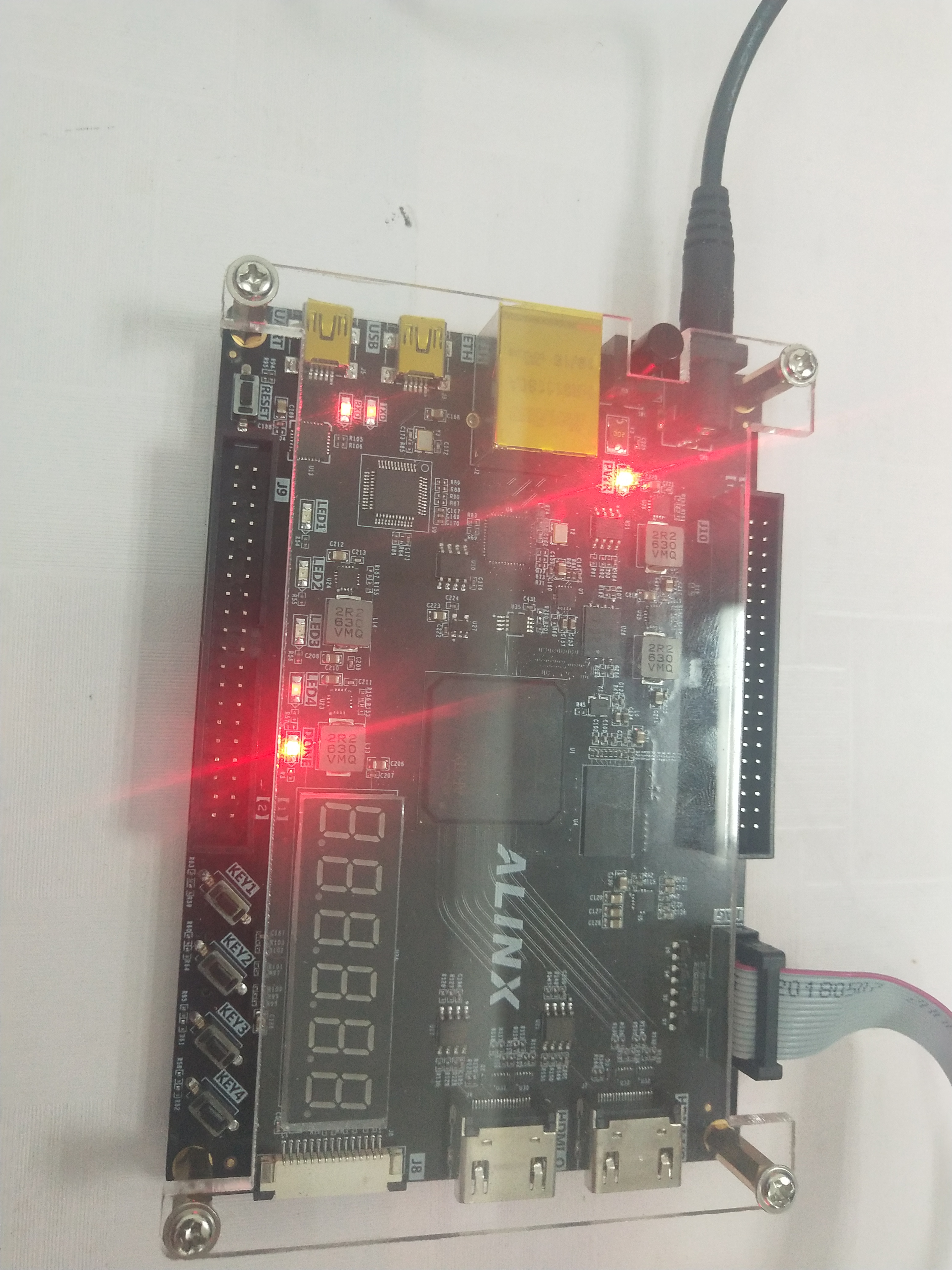

上板实验

由于fpga板并没有多种颜色的灯,故使用多个led灯进行模拟。

具体图片如下(视频无法上传):

最后

以上就是活力柚子最近收集整理的关于基于Verilog有限状态机实现的LED按键灯项目项目实现功能项目环境具体代码仿真代码及波形图约束文件代码过程中遇到的错误及解决方法上板实验的全部内容,更多相关基于Verilog有限状态机实现内容请搜索靠谱客的其他文章。

发表评论 取消回复