Verilog利用状态机实现交通灯控制

- 状态机

- 状态表

- 状态图

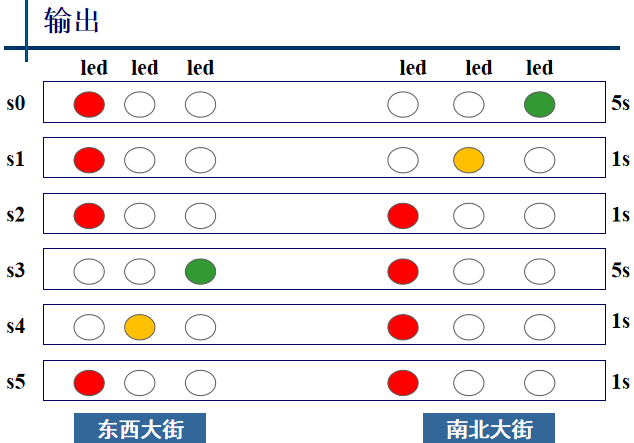

- 输出

- 代码实现

- 功能模块

- 测试模块

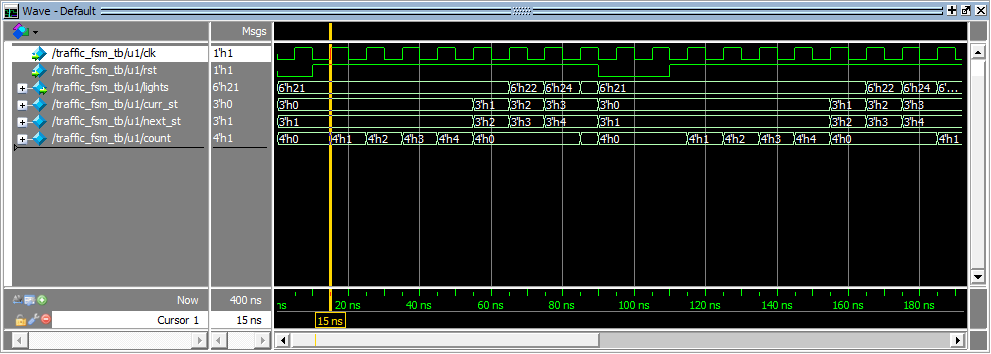

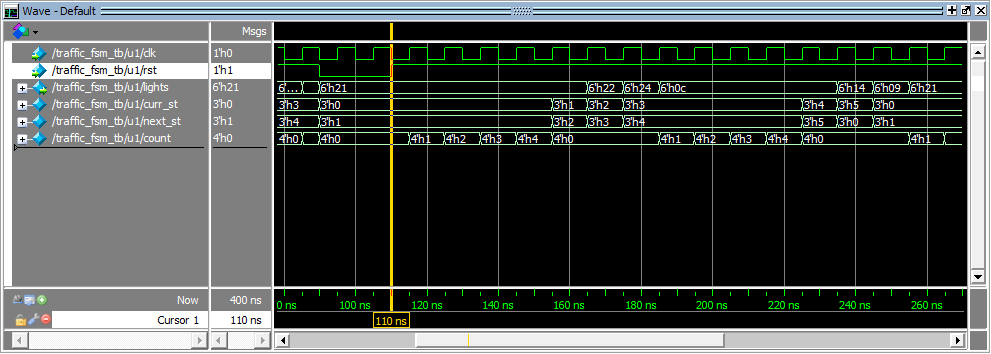

- 仿真波形

状态机

在一些应用中,通常希望产生任意的状态序列,并且每个状态停留任意时间。采用状态机的设计思想实现。

举例:交通灯

状态表

状态图

输出

代码实现

lights[5:0]:GYR_GYR

哪个亮,对应位置1

功能模块

module traffic_fsm (lights, clk, rst);

input clk, rst;

output [5:0] lights;

wire clk, rst;

reg [5:0] lights;

// define reg

reg [2:0] curr_st;

reg [2:0] next_st;

reg [3:0] count;

// define state

parameter s0 = 3'b000;

parameter s1 = 3'b001;

parameter s2 = 3'b010;

parameter s3 = 3'b011;

parameter s4 = 3'b100;

parameter s5 = 3'b101;

// define lights

parameter light0 = 6'b100_001;

parameter light1 = 6'b100_010;

parameter light2 = 6'b100_100;

parameter light3 = 6'b001_100;

parameter light4 = 6'b010_100;

parameter light5 = 6'b100_100;

// define time delay

parameter delay5 = 5;

parameter delay1 = 1;

// 产生一个可能的状态变化

always @ (posedge clk or negedge rst) begin

if (!rst) begin

curr_st <= s0;

count <= 0;

end

else

// curr_st = next_st;

begin

if (curr_st == s0 | curr_st == s3)

if (count < delay5 - 1)

count <= count + 1;

else begin

curr_st <= next_st;

count <= 0;

end

else if (curr_st == s1 | curr_st == s2 | curr_st == s4 | curr_st == s5) begin

curr_st <= next_st;

count <= 0;

end

end

end

// 产生下一个状态的组合逻辑

always @ (curr_st) begin

case (curr_st)

s0:

next_st <= s1;

s1:

next_st <= s2;

s2:

next_st <= s3;

s3:

next_st <= s4;

s4:

next_st <= s5;

s5:

next_st <= s0;

default: begin

next_st <= s0;

end

endcase

end

// 产生输出lights的组合逻辑

always @ (posedge clk or negedge rst) begin

if (!rst) lights = light0;

else

case (curr_st)

s0: lights = light0;

s1: lights = light1;

s2: lights = light2;

s3: lights = light3;

s4: lights = light4;

s5: lights = light5;

default: lights = light0;

endcase

end

endmodule

测试模块

// testbench of 'traffic_fsm'

module traffic_fsm_tb;

reg clk, rst;

wire [5:0] lights;

traffic_fsm u1 (.lights(lights), .clk(clk), .rst(rst));

initial begin

clk = 0;

rst = 0;

#10 rst = 1;

#80 rst = 0;

#20 rst = 1;

end

always #5 clk = ~clk;

endmodule

仿真波形

在第一个always块中产生下一个状态,写的不简洁

最后

以上就是香蕉睫毛最近收集整理的关于Verilog状态机实现交通灯控制的全部内容,更多相关Verilog状态机实现交通灯控制内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复