一、题目

计数器实现数字钟60秒计数设计实验

二、源代码

说明:本实验实现了数字钟60秒计数设计;可以输出定时时间eg:11.22s,即11s、22ms,两个参数通过COUTS、COUTMS输出;同时,可以输出溢出位,当60s定时到达时,OV输出1,反之,OV输出0。本实验的时钟频率为50MHz。

顶层文件:

//----------------------------------------------------------------------------------------

// File name: Timer60s

// Last modified Date: 2020年5月30日11点10分

// Last Version: V1.1

// Descriptions: 定时60s,可以输出ms及s数据,精度可达10ms

//----------------------------------------------------------------------------------------

module Timer60s(CLK,RST,EN,COUTS,COUTMS,OV);

input CLK,RST,EN;//时钟,复位,输入使能

output [5:0] COUTS;//s输出

output [6:0] COUTMS;//ms输出

output OV; //计数进位输出

wire [5:0] Q1s;//reg OV;

wire [6:0] Q1ms;

wire COUT10ms;

wire COUT1s;

wire COUT60s;

assign COUTS = Q1s;//将内部寄存器的计数结果输出至COUTS

assign COUTMS = Q1ms;

assign OV = COUT60s;

//定时10ms模块例化

Timer10ms u_Timer10ms(

.CLK (CLK),

.RST (RST),

.EN (EN),

.COUT10ms (COUT10ms),

);

//定时1s模块例化

Timer1s u_Timer1s(

.CLK1ms (COUT10ms),

.RST (RST),

.EN (EN),

.COUT1s (COUT1s),

.CNTS (Q1ms),

);

//定时60s模块例化

Timer60sby1s u_Timer60sby1s(

.CLK1s (COUT1s),

.RST (RST),

.EN (EN),

.COUT60s (COUT60s),

.CNT60S (Q1s),

);

endmodule

60s定时器模块:需要1s定时器模块的支持

//----------------------------------------------------------------------------------------

// File name: Timer10ms

// Last modified Date: 2020年5月30日10点50分

// Last Version: V1.1

// Descriptions: 定时60s,本模块需基于1s定时模块的基础上进行

//----------------------------------------------------------------------------------------

module Timer60sby1s(CLK1s,RST,EN,COUT60s,CNT60S);

input CLK1s,EN,RST;//时钟,时钟使能,复位;EN == 1有效

output COUT60s; //计数进位输出

output [5:0] CNT60S;//计数值输出

reg [5:0] Q60s;reg COUT60s;

assign CNT60S = Q60s;

always @(posedge CLK1s or negedge RST) //时序过程

begin

if(!RST) Q60s <= 0; //RST=0时,对内部寄存器单元异步清0

else if (EN) //同步使能EN = 1;则允许计数

begin

if(Q60s < 60)

Q60s <= Q60s +1;//当Q1小于60时,允许累加

else

Q60s <= 6'b0; //否则一个时钟后清0返回初值

end

end

always @(Q60s) //组合逻辑

if (Q60s==6'd60)

COUT60s = 1'b1;

else

COUT60s = 1'b0;

endmodule

1s定时器模块:需要10ms定时器模块的支持

//----------------------------------------------------------------------------------------

// File name: Timer10ms

// Last modified Date: 2020年5月30日10点35分

// Last Version: V1.1

// Descriptions: 定时1s,本模块需基于10ms定时模块的基础上进行

//----------------------------------------------------------------------------------------

module Timer1s(CLK1ms,RST,EN,COUT1s,CNTS);

input CLK1ms,EN,RST;//时钟,时钟使能,复位;EN == 1有效

output COUT1s; //计数进位输出

output [6:0] CNTS; //计数器数值输出,单位:ms

reg [6:0] Q1s;reg COUT1s;

assign CNTS = Q1s;

always @(posedge CLK1ms or negedge RST) //时序过程

begin

if(!RST) Q1s <= 0; //RST=0时,对内部寄存器单元异步清0

else if (EN) //同步使能EN = 1;则允许计数

begin

if(Q1s < 100)

Q1s <= Q1s +1;//当Q1小于100时,允许累加

else

Q1s <= 7'b0; //否则一个时钟后清0返回初值

end

end

always @(Q1s) //组合逻辑

if (Q1s==7'd100)

COUT1s = 1'b1;

else

COUT1s = 1'b0;

endmodule

10ms定时器模块:

//----------------------------------------------------------------------------------------

// File name: Timer10ms

// Last modified Date: 2020年5月30日10点20分

// Last Version: V1.1

// Descriptions: 定时10ms

//----------------------------------------------------------------------------------------

module Timer10ms(CLK,RST,EN,COUT10ms);

input CLK,EN,RST;//时钟,时钟使能,复位;EN == 1有效

output COUT10ms; //计数进位输出

reg [18:0] Q10ms;reg COUT10ms;

always @(posedge CLK or negedge RST) //时序过程

begin

if(!RST) Q10ms <= 0; //RST=0时,对内部寄存器单元异步清0

else if (EN) //同步使能EN = 1;则允许计数

begin

if(Q10ms < 500000)

Q10ms <= Q10ms +1;//当Q10ms小于500000时,允许累加

else

Q10ms <= 19'b0; //否则一个时钟后清0返回初值

end

end

always @(Q10ms) //组合逻辑

if (Q10ms==19'd500000)

COUT10ms = 1'b1;

else

COUT10ms= 1'b0;

endmodule

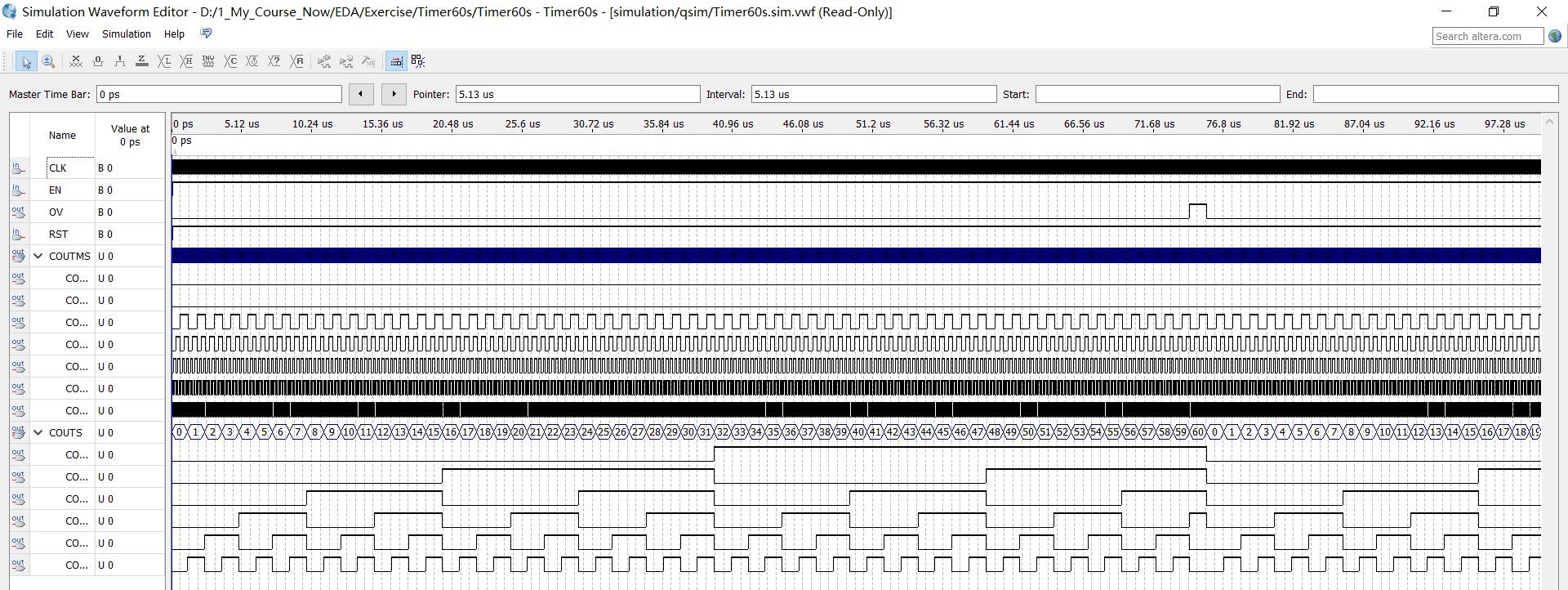

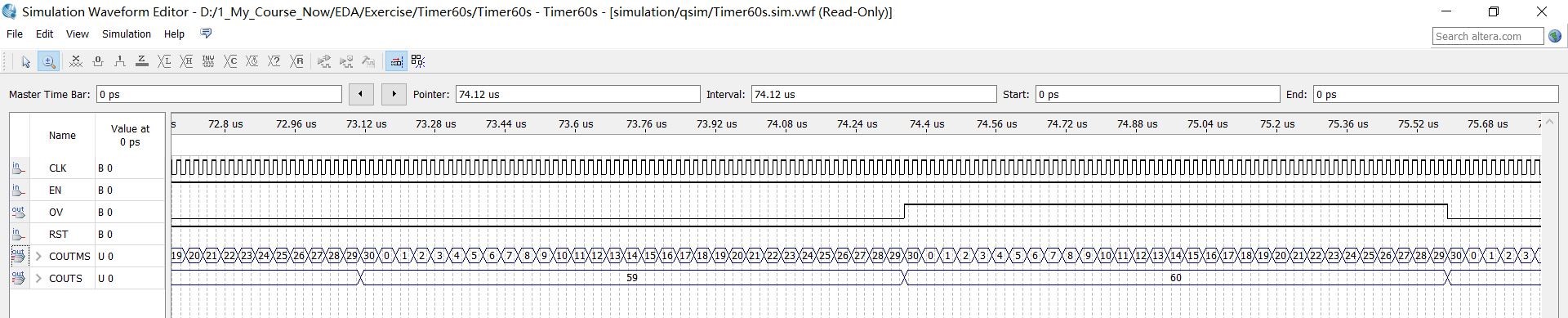

三、仿真波形图

最后

以上就是义气黑夜最近收集整理的关于FPGA _Verilog HDL_计数器实现数字钟60秒计数设计实验一、题目二、源代码三、仿真波形图的全部内容,更多相关FPGA内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[SystemVerilog] 基于 FPGA 的数字钟设计](https://www.shuijiaxian.com/files_image/reation/bcimg21.png)

发表评论 取消回复