数字跑表的FPGA设计

目录

〇、设计要求

一、数字跑表计时模块的设计

二、数码管显示设计

三、按键扫描和消抖模块

四、综合设计

〇、设计要求

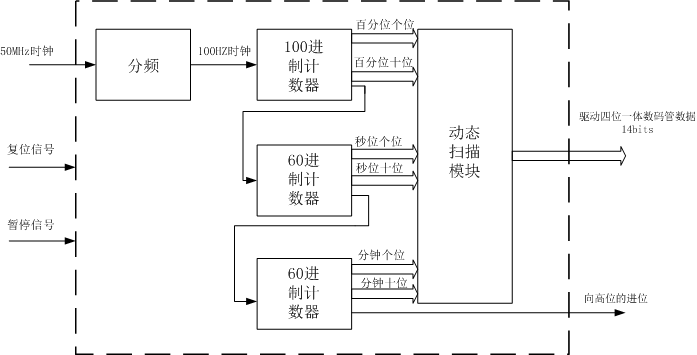

1、整体设计框图如下。实现具备下诉功能需求的跑表。由数码管显示百分秒、秒、分等计时。

2、任务分析

输入端口:

1)复位信号CLR,当CLR=1,输出全部置0,当CLR=0,系统正常工作。

2)暂停信号PAUSE,当PAUSE=1,暂停计数,当PAUSE=0,正常计数。

3)系统时钟CLK50M,CLK=50MHz。

输出端口:

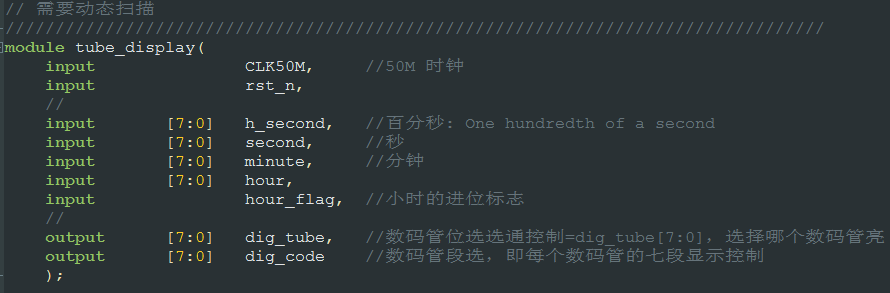

数码管位选选通控制,选择哪个数码管亮——dig_tube,位宽8位,依次控制8个数码管。

数码管段选,即每个数码管的七段显示控制——dig_code,位宽8位,数码管显示值。

一、数字跑表计时模块的设计

1、RTL设计

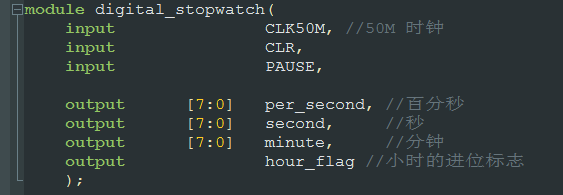

源程序为 digital_stopwatch.v

顶层端口:

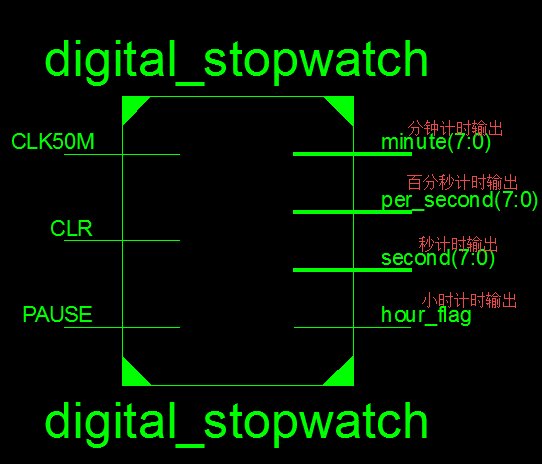

综合后的顶层框图如下:设计要求按照PPT所述。

2、仿真

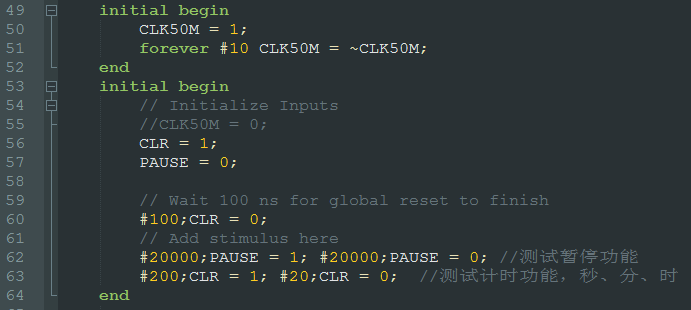

仿真文件为 test_digital_stopwatch.v

示例测试代码如下:

测试结果如下。

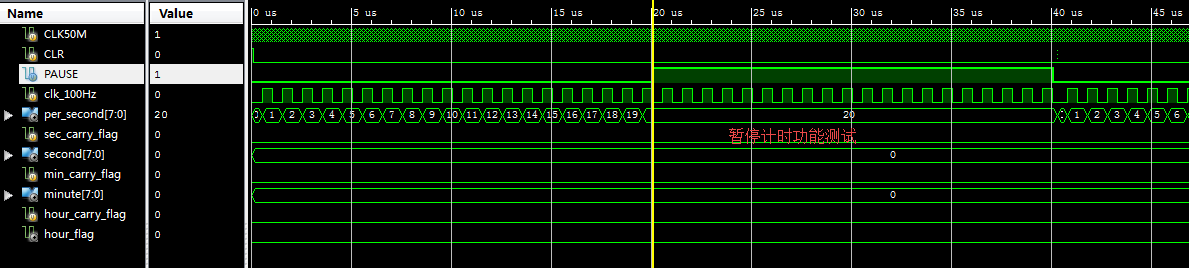

暂停仿真测试:

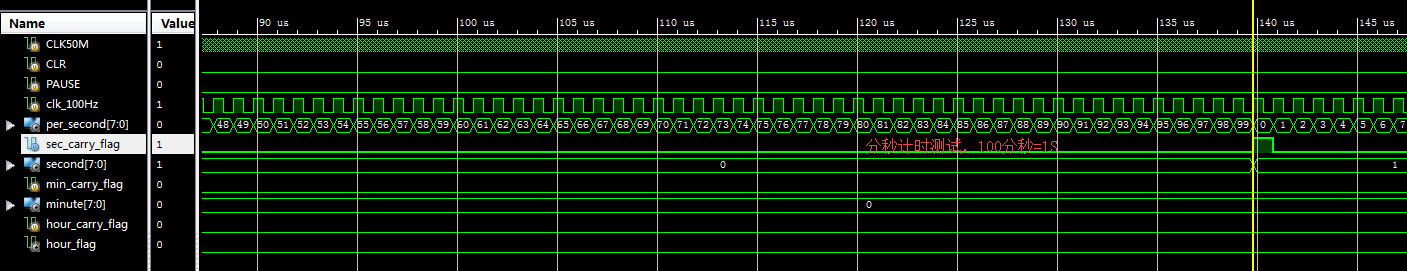

分秒计时测试:

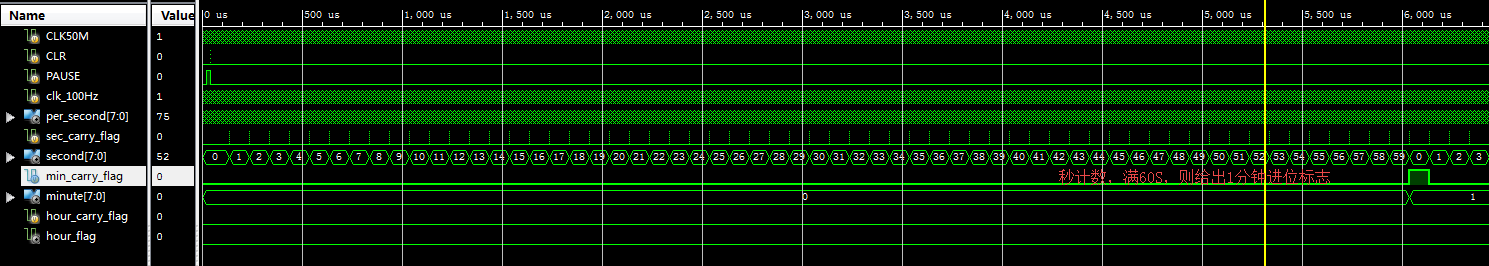

秒计时仿真:

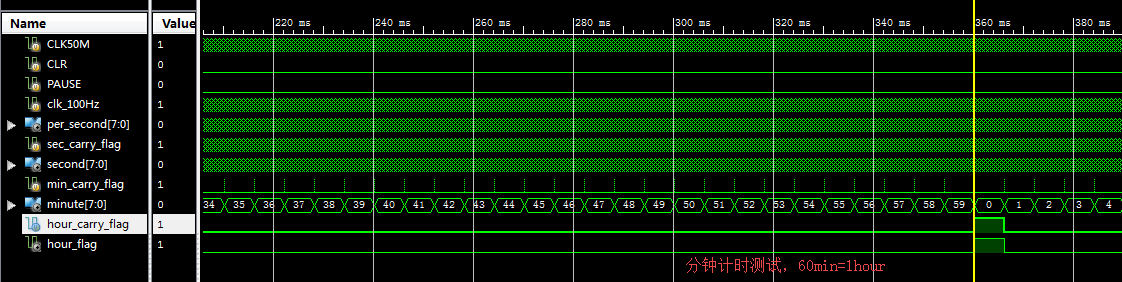

分钟计时仿真:

3、总结

设计通过50MHz的输入时钟,分频得到100Hz的慢速时钟,实现分秒计数。并通过对进位标志的求和,实现秒、分、时的计时。

设计实现了CLR异步重置、PAUSE暂定计时,并输出相应的时进位标志,分、秒、分秒计数值。

注意:上述代码中,只实现了秒表的计数,分秒计时、秒计时、分计时、和小时进位标志,并具备复位和暂停功能。但是数码管部分的代码,没有实现,还需要添加。

二、数码管显示设计

一共有8个数码管,依次控制 百分秒、秒、分钟、小时的显示。

分析:以1ms 的频率扫描输出行数据给8个数码管,所以完成8个数码管的依次输出显示的总时间为8ms。程序把计数程序时间计时的各个数据位数字赋给个位数码管,十位数字赋给十位数码管,依次完成8个数码管的赋值。

1、顶层接口如下。

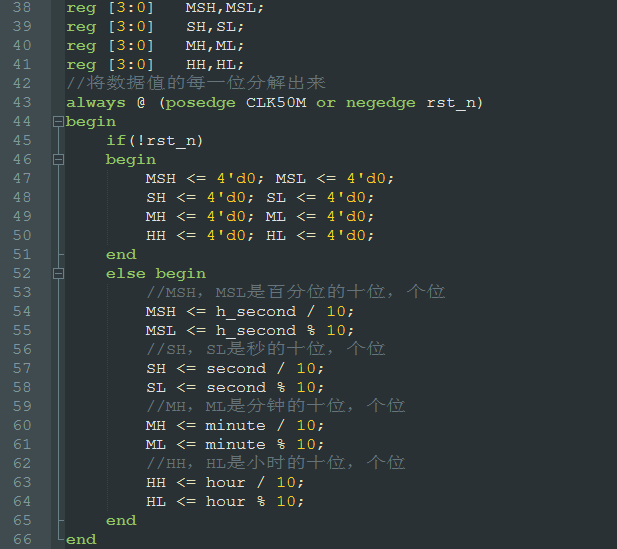

2、代码介绍

将计时时间数值的个位和十位分解出来。

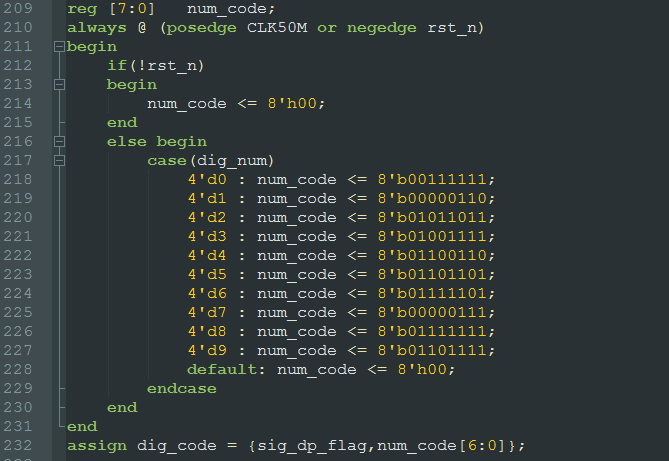

每个数码管的段选编码0~9。

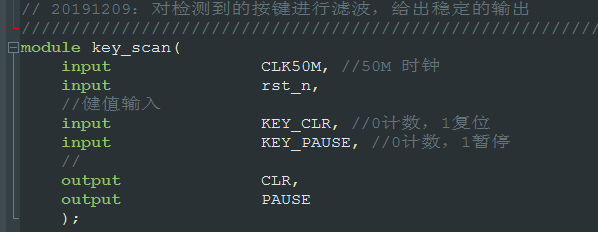

三、按键扫描和消抖模块

顶层如下,实现赞同和复位按键的检测和滤波。

采样按键值,20ms扫描一次,采样频率小于按键毛刺频率,相当于滤除掉了高频毛刺信号

四、综合设计

综合后的顶层,添加好UCF文件后,下载测试。

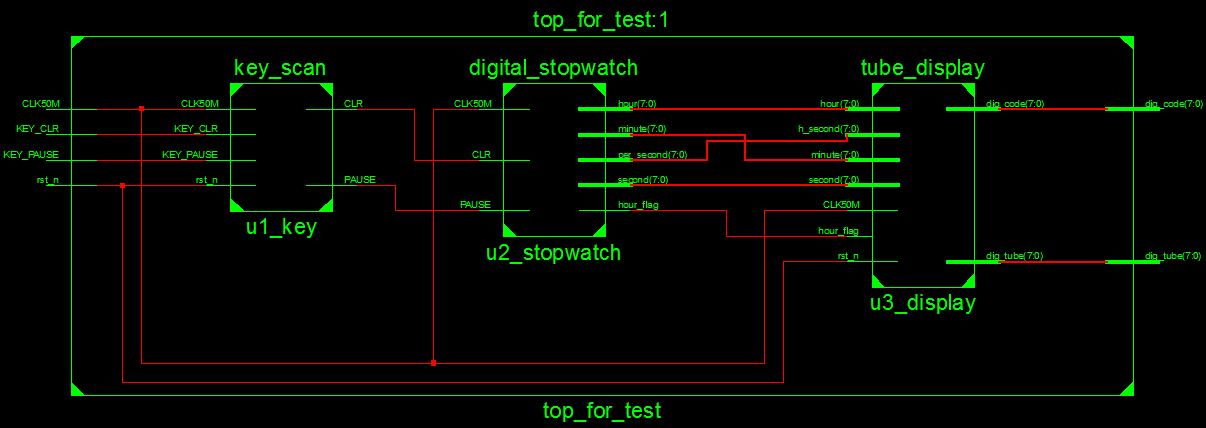

其RTL原理图。

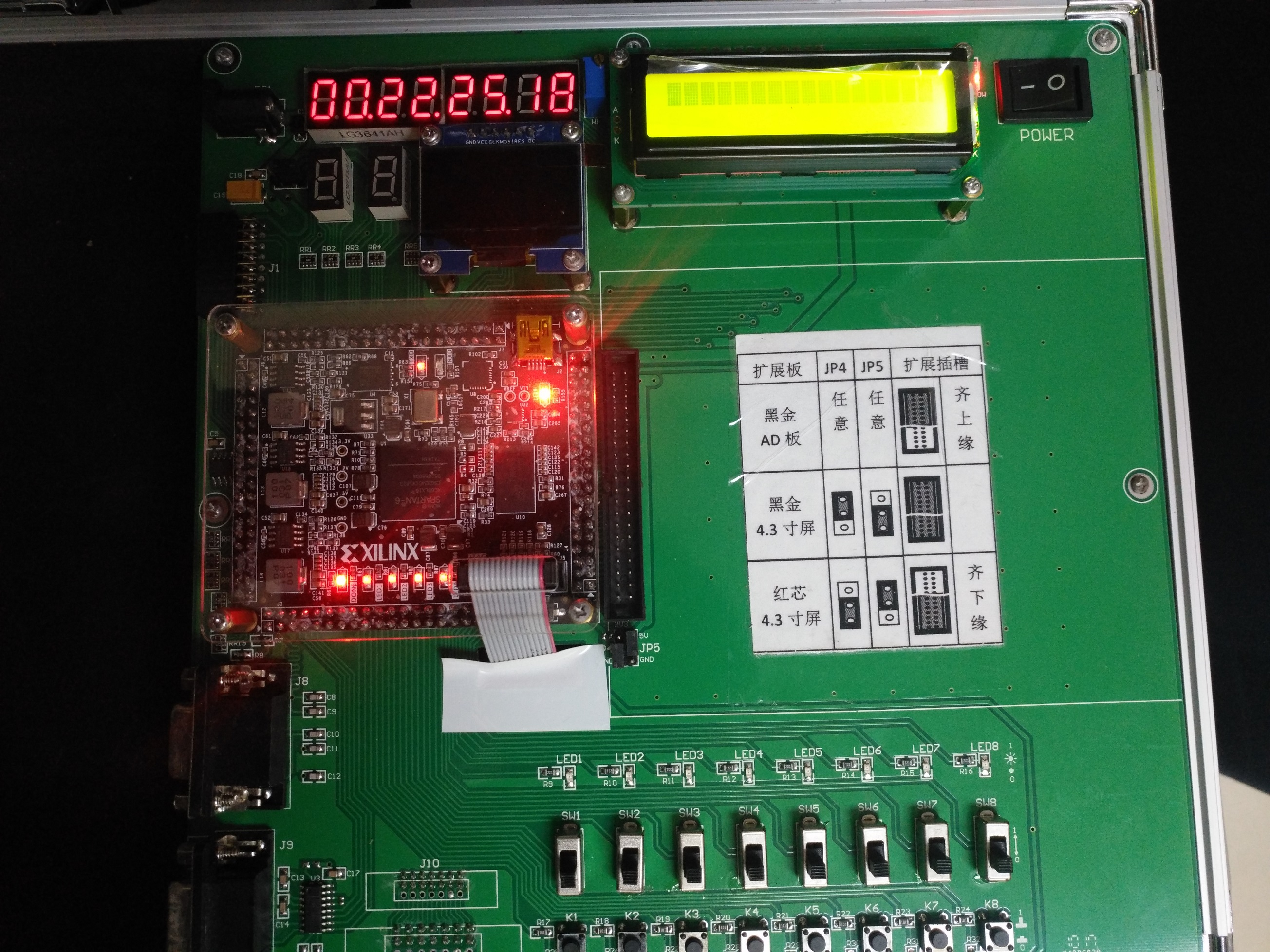

测试如下,暂停、复位、计数功能均正常。设计完成。当前测试时间为22min,25秒,18百分秒。

最后

以上就是冷艳诺言最近收集整理的关于基于FPGA的数字跑表设计的全部内容,更多相关基于FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复