我是靠谱客的博主 老实外套,这篇文章主要介绍EDA数字钟设计(verilog)——开关功能和总体接线图及模块改进1.开关功能如思维导图所示2.总体接线图:3.问题及改进,现在分享给大家,希望可以做个参考。

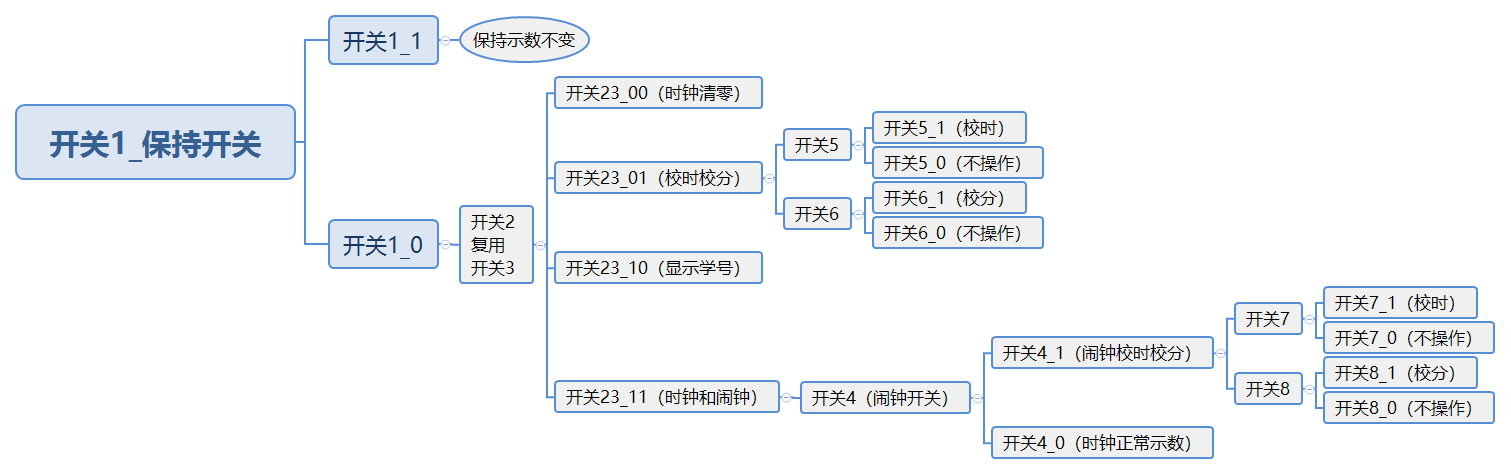

1.开关功能如思维导图所示

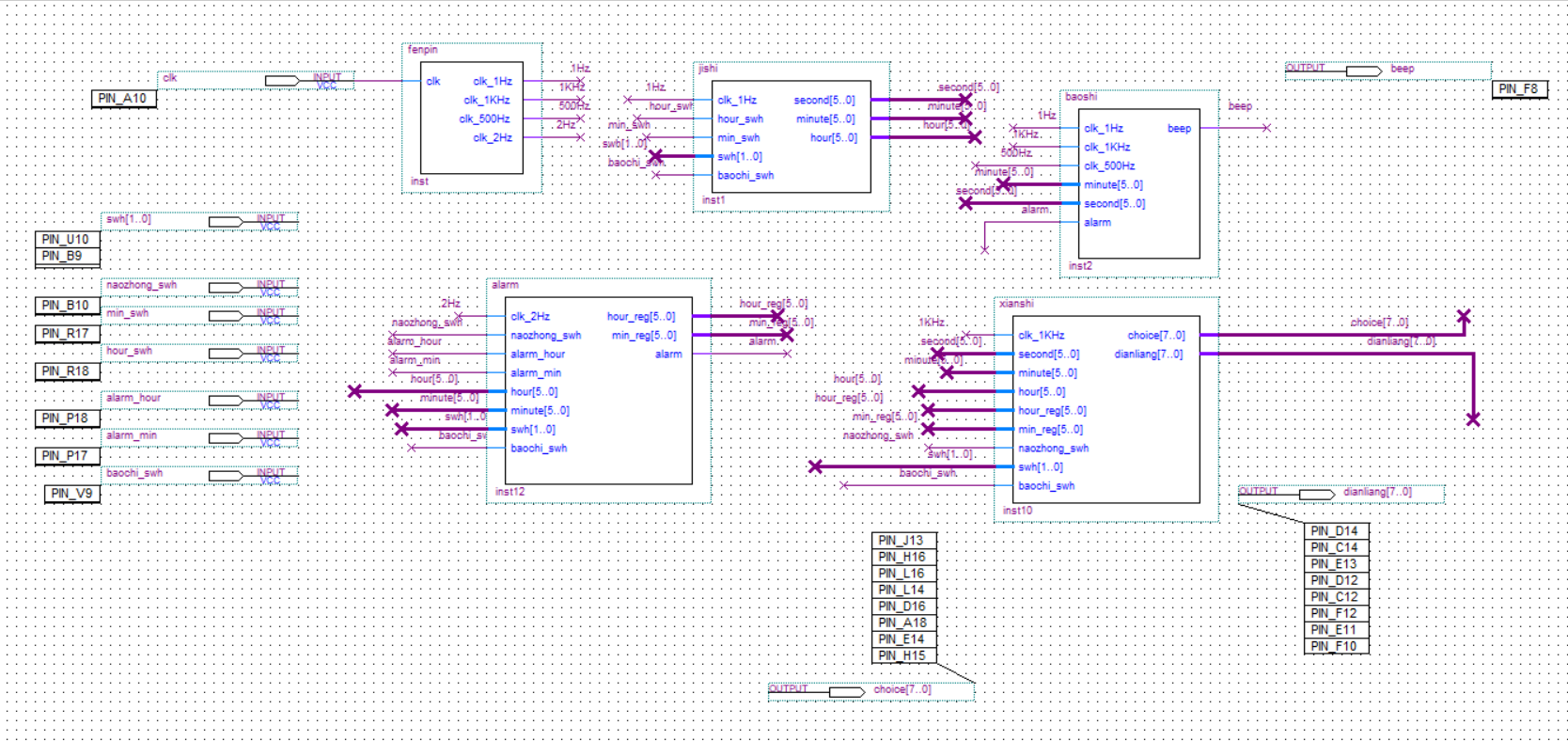

2.总体接线图:

3.问题及改进

学号显示后正常计数是从学号开始计数下面对程序进行改进,主要是在计时模块中删除显示学号的内容,把显示学号部分转移到显示模块中,让显示时根据条件显示内容,而不是直接显示示数:

-

计时模块

module jishi(clk_1Hz,second,minute,hour,hour_swh,min_swh,swh,baochi_swh);

input clk_1Hz;

input hour_swh,min_swh,baochi_swh;

input [1:0]swh;

output reg[5:0]second,minute,hour;

reg [11:0]hs; //3600秒小时加1

always@(posedge clk_1Hz)

begin

if((swh[1:0] == 'b00)&&(!baochi_swh)) //清零

begin

second <= 0;

minute <= 0;

hour <= 0;

end

else if(baochi_swh) //使能

begin

second <= second;

minute <= minute;

hour <= hour;

end

else if((swh[1:0] == 'b11)&&(!baochi_swh)) //正常示数

begin

if(second < 'd59)

begin

second <= second + 'd1;

hs <= hs + 'd1;

end

else

begin

second <= 'd0;

hs <= hs + 'd1;

if(minute < 'd59)

minute <= minute + 'd1;

else

minute <= 'd0;

if(hs < 'd3599 && hour < 'd23)

hour <= hour + 'd1;

else if((hs == 'd3599)&&(hour == 'd23))

begin

hour <= 'd0;

hs <= 'd0;

end

end

end

else if(((swh[1:0] == 'b01)&&(!baochi_swh))||(swh[1:0] == 'b10)) //校时校分

begin

if((hour_swh)&&(swh[1:0] == 'b01))

begin

if(hour == 'd23)

hour <= 'd0;

else

hour <= hour + 'd1;

end

if((min_swh)&&(swh[1:0] == 'b01))

begin

if(minute == 'd59)

minute <= 'd0;

else

minute <= minute + 'd1;

end

end

end

endmodule

-

显示模块

module xianshi(clk_1KHz,second,minute,hour,choice,dianliang,hour_reg,min_reg,naozhong_swh,swh,baochi_swh,baochi);

input [5:0]second,minute,hour;

input [5:0]hour_reg,min_reg;

input clk_1KHz;

input naozhong_swh,baochi_swh,baochi;

input [1:0]swh;

reg [3:0]sec_ge,sec_shi,hour_ge,hour_shi,min_ge,min_shi;

reg [3:0]scan;

reg [7:0]data;

output reg[7:0]choice;

output reg[7:0]dianliang;

always@(posedge clk_1KHz) //扫描电路

begin

if(scan == 'b111)

scan <= 'b000;

else

scan <= scan + 'd1;

end

always@(clk_1KHz) //时分秒个位十位提取

begin

if((naozhong_swh)&&(swh[1:0] == 'b11)&&(!baochi_swh))

begin

min_ge <= min_reg%10;

min_shi <= min_reg/10;

hour_ge <= hour_reg%10;

hour_shi <= hour_reg/10;

sec_ge <= 'd0;

sec_shi <= 'd0;

case(scan)

'b000:

begin

choice <= 'b11111110;

data <= sec_ge;

end

'b001:

begin

choice <= 'b11111101;

data <= sec_shi;

end

'b010:

begin

choice <= 'b11111011;

data <= 'd10;

end

'b011:

begin

choice <= 'b11110111;

data <= min_ge;

end

'b100:

begin

choice <= 'b11101111;

data <= min_shi;

end

'b101:

begin

choice <= 'b11011111;

data <= 'd10;

end

'b110:

begin

choice <= 'b10111111;

data <= hour_ge;

end

'b111:

begin

choice <= 'b01111111;

data <= hour_shi;

end

default:

begin

choice <= 'b00000000;

data <= 'd5;

end

endcase

end

else if((!baochi)&&(swh[1:0] == 'b10)) //显示学号

begin

sec_ge <= 'd6;

sec_shi <= 'd3;

min_ge <= 'd7;

min_shi <= 'd0;

hour_ge <= 'd0;

hour_shi <= 'd0;

case(scan)

'b000:

begin

choice <= 'b11111110;

data <= sec_ge;

end

'b001:

begin

choice <= 'b11111101;

data <= sec_shi;

end

'b010:

begin

choice <= 'b11111011;

data <= 'd10;

end

'b011:

begin

choice <= 'b11110111;

data <= min_ge;

end

'b100:

begin

choice <= 'b11101111;

data <= min_shi;

end

'b101:

begin

choice <= 'b11011111;

data <= 'd10;

end

'b110:

begin

choice <= 'b10111111;

data <= hour_ge;

end

'b111:

begin

choice <= 'b01111111;

data <= hour_shi;

end

default:

begin

choice <= 'b00000000;

data <= 'd0;

end

endcase

end

else

begin

sec_ge <= second%10;

sec_shi <= second/10;

min_ge <= minute%10;

min_shi <= minute/10;

hour_ge <= hour%10;

hour_shi <= hour/10;

case(scan)

'b000:

begin

choice <= 'b11111110;

data <= sec_ge;

end

'b001:

begin

choice <= 'b11111101;

data <= sec_shi;

end

'b010:

begin

choice <= 'b11111011;

data <= 'd10;

end

'b011:

begin

choice <= 'b11110111;

data <= min_ge;

end

'b100:

begin

choice <= 'b11101111;

data <= min_shi;

end

'b101:

begin

choice <= 'b11011111;

data <= 'd10;

end

'b110:

begin

choice <= 'b10111111;

data <= hour_ge;

end

'b111:

begin

choice <= 'b01111111;

data <= hour_shi;

end

default:

begin

choice <= 'b00000000;

data <= 'd0;

end

endcase

end

case(data)

'd0:dianliang = 'hc0;

'd1:dianliang = 'hf9;

'd2:dianliang = 'ha4;

'd3:dianliang = 'hb0;

'd4:dianliang = 'h99;

'd5:dianliang = 'h92;

'd6:dianliang = 'h82;

'd7:dianliang = 'hf8;

'd8:dianliang = 'h80;

'd9:dianliang = 'h90;

'd10:dianliang = 'hbf;

endcase

end

endmodule

最后

以上就是老实外套最近收集整理的关于EDA数字钟设计(verilog)——开关功能和总体接线图及模块改进1.开关功能如思维导图所示2.总体接线图:3.问题及改进的全部内容,更多相关EDA数字钟设计(verilog)——开关功能和总体接线图及模块改进1内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![eda多功能数字钟课程设计_EDA电子钟多功能数字时钟课程设计(含代码)[优秀]...](https://www.shuijiaxian.com/files_image/reation/bcimg3.png)

发表评论 取消回复