报时模块进行闹钟的响铃还有整点报时功能,分别在59’53’’、59’55’’和59’57’’进行低频蜂鸣器的声音,59’59’’进行高频蜂鸣器的声音,在闹钟信号来临时用500Hz让蜂鸣器连续蜂鸣,同时输出beep蜂鸣信号。

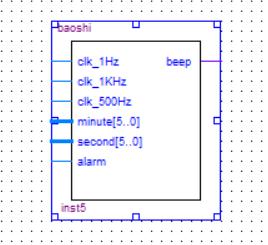

module baoshi(clk_1Hz,clk_1KHz,clk_500Hz,minute,second,beep,alarm);

input [5:0]minute,second;

input clk_1KHz,clk_500Hz,clk_1Hz;

input alarm; //闹钟信号

output reg beep;

always@(clk_1Hz)

begin

if(alarm)

begin

beep <= clk_500Hz;

end

else if(minute == 'd59)

begin

if(second == 'd53 || second == 'd55 || second == 'd57)

beep <= clk_500Hz;

else if(second == 'd59)

beep <= clk_1KHz;

else

beep <= 'd0;

end

else

begin

beep <= 'd0;

end

end

endmodule

封装图如下:

最后

以上就是动人路灯最近收集整理的关于EDA数字钟设计(verilog)——报时模块的全部内容,更多相关EDA数字钟设计(verilog)——报时模块内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复