文章目录

- 1. 任务要求

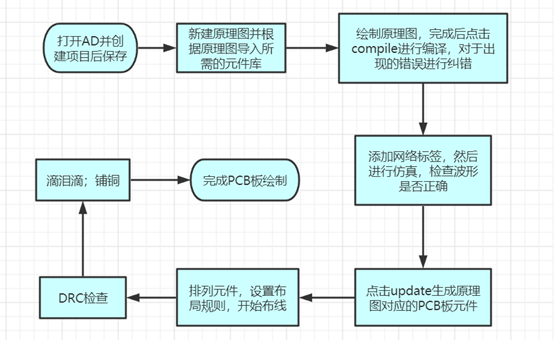

- 2. 使用AD的步骤简述

- 3. SCH绘制

- 4. 仿真及结果

- 5. PCB 绘制

- 6. DRC 检查

- 7.后记

- 8.完整实验报告

1. 任务要求

规定题目1:“典型差放与带恒流源差放” 模拟仿真

具体要求:

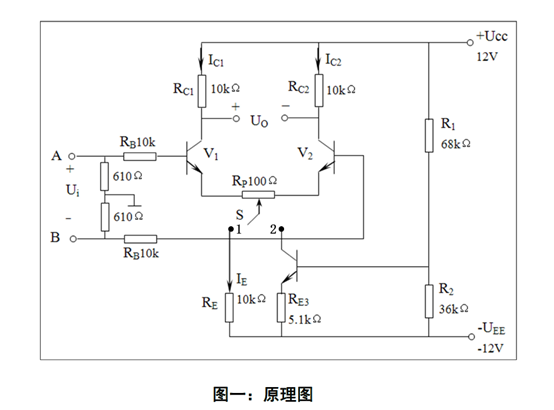

- 原理图如图:

- 典型差放与带恒流源差放分别仿真

- 分别仿真各自的差模增益、共模增益;并列表比较,并分析性能不同的

原因。

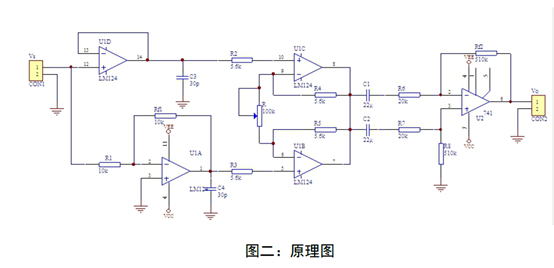

规定题目2:“测量放大电路” 模拟仿真

具体要求:

- 原理图如图1。图1 中的元件封装方式可以按表格中所列的直插式的,鼓励大家把封装改为贴片(SMD)。

- 完成“测量放大电路”的电路模拟仿真(工作点分析、瞬态分析和小信

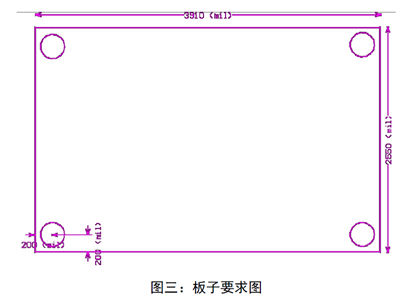

号分析) - 设计一块双面PCB 板,机械尺寸见图2

- 要在这块PCB 板的TopOverlay 层放上你的学号。学号的位置到PCB 板的

左边的距离是你的学号的最后两位乘以10。例如你的学号后两位是22,

则字符的位置到左边的距离是220mil。 - 这块PCB 中,要求网络标号VCC、VEE 线的宽度为25mil,与其他线和地

的间距不小于50mil。其他线宽没有要求,但线间距不小于10mil。地线

应尽量宽,并铺铜。 - PCB 板的机械结构要求(图2)

a) 板子为长方形,长3910mil,高2550mil

b) 四周有4 个上螺丝的孔,圆心到两个相邻边的距离都是200mil,圆的直径138mil,但打孔的孔径为120mil,宽出来的18mil 是考虑螺丝的头比较大,所以布线时不能进入这个圆内,也不能在圆内放元件。

c) 由于加工和安装需要,长方形的每个边周围留出50mil 禁止布线和放元件。例如底边向上有50mil 不能布线,左边的边的右边50mil 范围内不能布线和放元件。

2. 使用AD的步骤简述

3. SCH绘制

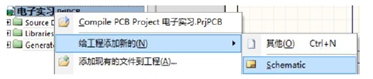

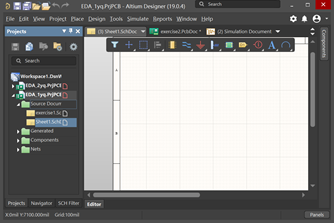

3.1 进入SCH

通过project 创建原理图Schematic 进入原理图。

创建完毕进入schematic 界面。

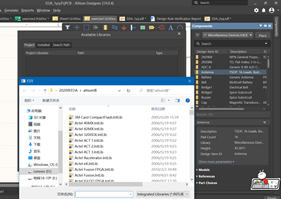

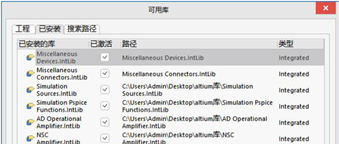

3.2 加载SCH 库

添加器件所在的库的操作。

3.3 添加元器件

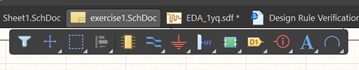

找到工具栏中添加元器件的标志,红色下划线标志即为放置器件标志。

根据任务书原理图放置所需要的器件,添置部分器件。

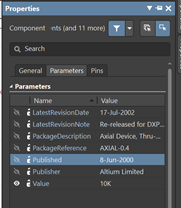

3.4 修改元器件属性

通过双击元件来修改其内部属性,观察有无封装可否仿真等,如图3.4.1 所示,value 代表器件的数值大小。

3.5 元器件连接

通过工具栏中的导线标识来实现器件之间的电气连接,,红色下划线标志即为放置器件标志。

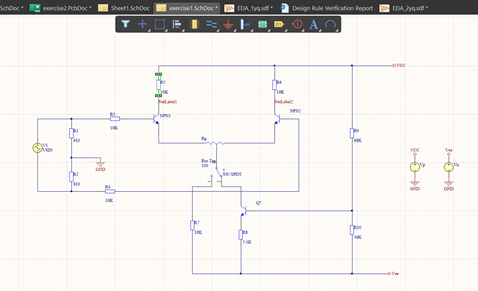

按照任务书提供的放大电路原理图,

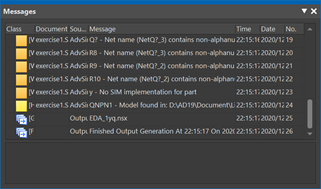

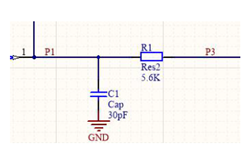

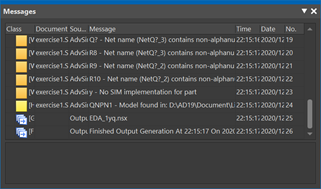

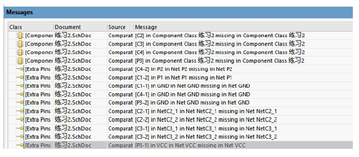

编译结果如下图3.5.3 所示。

3. 6 放置网络标号

网络标号的标志,红色下划线标志即为网络标号标志。在需要观察的地方加上标签,这里例举一下标签P1 和P3,

3.7 编译

完成了原理图的绘制,应该对原理图进行编译来检查是否存在电气连接等规则错误,

观察Message 中的情况,一般情况下warning 不影响后续的进行,若对后续的仿真造成影响,可以对其进行修改,通过改变器件每一个端口的输入输出情况进行修改。

4. 仿真及结果

4.1“差动放大电路”模拟仿真及结果

4.11仿真

外加激励源,将电压等参数进行相应修改;对四种情况的原理图进行编译;编译无误以后进行仿真。

4.12结果

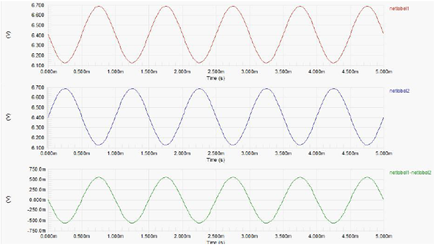

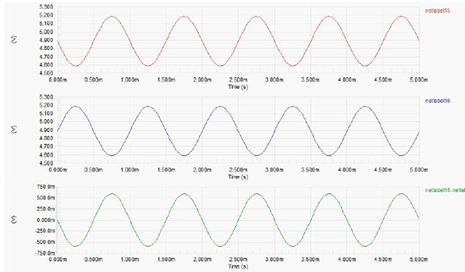

典型差动放大电路—差模

典型差动放大电路—共模

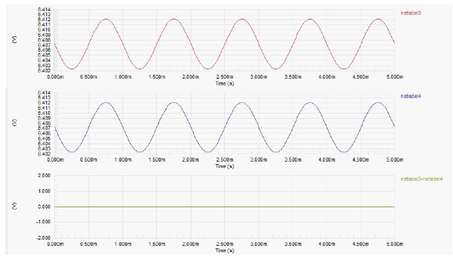

带恒流源的差动放大电路—差模

带恒流源的差动放大电路—共模

4.13结果分析

仿真波形分析:

共模信号:两个大小相等、极性相同的信号称为共模信号,把共模信号到

差动放大电路的输入端称为共模输入。

差模信号:两个大小相等、极性相反的信号称为差模信号,把差模信号加到

差动放大电路的输入端称为差模输入。

由于这是完全对称的差动放大电路,当差模输入时,两个输出端的波形是对称的,并存在电压差,此时达到了放大的效果;而共模输入时,两个输出端的波形一致,不存在电压差,此时电压的共模放大倍数为0。

通过比较典型差动放大电路和带恒流源的差动放大电路的仿真结果,我们可

以得到:两者都放大差模信号,抑制共模信号,而最主要的区别就是前者的单端

输出和双端输出均远小于后者。在这里我们需要特别注意仿真图上面的单位。

典型和带恒流源的差动放大电路分析:

当温度发生变化时,两个三极管的集电极电流、集电极电位都将发生变化,但是由于两管的参数完全一致,所以两边集电极电流、电位的变化量相同,这说明完全对称的差动放大电路对两管所产生的同向漂移具有抑制作用,即在理想的情况下能够使漂移为0,但是温度的变化仍然会导致漂移,当发射极电阻Re 越大,抑制零漂的作用越显著。而经过实验分析可以知道,差动放大电路既能抑制零漂,又有较高的电压放大倍数,是一个比较高效益的放大电路。一个实际的差动放大电路,对差模信号和共模信号都具有放大作用,但是要求电路的差模放大倍数越大越好,而共模的放大倍数越小越好。通常采用共模抑制比来描述差动放大电路差模信号和抑制共模信号的能力(差模放大倍数/共模放大倍数),即共模抑制比的值越大越好。要想提高差动放大电路的共模抑制比,就要增大共模负馈电阻Re,但增大Re 会使其直流压降增大,要保持合适的静态工作点,VEE 就要增大很多,这显然是不经济的。恒流源电路具有输出电阻很高而直流压降较小的特点,若用恒流源电路代替电路中的Re,就可在VEE不高的情况下,获得很高的共模抑制比。

4.2“测量放大电路”模拟仿真及结果

4.21仿真

在可仿真电路基础上添加激励源;添加网络编号;编译、仿真;

4.22仿真结果

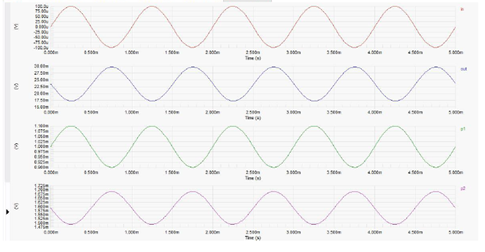

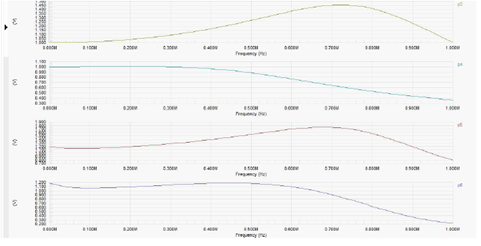

瞬态分析

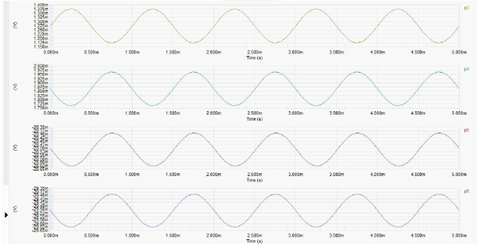

小信号分析

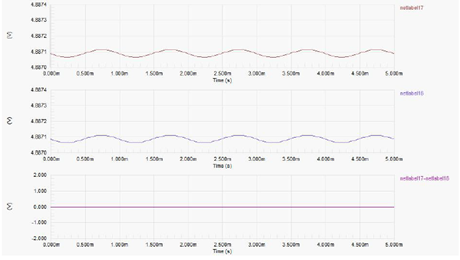

静态工作点:

4.23结果分析

LM124 是四运放集成电路,它的内部包含四组形式完全相同的运算放大器,

除电源共用外,四组运放相互独立。两个信号输入端中,Vi-(-)为反相输入端,

表示运放输出端Vo 的信号与该输入端的相位相反;Vi+(+)为同相输入端,表

示运放输出端Vo 的信号与该输入端的相位相同。

对瞬态进行分析:瞬态分析是用于析仿真电路工作点信号随时间变化的情

况。可以通过对激励源的属性设定来进行不同的仿真。输入信号是从Vi+(+)

端口输入即U1D,所以输出端口得到的Vo 应该与Vi+(+)同相。相反输入信号从Vi-(-)输入即U1A,所以输出端口得到的Vo 应该与Vi-(-)反向。同时因为在进入下一个比较器时,电路状态处于虚短路,是的R2 与R3 上均没有分压,得到的结果应是P1 与P3 相同,P2 与P4 相同。U1B,U1C 中的比较器可以作为减法器得到新的信号P5,P6。经过LM741,LM741 是单运放的高增益运算放大器,得到放大后的信号OUT。由该图可以计算得到一个近似的额放大倍数,这里需要注意单位的不一样。从输入端信号IN 到输出端信号OUT总体放大倍数约为65%。

小信号分析是在频域响应方面显示系统的性能,通过设置交流信号分析的频

率范围,系统将显示该频率范围内的增益。在进行小信号分析时,Start Frequency参数用于设置进行交流小信号分析的起始频率。Stop Frequency 参数用于设置进行交流小信号分析的终止频率。Sweep 参数用于设置交流小信号分析的频率扫描方。从图中我们可以看出,in 输入端的交流电压一直是1V,out 端输出的电压会随着频率的增加,电压会逐渐下降。P1 端在725KHZ 的时候,其输出的电压值达到最大,P2 端在0.3M 之前电压值几乎不变,在0.3M 之后电压值随频率的增加而下降。P3-P6 的电压值,随频率的增加,电压值上下波动的不同。

静态工作点分析通常是用于对放大电路进行分析,当放大器的输入信号为零

状态时,电路中的各点(P1-P6 以及OUT 各点)状态就是电路的静态工作点。

5. PCB 绘制

5.1 创建PCB

⑴建立PCB 文件并保存,

⑵安装标准PCB 封装库和自定义元件封装库

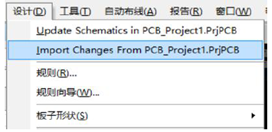

5.2 加载网络表

加载网络表,如果有错返回原理图修改

5.3 调出元件

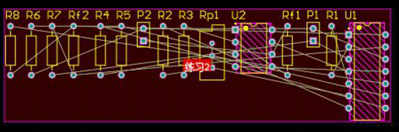

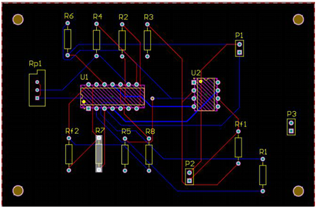

元件调出后,各元件之间由飞线进行连接,飞线只代表元件之间的连接关系,

不会存在于PCB 中。

5.4 排列原件

按照一定的原则排列元件并规划电路板的大小,如下图5.4.1 所示

图5.4.1

5.5 布线

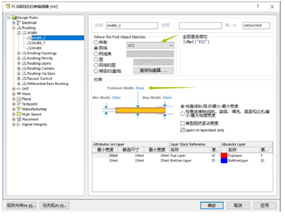

设定PCB 布线规则,根据要求VCC,VEE 设定宽度为20mil,其他线间间距不小于10mil。添加新的规则width_1 保证VEE 宽度为20mil,如图5.5.1 所示。width_2 保证VCC 宽度为20mil。width 使其他线的宽度首选为10mil,最细为10mil,最宽10mil。

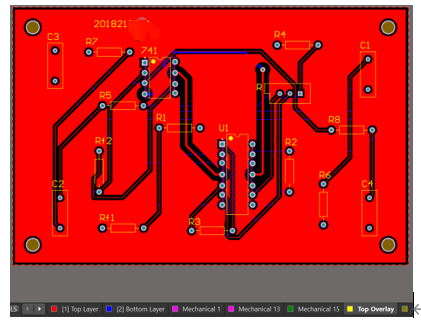

开始自动布线并打孔,再手动修改有问题的线

设置完毕,布线前进行规则检查

图5.5.3

布线完毕,再于top Overlay 层放置自己的学号,按要求学号距离左侧边界

学号尾数两位10mil 的距离,我的学号是201821**33,因此应该间隔330mil。

5. 6 铺铜

根据要求采用solid 实心敷铜进行普通设计,因为采用的是双面板,所以要对top layer 以及bottom layer 进行铺铜

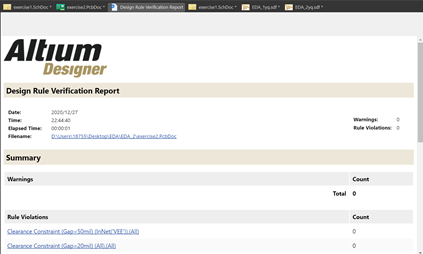

6. DRC 检查

在工具中找到设计规则检测,点击。

7.后记

1.此项目的源文件我已上传至百度网盘:

提取码:eony

压缩包内有两个文件夹,分别对应第一题和第二题。

EDA_1中分别为四个电路的源仿真图;

EDA_2中有一个电路的源仿真图,本人制作的PCB板虽可以通过验收但有较多瑕疵,故并未放出;

如何将这些源仿真图导入到工程内请自己尝试,做个实验不能这个都不会吧~

8.完整实验报告

https://download.csdn.net/download/qq_44977889/18966565

既来之~

则赞之~

若有疑问~

创所欲言~

最后

以上就是爱笑心情最近收集整理的关于EDA 课程设计 实验报告及源文件1. 任务要求2. 使用AD的步骤简述3. SCH绘制4. 仿真及结果5. PCB 绘制6. DRC 检查7.后记的全部内容,更多相关EDA内容请搜索靠谱客的其他文章。

![eda多功能数字钟课程设计_EDA电子钟多功能数字时钟课程设计(含代码)[优秀]...](https://www.shuijiaxian.com/files_image/reation/bcimg3.png)

发表评论 取消回复