文章目录

- 前言

- 一、由移位寄存器构成

- 二、由移位寄存器和组合逻辑电路构成

- 三、由计数器构成

前言

在数字电路中, 序列信号是指在同步脉冲作用下循环地产生一串周期性的二进制信号.能产生这种信号的逻辑器件就称为序列信号发生器。

序列信号发生器是数字电路系统中常用的功能单元,按照序列训话长度M和触发器数目n的关系可分为三种:

(1)最大循环长度序列码,M=2^n;

(2)最大线性序列码(m序列码),M=(2^n)-1。

(3)任意循环长度序列码,M<2^n。

序列信号发生器是能够产生一组或多组的序列信号的时序电路,他可以有纯时序电路构成,也可以有包含时序和组合逻辑的混合电路构成。

下面介绍三种设计思路,以产生100111序列的信号发生器为例。

一、由移位寄存器构成

单纯使用移位寄存器的序列信号发生器,由于输入输出之间没有组合电路,不需要组合逻辑反馈运算,因此电路工作频率高,但问题在于移位寄存器的长度取决于序列长度,占用电路面积大。

代码如下(示例):

module signal_maker1(out,clk, load, D);

parameter M=6;

output out;

input clk,load;

input [M-1:0] D;

reg [M-1:0] Q;

initial Q=6'b100111;

always @(posedge clk)

if(load)

Q<=D;

else

Q<={Q[M-2:0],Q[M-1]};

assign out=Q[M];

endmodule

二、由移位寄存器和组合逻辑电路构成

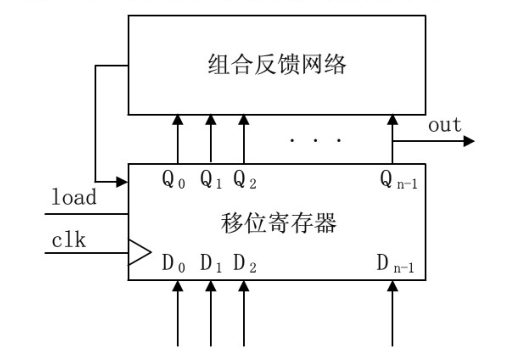

反馈移位型序列码发生器的结构框图如下图所示,它由移位寄存器和组合逻辑网络组成,从移位寄存器的某一输出端可以得到周期性的序列码。

其设计按以下步骤进行:

(1)根据给定序列信号的循环周期M,确定移位寄存器位数n,2^(n-1)<M≤2^n

(2)确定移位寄存器的M个独立状态。将给定的序列码按照移位规律每n位一组,划分为M个状态。若M个状态中出现重复现象,则应增加移位寄存器位数。用n+1位再重复上述过程,直到划分为M个独立状态为止.

(3)根据M个不同的状态列出移位寄存器的态序表和反馈函数表,求出反馈函数F的表达式。

(4)检查自启动性能。

与上面的序列信号发生器相比,各个寄存器的输出需要经过反馈网络,然后才连接到移位寄存器的输入端。因此,电路的速度必然下降,但反馈网络的好处在于它可以节省寄存器。

对于“100111”序列的信号发生器。

首先,确定所需移位寄存器的个数n。因M=6,故n≥3。

然后,确定移位寄存器的六个独立状态。

按照规律每三位一组,划分六个状态为100、001、011、111、111、110。

其中状态111重复出现,故取n=4,并重新划分状态,得到:1001、0011、0111、1111、1110、1100。因此确定n=4。

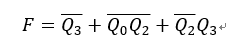

第三,列态序表和反馈激励函数表,求反馈函数F的表达式。

首先列出态序表,然后根据每一状态所需要的移位输入即反馈输入信号,列出反馈激励函数表,如下表所示。求得反馈激励函数:

代码如下(示例):

module signal_maker(out,clk, load, D);

parameter M=4;

output out;

input clk,load;

input [M-1:0] D;

reg[M-1:0] Q;

wire w1;

always @(posedge clk)

if(load)

Q<=D;

else

Q<={Q[M-2:0],w1};

assign w1=(~Q[3])|((~Q[1])&(~Q[0]))|(~Q[3]&(~Q[2]));

assign out=Q[M-1];

endmodule

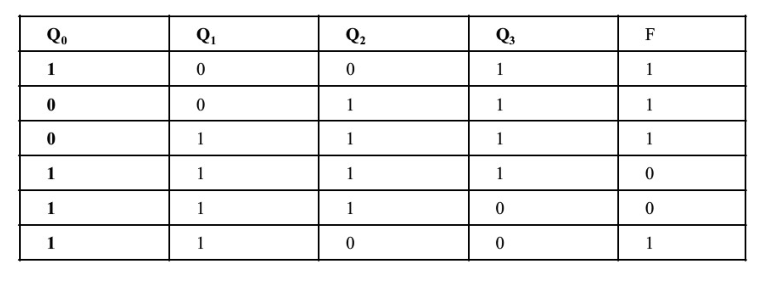

仿真出来的电路如下:

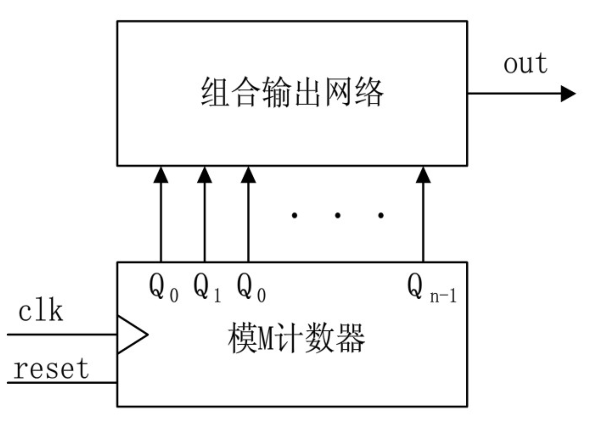

三、由计数器构成

计数型序列信号发生器和反馈型序列信号发生器大体相同,它们都是由时序电路和组合电路两部分构成。不同在于,反馈型序列信号发生器的时序状态由移位寄存器产生,输出取寄存器的最高位;而在计数型序列信号发生器中,采用计数器代替移位寄存器产生时序状态,输出由组合电路产生。

计数型的好处在于,计数器的状态设置与输出序列没有直接关系,不需要像上面一样,根据输出确定状态。只需要将反馈网络设计好就可以了。因此计数结构对于输出序列的更改比较方便,而且只要连接到不同的反馈网络,它可以同时产生多组序列码

设计过程分为两步:第一,根据序列码的长度M设计模M计数器,状态可以自定;第二,按计数器的状态转移关系和序列码的要求设计组合输出网络。

对于“100111”序列的信号发生器。

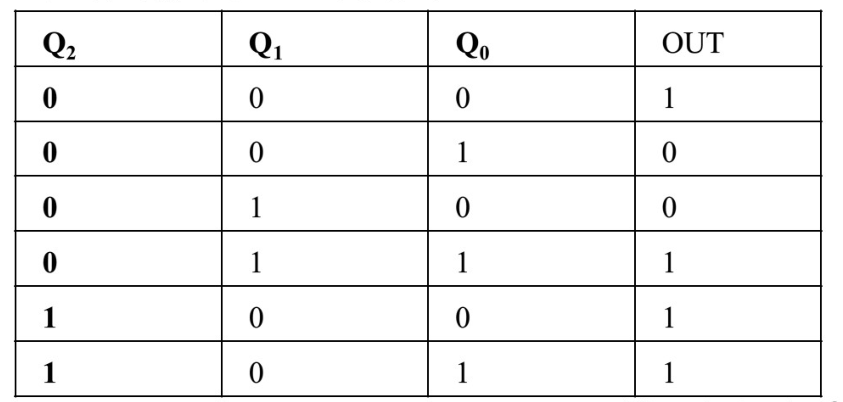

序列信号的M值为6,因为需选用模6的计数器。计数器的状态选择从000到101可以得到输出的组合逻辑真值表

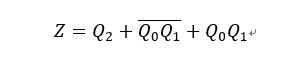

由真值表可画出输出Z的卡诺图,得到输出函数:

代码如下(示例):

module signal_maker3(out,clk,reset);

parameter M=3;

output out;

input clk,reset;

reg[M-1:0] counter;

always @(posedge clk)

if(!reset)

count<=3'b000;

else

counter<=counter+1;

assign out=counter[2]|((counter[1])&(~counter[0]))|(counter[1]&counter[0]);

endmodule

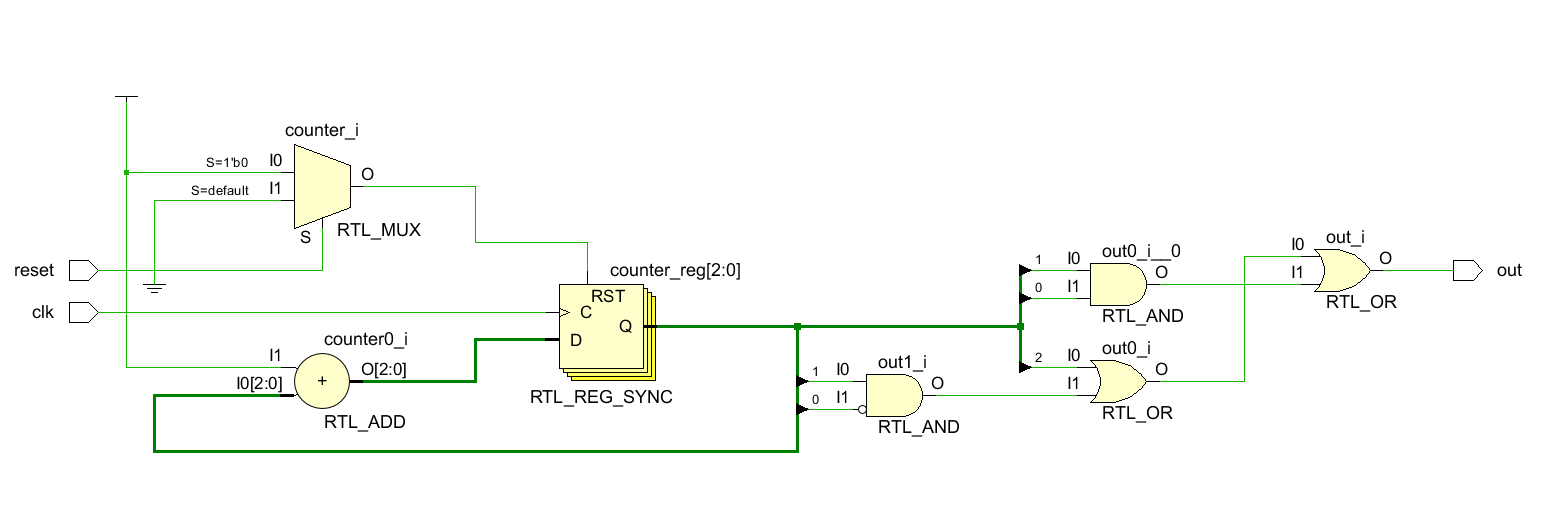

仿真出来的电路:

最后

以上就是碧蓝皮带最近收集整理的关于Verilog 序列信号发生器的三种设计思路前言一、由移位寄存器构成二、由移位寄存器和组合逻辑电路构成三、由计数器构成的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复