我是靠谱客的博主 踏实樱桃,这篇文章主要介绍Quartus中移位寄存器的使用以及计算均值Quartus中移位寄存器的使用以及计算均值:verilog代码TestBench仿真代码:仿真图片:,现在分享给大家,希望可以做个参考。

Quartus中移位寄存器的使用以及计算均值:

移位寄存器可以实现对近100个数求平均值,或者是一行图像数据的缓存,实际应用时是很有用的。

verilog代码

在配置移位寄存器的ip核时,有一个taps参数,taps的个数*taps的距离就是需要的移位寄存器的位数。

module average_shift_reg(

input clk,

input rst_n,

input [7:0] data_in,

output reg[7:0] data_average

);

wire [7:0] data_out; //移位寄存器的输出

reg [4:0] cnt; //计数器,对第一轮16个数据进行计数

reg [23:0] data_sum; //输入的16个数的和

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

cnt <= 5'd0;

else if(cnt == 5'd16)

cnt <= cnt;

else

cnt <= cnt + 5'd1;

end

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

data_sum <= 24'd0;

else if(cnt == 5'd16)

data_sum <= data_sum + data_in - data_out;

else

data_sum <= data_sum + data_in;

end

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

data_average <= 8'd0;

else if(cnt == 5'd16)

data_average <= data_sum / 5'd16;

else

data_average <= data_average;

end

shift_reg u_shift_reg(

.clock (clk),

.shiftin (data_in),

.shiftout (data_out),

.taps ()

);

endmodule

TestBench仿真代码:

`timescale 1 ns/ 1 ps

module average_shift_reg_tb();

reg clk;

reg [7:0] data_in;

reg rst_n;

wire [7:0] data_average;

average_shift_reg i1 (

.clk(clk),

.data_average(data_average),

.data_in(data_in),

.rst_n(rst_n)

);

initial

begin

clk = 1'b0;

rst_n = 1'b0;

#200;

rst_n = 1'b1;

end

always #10 clk = ~clk;

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

data_in <= 8'd0;

else if(data_in == 8'd31)

data_in <= 8'd0;

else

data_in <= data_in + 8'd1;

end

endmodule

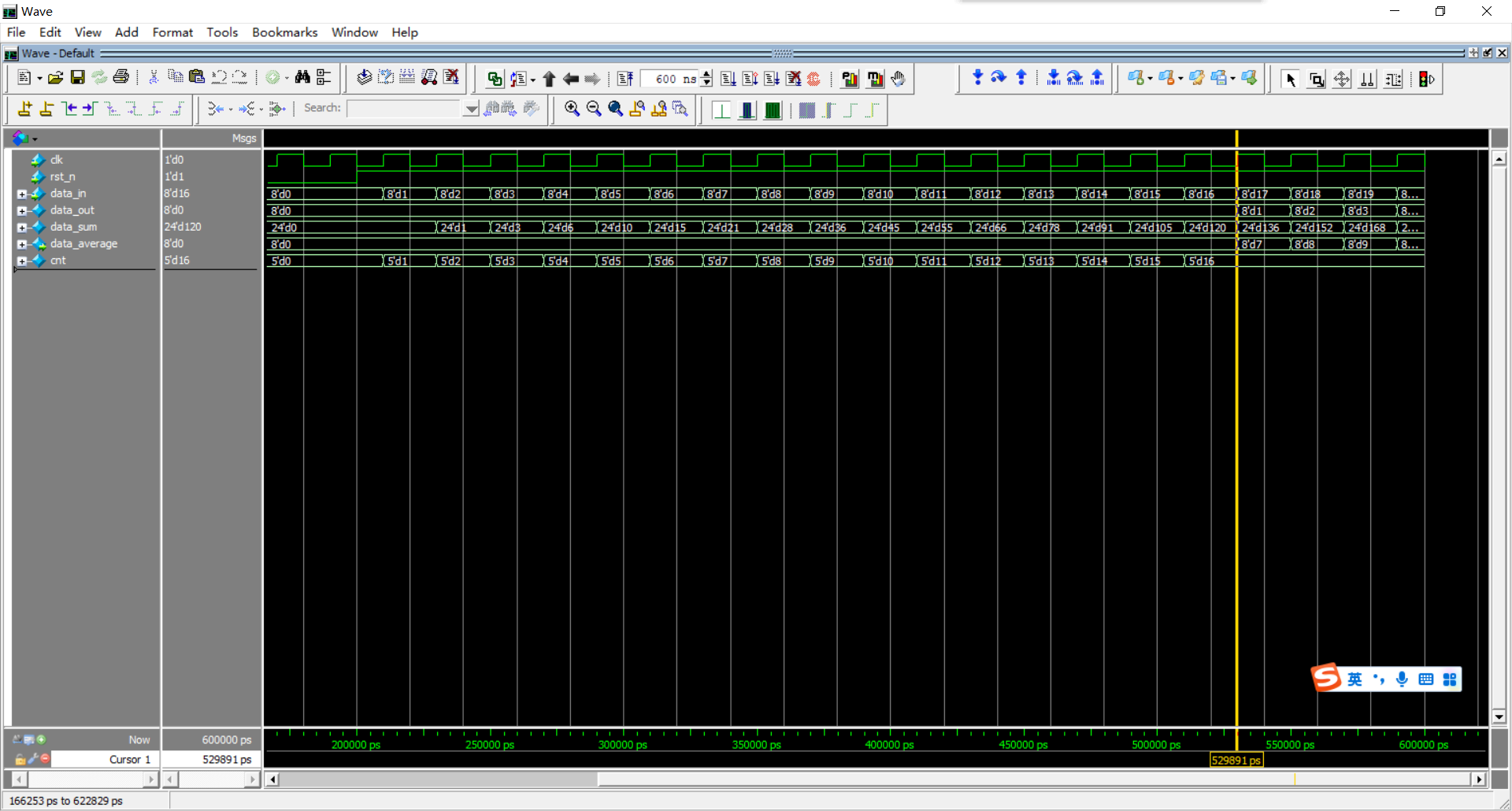

仿真图片:

最后

以上就是踏实樱桃最近收集整理的关于Quartus中移位寄存器的使用以及计算均值Quartus中移位寄存器的使用以及计算均值:verilog代码TestBench仿真代码:仿真图片:的全部内容,更多相关Quartus中移位寄存器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复