前言

-

之前的文章《如何学习verilog,如何快速入门?》中提到了verilog学习,推荐了一个可以练习的网站:hdlbits网站,那自己也玩玩这个网站。

-

这篇文章,是接着《verilog练习:hdlbits网站上的做题笔记(2)》写的!

2.5 More Verilog Features

2.5.1 Conditional ternary operator(Conditional)

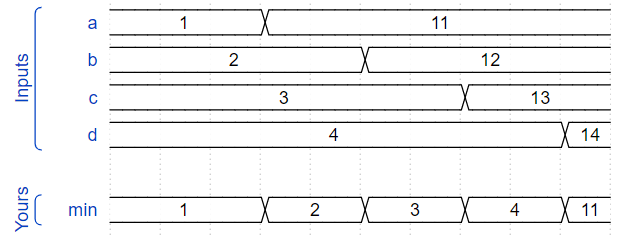

找出四个数中最小值,提示的是五行代码!

module top_module (

input [7:0] a, b, c, d,

output [7:0] min);//

// assign intermediate_result1 = compare? true: false;

wire [7:0] intermediate_result1;

wire [7:0] intermediate_result2;

assign intermediate_result1 = a < b ? a : b;

assign intermediate_result2 = c < d ? c : d;

assign min = intermediate_result2 < intermediate_result1 ? intermediate_result2 : intermediate_result1;

endmodule

2.5.2 Reduction operators(Reduction)

前面有个题目用到了这个思想!

& a[3:0] // AND: a[3]&a[2]&a[1]&a[0]. Equivalent to (a[3:0] == 4’hf)

| b[3:0] // OR: b[3]|b[2]|b[1]|b[0]. Equivalent to (b[3:0] != 4’h0)

^ c[2:0] // XOR: c[2]c[1]c[0]

通过不完善的通道传输数据时,奇偶校验通常用作检测错误的简单方法。

创建一个电路,该电路将计算8位字节的奇偶校验位(这将在字节中添加第9位)。我们将使用“偶数”奇偶校验,其中奇偶校验位只是所有8个数据位的XOR。

module top_module (

input [7:0] in,

output parity);

assign parity = ^in;

endmodule

2.5.3 Reduction: Even wider gates(Gates100)

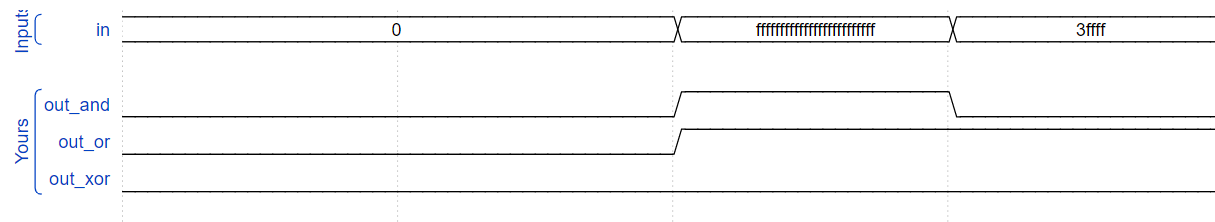

out_and: output of a 100-input AND gate.

out_or: output of a 100-input OR gate.

out_xor: output of a 100-input XOR gate.

module top_module(

input [99:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and = ∈

assign out_or = | in;

assign out_xor = ^ in;

endmodule

2.5.4 Combinational for-loop: Vector reversal 2(Vector100r)

Given a 100-bit input vector [99:0], reverse its bit ordering.

把100位的输入从头到尾反转,对于这种重复性的工作,第一反应就是使用循环去实现。

【此处同第一篇文章的2.2.7】

//方法1

module top_module(

input [99:0] in,

output [99:0] out

);

integer i;

always@(*)begin

for(i=0;i<100;i=i+1)begin

out[99-i] = in[i];

end

end

endmodule

- 下面这个例子就是说明:assign是可以出现在for循环(begin…end)中的,但是需要generate来包住!

module top_module(

input [99:0] in,

output [99:0] out

);

generate

genvar i;

for(i = 0; i <= 99; i = i + 1)begin:reverse

assign out[i] = in[99 - i];

end

endgenerate

endmodule

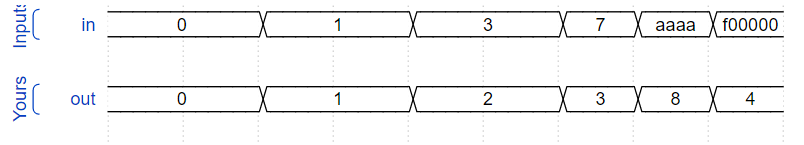

2.5.5 Combinational for-loop: 255-bit population count(Popcount255)

//方法1

module top_module(

input [254:0] in,

output [7:0] out );

integer i;

always@(*)begin

out = 0;

for(i=0;i< 255;i=i+1)begin

if(in[i])

out = out + 1;

else

out = out;

end

end

endmodule

//方法2

module top_module(

input [254:0] in,

output [7:0] out );

integer i;

always@(*)begin

out = 1'b0;

for(i=0;i< 255;i=i+1)begin

out = out + in[i];

end

end

endmodule

2.5.6 Generate for-loop: 100-bit binary adder 2(adder100i)

行波进位加法器?

//第一种方法

module top_module(

input [99:0] a, b,

input cin,

output [99:0] cout,

output [99:0] sum );

integer i;

always@(*)begin

{cout[0],sum[0]} = a[0]+b[0]+cin;

for(i=1;i< 100;i=i+1)begin

{cout[i],sum[i]} = a[i]+b[i]+cout[i-1];

end

end

endmodule

//第二种方法

module top_module(

input [99:0] a, b,

input cin,

output [99:0] cout,

output [99:0] sum );

generate

genvar i;

for(i=0;i<=99;i=i+1)begin:adder//这个地方的名字不能省略,否则会给你报错:缺名字

if(i == 0) begin assign {cout[0],sum[0]} = a[0]+b[0]+cin; end

else begin assign {cout[i],sum[i]} = a[i]+b[i]+cout[i-1]; end

end

endgenerate

endmodule

2.5.7 Generate for-loop: 100-digit BCD adder

You are provided with a BCD one-digit adder named bcd_fadd that adds two BCD digits and carry-in, and produces a sum and carry-out.

module bcd_fadd {

input [3:0] a,

input [3:0] b,

input cin,

output cout,

output [3:0] sum );

Instantiate 100 copies of bcd_fadd to create a 100-digit BCD ripple-carry adder. Your adder should add two 100-digit BCD numbers (packed into 400-bit vectors) and a carry-in to produce a 100-digit sum and carry out.

module top_module(

input [399:0] a, b,

input cin,

output cout,

output [399:0] sum );

wire[99:0] cout_1;

generate

genvar i;

for(i = 0; i <= 99; i = i + 1)begin:adder

if(i == 0)begin

bcd_fadd u_bcd_fadd(

.a (a[3:0] ),

.b (b[3:0] ),

.cin (cin ),

.sum (sum[3:0] ),

.cout (cout_1[0] )

);

end

else begin

bcd_fadd ui_bcd_fadd(

.a (a[4 * i + 3: 4 * i] ),

.b (b[4 * i + 3: 4 * i] ),

.cin (cout_1[i - 1] ),

.sum (sum[4 * i + 3: 4 * i] ),

.cout (cout_1[i] )

);

end

end

assign cout = cout_1[99];

endgenerate

endmodule

后记

冲冲冲!

最后

以上就是心灵美玉米最近收集整理的关于verilog练习:hdlbits网站上的做题笔记(3)前言后记的全部内容,更多相关verilog练习:hdlbits网站上内容请搜索靠谱客的其他文章。

发表评论 取消回复