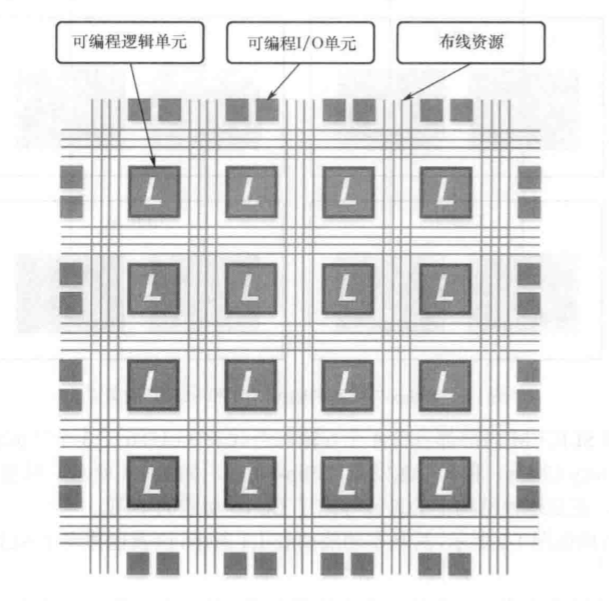

FPGA主要由以下几部分组成:

(1)基本可编程逻辑单元(CLB)

(2)可编程输入输出单元(IOB)

(3)嵌入式块RAM

(4)内嵌的底层功能单元和嵌入式专用硬核

(5)完整的时钟管理模块

(6)丰富的布线资源

一、总体结构

二、基本组成部分

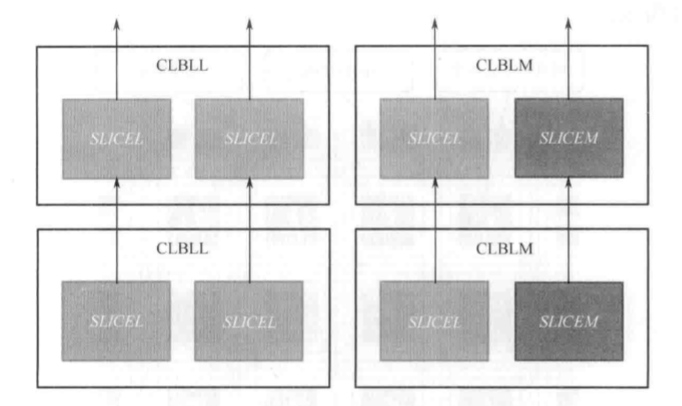

1、可配置逻辑单元(Configurable Logic Block,CLB)

CLB由两个SLICE构成,SLICE可分为SLICEL(L:Logic)和SLICEM(M:Memory),因此CLB也可分为CLBLL和CLBLM两类。

SLICE由查找表(LUT)和寄存器(Register)组成,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟使能的触发器,也可以配置成为锁存器。FPGA一般依赖寄存器完成同步时序逻辑设计。

学习底层配置单元的LUT和Register比率的重要意义在于器件选型和规模估算。

注意:FPGA中组合逻辑全部使用查找表LUT实现,此外,查找表也可用来作为分布式存储使用。

2、可编程输入输出单元(IOB)

目前大多数FPGA的I/O单元被设计为可编程模式,即通过软件的灵活配置,可适应不同的电器标准与I/O物理特性;可以调整匹配阻抗特性,上下拉电阻;可以调整输出驱动电流的大小等。

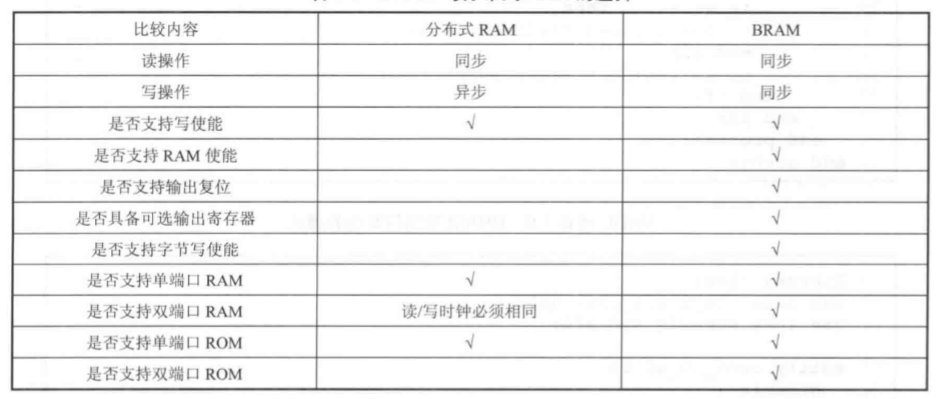

3、嵌入式块RAM

目前大多数FPGA都有内嵌的块RAM。嵌入式块RAM可以配置为单端口RAM、双端口RAM、伪双端口RAM、CAM、FIFO等存储结构。

尽管BRAM的功能更多,但是对于一些小规模的数据存储,分布式RAM可能获得比BRAM更好的性能(从功耗和速度两方面讲)。

4、内嵌的底层功能单元和嵌入式专用硬核

底层嵌入功能单元是指通用程度较高的嵌入式功能模块。如锁相环(Phase Locked Loop,PLL)、DLL(Delay Locked Loop)、DSP(Digital Signal Processing)和CPU等。

与“底层嵌入单元”是有区别的,这里指的硬核主要是那些通用性相对较弱,不是所有FPGA器件都包含硬核。

5、完整的时钟管理

全局时钟是一种专用互联网络,是专为覆盖对FPGA中各种资源的所有时钟输入设计的。这些时钟网络的设计旨在降低歪斜、占空比失真和功耗。其设计的目的还在于支持甚高频信号。

全局时钟控制资源和网络通常由以下通路和组件构成:全局时钟输入 、全局时钟缓冲器 、时钟树和时钟网络-GCLK 、时钟区域。

6、丰富的布线资源

长线资源、短线资源及逻辑单元內部布线资源。

最后

以上就是认真小懒猪最近收集整理的关于FPGA的基本结构的全部内容,更多相关FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复