前言

做了三个月FPGA相关工作但是一直不是很了解FPGA的最基本的组成结构,马上也临近校招了,这也是很多公司面试的必考问题,那么FPGA的基础结构都有什么?应该怎么用?你写的代码最终会被综合成什么样的电路?要想成为“人肉综合器”,那么了解FPGA基础结构就是第一步,本文以Xilinx 7 series FPGA为例,对FPGA基本组成进行分析与讨论。

FPGA资源划分

- FPGA层级

- FPGA=>ASMLB(高级硅模块)=>SLR(Super Logic Region)=>各种逻辑资源(本文详解)

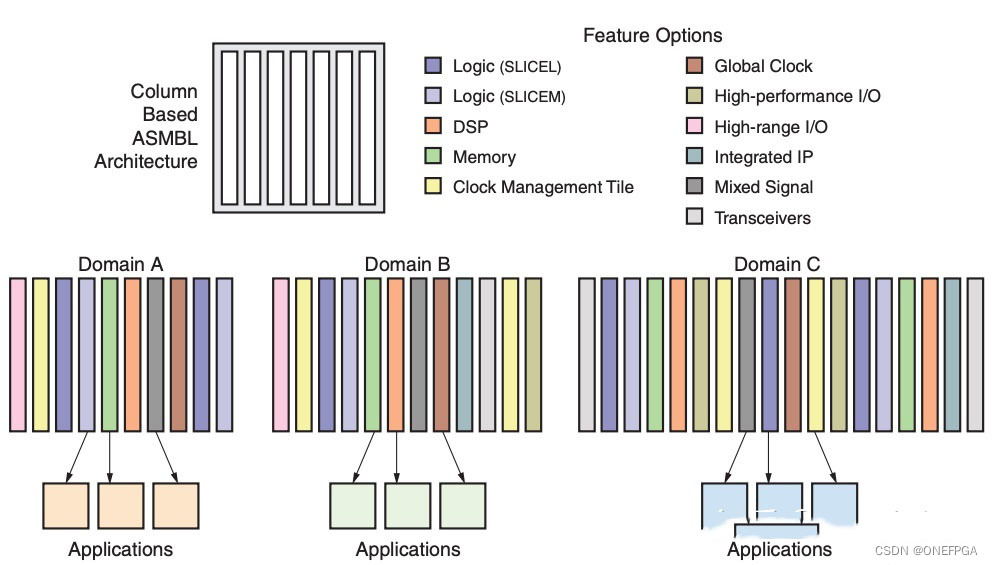

- ASMBL(高级硅模块)

高级硅模块如上图所示,我理解就是Xilinx创造出的一种FPGA架构,将资源按列划分,所以我们在Vivado Device视图的时候也可以看到一列一列的资源,有利于后续布局布线、IO口分布、增强片上功率等等。

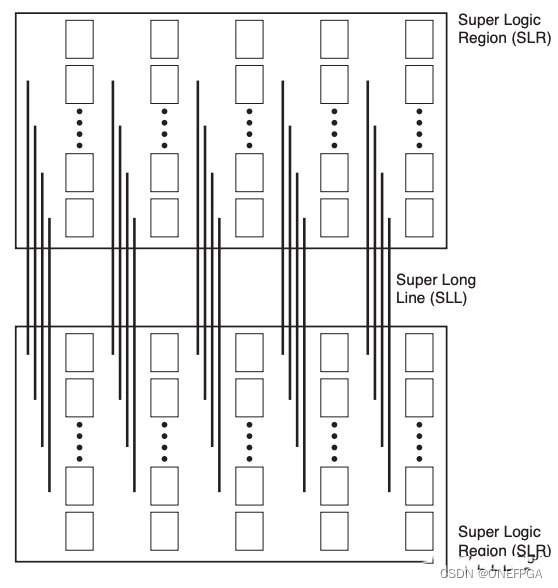

然后现在的Xilinx FPGA基本会用2个Die拼接,也就是SLR(超级逻辑区),这两个Die拥有独立逻辑资源和布线资源,中间用SLL(Super Long Line)连接,所以vivado有自己的跨die寄存器,两个寄存器用SLL连接来优化timing问题。结构如下图所示:

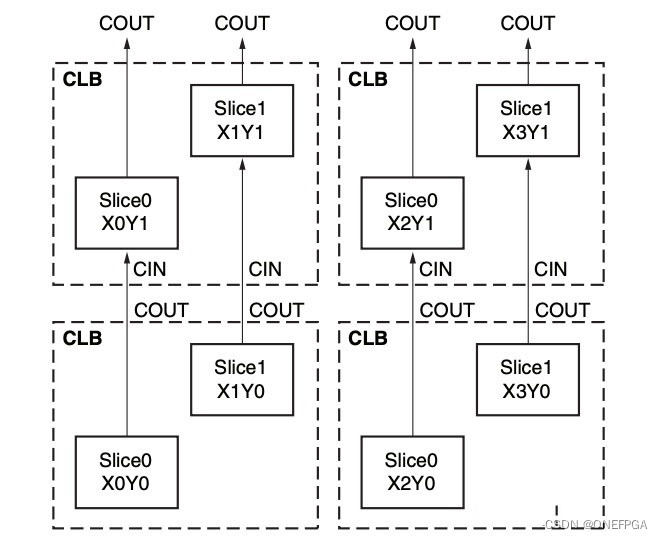

CLB(可配置逻辑块)

- CLB组成

- 1CLB=2SLICE

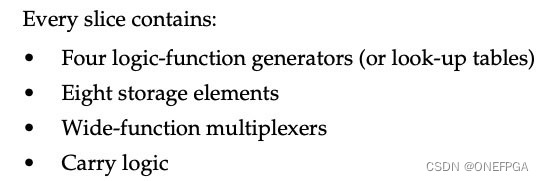

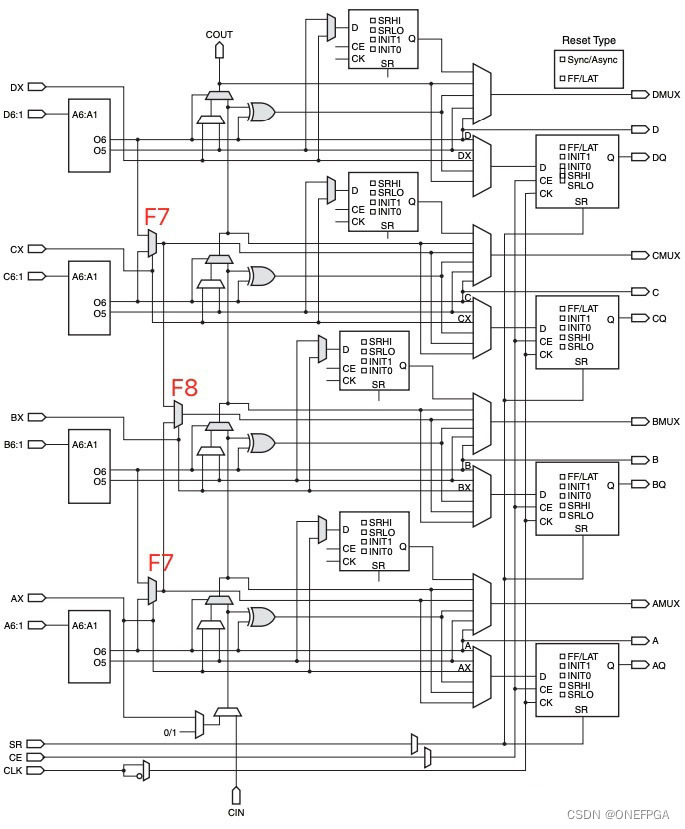

- 1SLICE = 4*LUT6+8*storage elements+3MUX+CARRY4进位链

1个CLB里面有2个SLICE,SLICE可分为SLICEM和SLICEL,M代表memory,L代表logic,顾名思义,带M的SLICE可以用于组成disturbuted ram和shift register,带L的SLICE用于逻辑资源。

1个SLICE中有4个LUT6,8个寄存器,3个2选1MUX和一个4bit的加法器进位链,这些后续会进行详细介绍。

CLB中的2块SLICE不会直接相连,正如前文高级硅模块架构所示,FPGA资源以列方式排列,所以前后2个CLB的SLICE通过进位链连接,左右如果想连接只能用布线资源(switch matrix),其结构如下图所示:

LUT(look up table)

FPGA中的LUT无疑是FPGA中最重要的资源,那么本文先介绍LUT,查找表是FPGA最小组成单元,有6位输入,2个独立输出,功能类似于ROM,可以理解为通过6位“地址线”来索引输出。LUT内部有真值表,可以作为一个有6输入1输出的布尔函数。

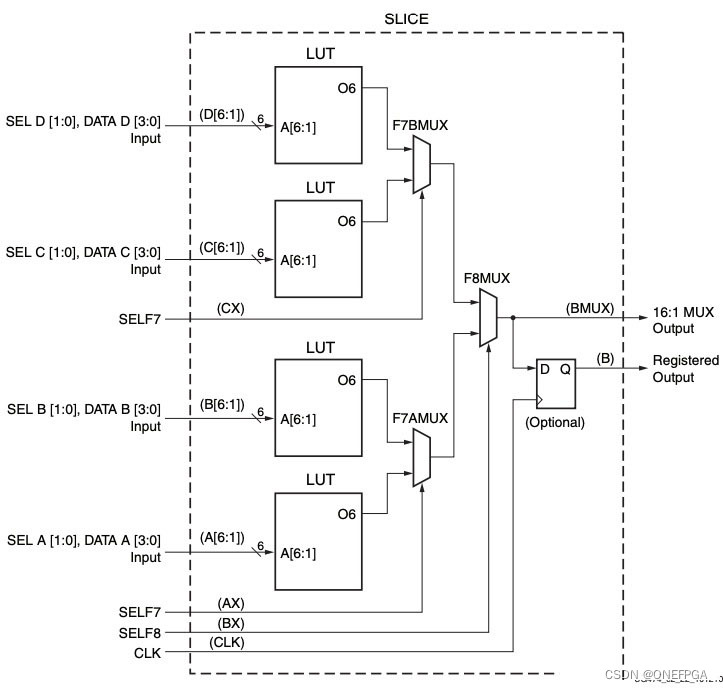

此外,1个SLICE除了包含LUT,还有3个多路选择器(F7AMUX, F7BMUX, and F8MUX),F7的意思是与LUT6和1个额外输入组成1个7输入选择器,F8代表与LUT6和2个F7MUX额外输入共组成8输入选择器。可参见如下示意图:

FPGA岗位常问问题:16选1MUX应该怎么搭?

- 1个LUT6可以组成一个4:1MUX,LUT6中的4个输入作为4选1的输入端,LUT6的另外2个输入作为选择器的选择端。

- 那么就有两种搭建方法,只用LUT6,那么就需要5个,2级逻辑。

- 或者是4个LUT6加2*F7MUX+F8MUX,正好在1个slice里,如下图所示

FPGA岗位常问问题:1个LUT可以组成多大的Distributed RAM?

- 由于LUT6有6个输入,那么地址线就可以有6根,输出端O6为1bit,根据内部真值表可以判断输出端O6是1/0,那么本质上LUT6可以组成一个最大64深,1bit位宽的单口RAM。

Distributed RAM深度较大但是位宽很小,所以适用场景也就是小位宽大深度的,同时要知道Distributed RAM时序timing要比Block RAM差。Block RAM分为18K和36K,对应数据位宽最大为36和72,深度最小为512。所以大家在应用时要考虑timing和资源平衡问题,这几个参数也是FPGA常问问题。

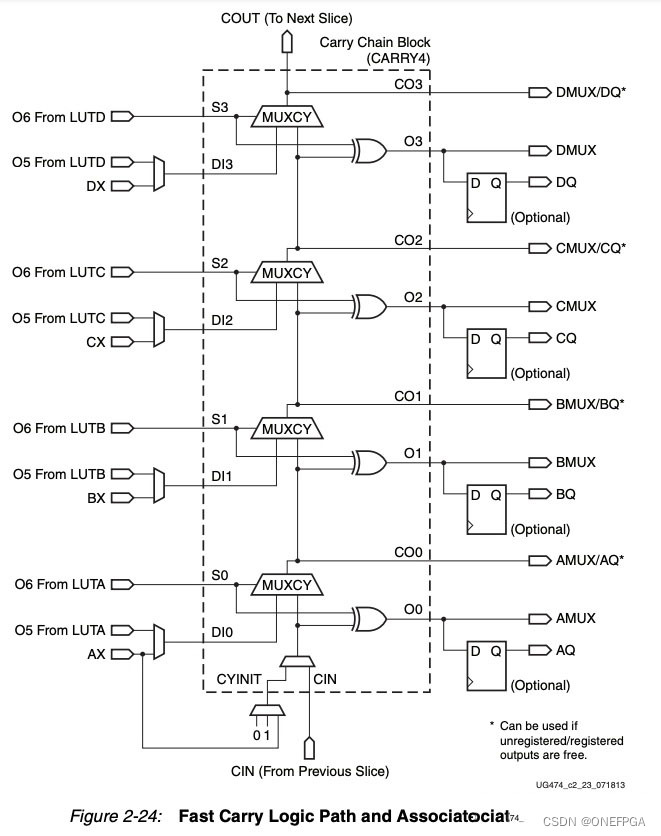

加法器进位链(CARRY4)

SLICE另一个重要资源就是加法器进位链,每个SLICE中有一个4bit加法器进位链,也叫CARRY4,可以与前后级SLICE组成更长的进位链,其结构如下图所示:

CARRY4进位链原理

-

- 假设有2个4bit加数:a[3:0],b[3:0]

- S0~S3为输入端异或,即S=a^b;

- DI0~DI3为其中1个输入,比如D=a;

- CIN为上一级CARRY4的进位端;

- O0为对应bit位加法结果:O=S^CIN=a^b^c,也就是说2输入和CIN有奇数个1时,对应bit输出1,符合加法器原理;

- CO为加法器进位端,通过上图可知:C0 = ~(a^b)&a+a^b&c;其中c为上一级的进位端,大家可以列一个真值表,发现其可实现加法器的进位端输出,只是不是我们常用的化简公式而已。

-

最后

以上就是鲜艳云朵最近收集整理的关于FPGA基础结构的全部内容,更多相关FPGA基础结构内容请搜索靠谱客的其他文章。

发表评论 取消回复