该篇是FPGA数字信号处理的第七篇,上一篇介绍了直接型IIR滤波器的原理,详细介绍使用Verilog HDL设计直接型IIR滤波器的方法。本文会介绍如何用Verilog HDL设计级联型IIR滤波器。级联型IIR计算速度快,占用资源少,比起直接型更为常用。

IIR滤波器

将IIR滤波器系统函数的分子分母进行因式分解(分解为实数和复共轭对),再将每一对共轭因子合并为实数二阶因子:

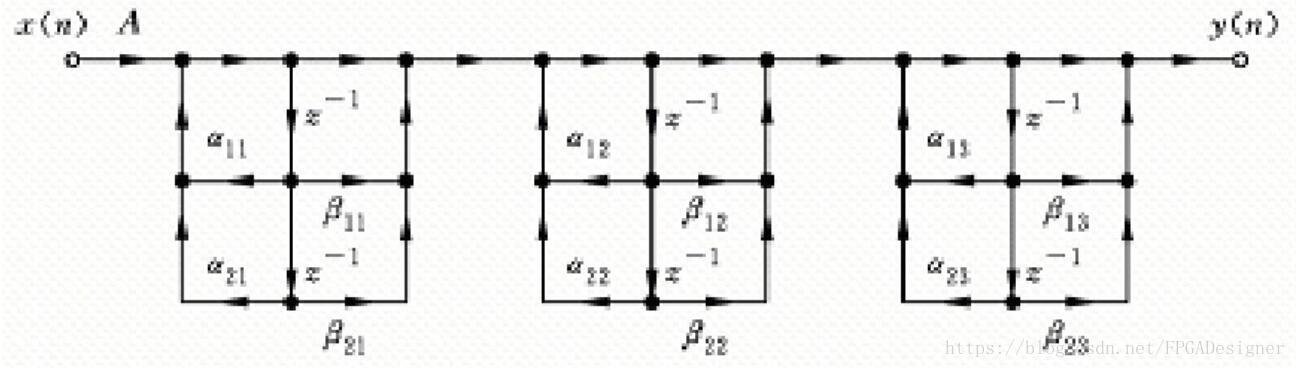

每个Hk(z)称作一个二阶基本节,使用直接II型结构实现,级联为整个系统所需的存储单元最少,这样的结构称作级联型IIR滤波器结构。一个六阶IIR滤波器级联结构如下图所示,由3级二阶基本节级联组成:

相比直接型IIR:(1).级联型结构每一个二阶基本节中反馈网络少,可以更好地控制有限字长效应带来的误差;(2).调整每一个基本节相当于单独调整滤波器的零点和极点,调整方便;(3).每个基本节结构相同,FPGA实现简单。因此设计中更多使用级联型IIR。

FPGA设计

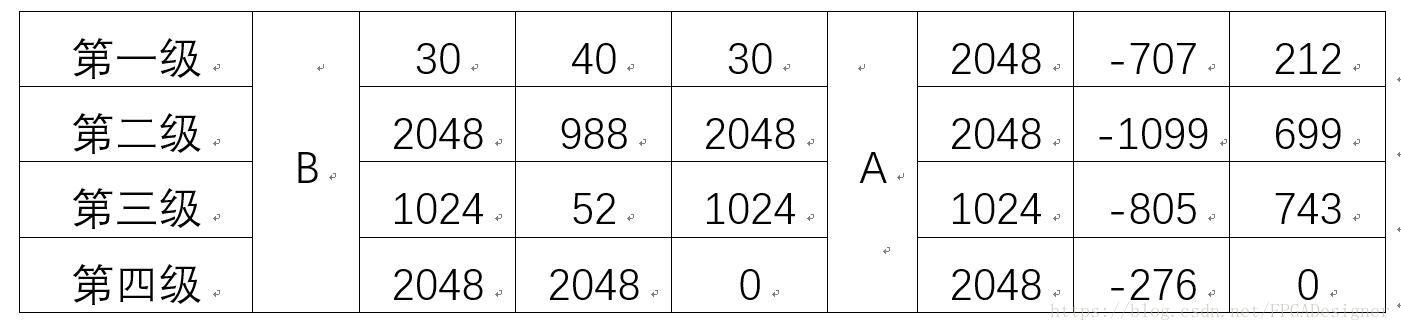

在MATLAB中设计好IIR滤波器,再到FPGA最重要的工作便是滤波器系数的量化。设计一个切比雪夫II型滤波器cheby(7,60,0.5),将系数转换为级联型结构并量化(MATLAB程序可参考文末下载工程中的m文件,或参考杜勇老师的《数字滤波器的MATLAB与FPGA实现》这本书),量化后的系数如下表所示:

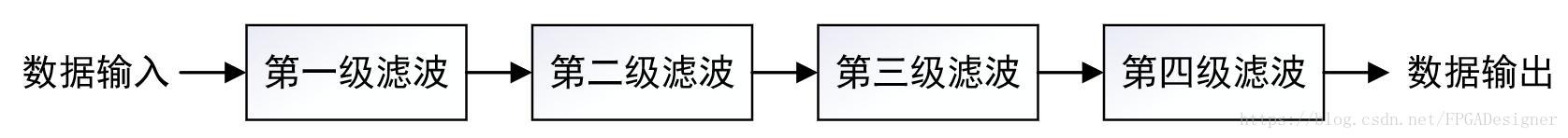

级联型IIR将一个8阶滤波器拆分为三个3阶滤波器和一个2阶滤波器,前一级滤波器的输出作为后一级滤波器的输入。每一级的系数如上表所示,零点向量b仍可以利用对称性节省乘法器;极点向量a的第一个系数(y(n)的系数)不为1,在每一级的输出应该加入除法器。

根据级联型IIR结构,FPGA整体设计框图如下图示:

Verilog HDL设计

由于IIR滤波器在DSP系统中不常用,Quartus和Vivado都没有提供相关的IP核,因此只能自己进行Verilog设计。本文设计参考自杜勇老师的《数字滤波器的MATLAB与FPGA实现》。本设计将在Vivado环境下完成并仿真。

每一级滤波子模块都相当于一个低阶的直接型IIR滤波器,无论是零点部分还是极点部分的实现都与“FPGA数字信号处理(六)直接型IIR滤波器Verilog设计” https://blog.csdn.net/fpgadesigner/article/details/80652480 相同,可以下载文末的工程浏览,本文不再赘述。

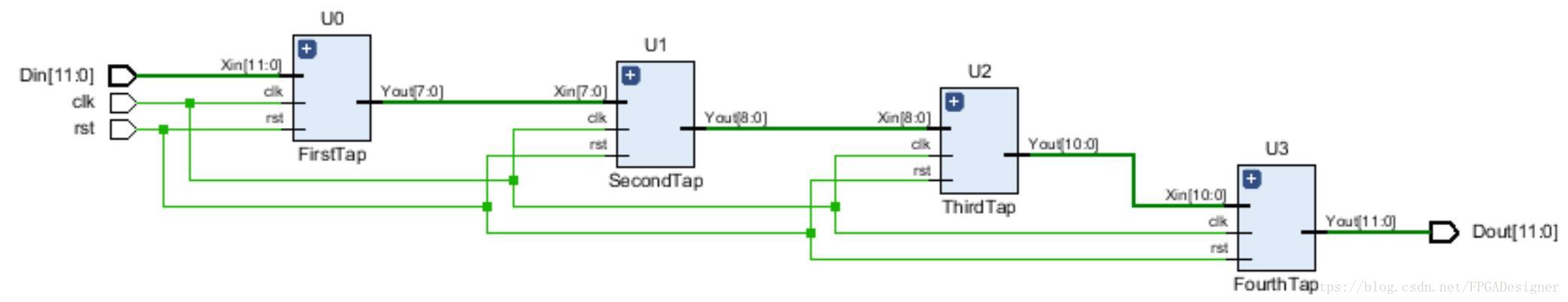

顶层模块实例化四个滤波子模块,并按照设计框图控制好数据流向,完成IIR滤波子模块的级联:

`timescale 1ns / 1ps

//-------------------------------------------------------------------------

// 级联型IIR滤波器顶层模块

//-------------------------------------------------------------------------

module CascadeIIR_liuqi

(

input clk,

input rst,

input signed [11:0] Din,

output signed [11:0] Dout

);

//第一级

wire signed [7:0] Y1;

FirstTap U0

(

.rst (rst),

.clk (clk),

.Xin (Din),

.Yout (Y1)

);

//第二级

wire signed [8:0] Y2;

SecondTap U1

(

.rst (rst),

.clk (clk),

.Xin (Y1),

.Yout (Y2)

);

//第三级

wire signed [10:0] Y3;

ThirdTap U2

(

.rst (rst),

.clk (clk),

.Xin (Y2),

.Yout (Y3)

);

//第四级

FourthTap U3

(

.rst (rst),

.clk (clk),

.Xin (Y3),

.Yout (Dout)

);

endmodule每一级的输出部分都需要进行截取,截取时可以先进行仿真,只保留一位符号位即可。综合没有问题之后,打开Vivado中的RTL ANALYSIS,级联型IIR滤波器系统原理图如下所示,与预期设计相同:

仿真与工程下载

使用MATLAB生成一个200khz+800kHz的混合频率信号,写入txt文件。编写Testbench读取txt文件对信号滤波,文件操作方法参考“Testbench编写指南(一)文件的读写操作”https://blog.csdn.net/fpgadesigner/article/details/80470972。

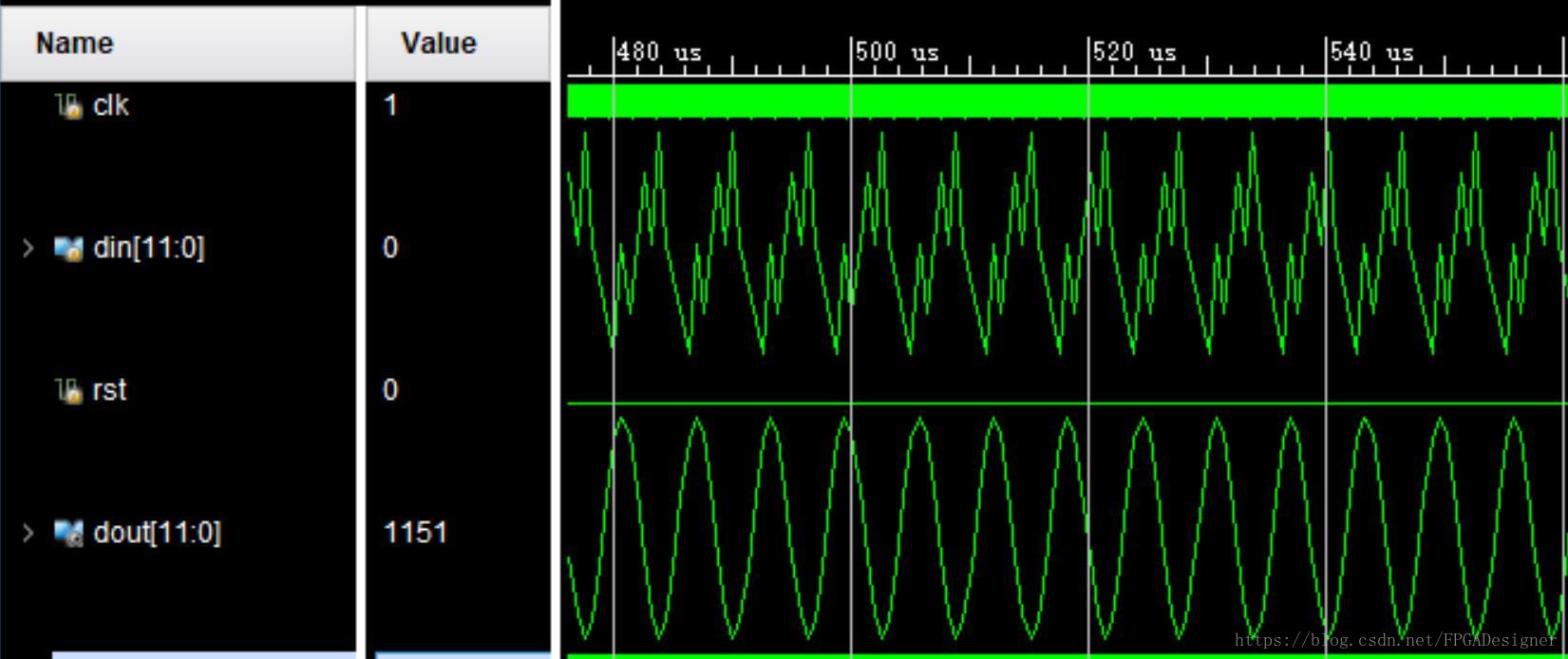

对正弦信号的滤波如下图所示:

明显看到经过500Hz低通滤波器滤波后,输入的200+800Hz信号只剩下200Hz的频率分量。

完整的Vivado工程(含testbench仿真)可以在这里下载:https://download.csdn.net/download/fpgadesigner/10472359

最后

以上就是曾经哈密瓜最近收集整理的关于FPGA数字信号处理(七)级联型IIR滤波器Verilog设计IIR滤波器FPGA设计Verilog HDL设计仿真与工程下载的全部内容,更多相关FPGA数字信号处理(七)级联型IIR滤波器Verilog设计IIR滤波器FPGA设计Verilog内容请搜索靠谱客的其他文章。

![[数字信号处理]IIR滤波器基础](https://www.shuijiaxian.com/files_image/reation/bcimg24.png)

发表评论 取消回复