目的:

1.进一步掌握数字电子技术的理论知识,培养工程设计能力和综合分析问题、解决问题的能力;

2.基本掌握常用电子电路的一般设计方法,提高电子电路的设计和实验能力;

3.掌握复杂可编程逻辑器件CPLD的原理及使用方法;

4.掌握Verilog HDL硬件描述语言的一般语法规则,学会设计方针CPLD器件,了解CPLD的烧写过程;

5.熟悉并学会选用电子元器件,为以后从事科研和生产工作打下一定的基础。

内容:

用Verilog HDL对CPLD进行编程,并增加适当的电子元件,设计一个数字电子时钟电路,要求

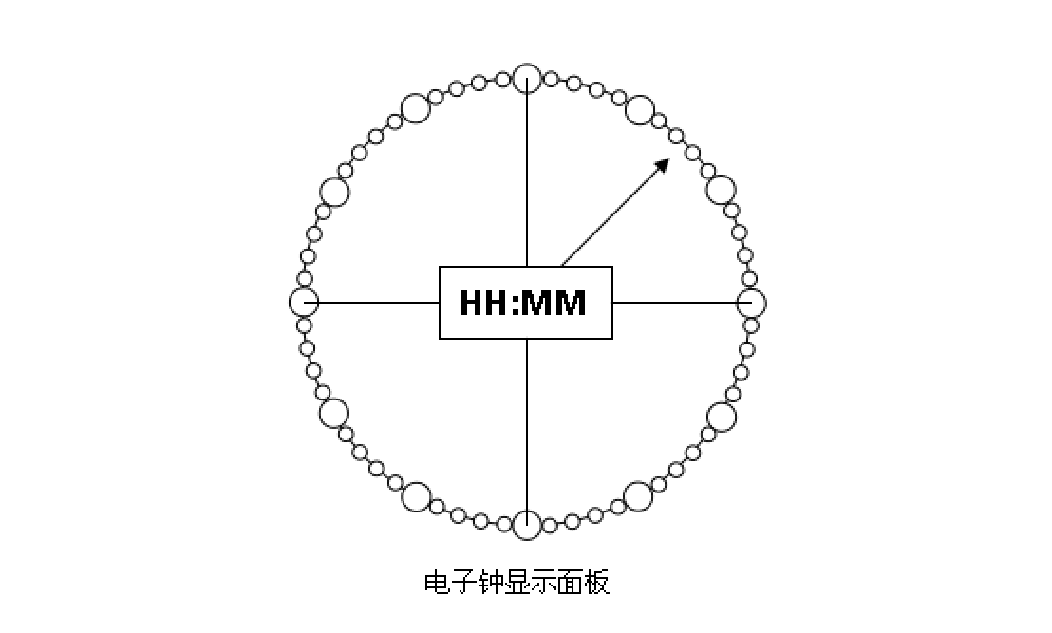

1.具有“时”“分”的数字显示功能,并可以进行时间校准

2.用发光二极管设计一个“表盘”,通过对应发光二极管的依次点亮来模拟表盘显示时间。

资源

大家自行下载吧

https://download.csdn.net/download/baidu_41907100/12431126

最后

以上就是花痴天空最近收集整理的关于数字电子钟设计制作——数字逻辑课程设计 Verilog HDL CPLD目的:内容:资源的全部内容,更多相关数字电子钟设计制作——数字逻辑课程设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复