D触发器的设计并调用D触发器设计4位串行移位寄存器:

1、设计原理

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。因此,D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。移位寄存器不仅能寄存数据,而且在时钟信号的最用下使它其中的数据依次左移或者右移或循环左移和循环右移。四位移位寄存器的原理:F0、F1、F2、F3是四个边沿触发的触发器D,每一个触发器的输出端Q接到右边一个触发器的输入端D。因为从时钟的信号CP的上升沿加到触发器上开始到输出端新状态稳定地建立起来有一段延迟的时间,所以当时钟信号同时加到四个触发器上的时候,每个触发器接受的都是左边一个触发器中原来的而数据(F0接收的输入数据D1)。寄存器中的数据依次右移一位。

2、设计源文件

(1)D触发器模块

`timescale 1ns / 1ps

// Create Date: 2022/05/30 10:11:42

// Module Name: D_chufa

module D_chufa(d,clk,q);

input d;// 输入

input clk;// 时钟

output q;// 输出

reg q;

always @ (posedge clk)

begin

q <= d;

end

endmodule

(2)调用D触发器来构成移位寄存器模块

`timescale 1ns / 1ps

/

// Create Date: 2022/05/30 17:07:00

// Module Name: yiwei

/

module yiwei(d,clk,q);

input d,clk;// clk:时钟 d:输入

output [3:0]q;//输出

begin

D_chufa u1(d,clk,q[0]);

D_chufa u2(q[0],clk,q[1]);

D_chufa u3(q[1],clk,q[2]);

D_chufa u4(q[2],clk,q[3]);

end

endmodule

3、仿真测试文件

`timescale 1ns / 1ps

/

// Create Date: 2022/05/30 20:13:51

// Module Name: sim_yiwei

/

module sim_yiwei();

reg d;

reg clk;

wire [3:0]q;

yiwei u1(d,clk,q);

initial//产生时钟

begin

clk=0;

forever #50 clk=~clk;

end

initial //产生激励

begin

d=0;

#40;d=~d;

#40;d=0;

end

endmodule

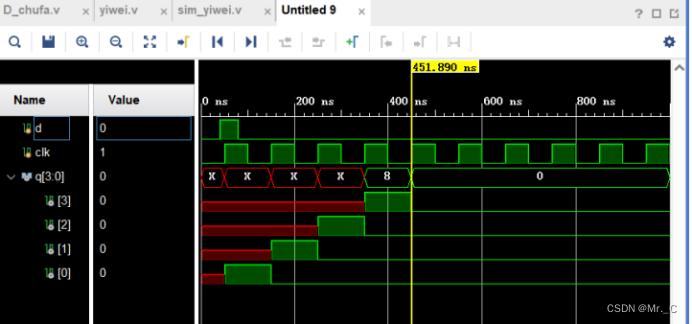

4、仿真结果及分析

给d信号0,可以看到当时钟信号上升沿到来时q[0],q[1],q[2],q[3]依次变为0,给d信号1,当时钟信号上升沿到来时q[0],q[1],q[2],q[3]依次变为1,实现了移位寄存器的功能。

最后

以上就是调皮大树最近收集整理的关于【FPGA】D触发器的设计并调用D触发器设计4位串行移位寄存器D触发器的设计并调用D触发器设计4位串行移位寄存器:的全部内容,更多相关【FPGA】D触发器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复