这里写目录标题

- 一、初始化

- 二、读入设计

- 三、时序约束

- 3.1创建时钟

- 3.2传播时钟

- 3.3时钟歪斜

- 3.4生成时钟

- 3.5门控时钟

- 四、导出报告

- 4.1 生成约束报告 report_constraint

- 4.2 生成路径延迟报告 report_timing

一、初始化

PT启动时需要初始化,参照上节内容完成。

二、读入设计

PT不能读取 RTL 源文件,它是静态分析引擎,只能读取映射后的设计,包括db、verilog、vhdl 等格式的文件。读入设计的命令格式如下:

pt_shell>read_db -netlist_only <filename>.db

pt_shell>read_verilog <filename>.sv

由于db格式的网表中包含了约束和环境属性等,故使用-netlist_only选项指示PT只加载结构化网表。

三、时序约束

时序分析的基本前提是精确指定时钟,包括延时、不确定性等。PT支持如下类型的时钟信息:

多个时钟(Multiple clocks):PT允许定义具有不同频率和占空比的多个时钟。时钟可以是真实时钟(具有端口 port 或 pin 等实际来源)或虚拟时钟。

时钟网络延时与歪斜 (Clock network delay and skew):PT 允许指定时钟网络的延时,比如相对于时钟源的延时,即clock latency;以及到达时钟网络目的节点的时间变化,即 clock skew。

门控时钟(Gated clock):门控时钟是指一个受控于门控逻辑(gating logic)的时钟信号。PT支持门控信号的建立时间和保持时间检查。

**生成时钟 (Generated clocks):**生成时钟是指由设计本身的电路从某个时钟信号产生的时钟,比如由时钟分频器生成的时钟。

时钟翻转时间 (Clock transition times ):翻转时间指信号从一个逻辑状态向另一个逻辑状态改变所需要的时间。下面简要介绍时钟约束的定义与相关命令:

3.1创建时钟

定义一个时钟源,即时钟的周期、波形、名称和所在引脚,用到的命令为:

create_clock -period <value> -waveform {rising_edge> <falling edge> } <sourcelist>

例如要为端口 CIK 创建周期为 20ns 的时钟,50%占空比,即上升和下降边沿分别在0ns 和10ns 处,命令如下:

pt_shell> create_clock -period 20 -waveform {0 10} [get ports CLK]

再比如为端口 CI 和CK2创建周期为 10ns,上升沿在 2ns,下降沿在 4ns处的时钟,命令如下:

pt_shell> create_clock -period 10 -waveform {2 4} {C1 CK2}

下列命令用于指定时钟延迟和时钟转换。

set_clock_latency <value> <clock list>

set_clock_transition <value> <clock list>

定义 CIK 端口的时钟延迟为 2.5ns,固定时钟翻转时间为 0.2ns,相应的命令为:

pt_shell> set_clock_latency 2.5 [get_clocks CUK]

pt_shell> set_clock_transition 0.2 [get_clocks CLK]

当设计中定义多个时钟时,时钟之间的关系则取决于时钟的来源以及其在设计中的用途,两个时钟之间可能是同步、异步或互斥的关系。对于不同的时钟关系,其定义方法如下所示。

CK1和CK2同步

create_clock -period 2 -name CK1 [get_ports CLK1]

create_generated_clock -name CK2 -source [get_portsCLK1] -divide_by 2 [get pins U1/Q]

CK1和CK2 异步

create_clock -period 2 -name CK1 [get_ports CLK1]

create_clock -period 6 -name CK2 [get_pins OSC/OUT]

set_clock groups -asynchronous -group {CK1} -group {CK2}

CK1和CK2 互斥

create_clock -period 2 -name CK1 [get_ports CKP1]

create_clock -period 8 -name CK2 [get_ports CKP2]

set_clock _groups -logically_exclusive -group {CK1} -group {CK2}

3.2传播时钟

时钟通过网表中的整个时钟树网络传播以确定时钟延迟。换言之,对通过时钟树中每个单元的延迟和单元间的互连线延迟都要加以考虑。

下面的命令指示 PT通过时钟网络传播时钟:set_propagated_clock <clock list>

例如:pt_shell> set_propagated_clock [get_clocks CLK]

3.3时钟歪斜

通过下面的命令指定时钟歪斜:

set_clock_uncertainty <uncertainty value> -from <from clock> -to <to clock> -setup -hold <object list>

下例中,0.6ns 用来表示时钟信号(CLK)的建立和保持时间。

Pt_shell> set_clock_uncertainty 0.6 [get_clocks CLK]

选项-setup用于给建立时间检查应用不确定值,而-hold 选项给保持时间检查应用不确定值。必须注意的是,建立和保持的不同值不能在单个命令中实现必须使用两个单独的命令。例如:

Pt_shell> set_clock_uncertainty 1.0 -hold [get_clocks CLK]

pt_shell> set_clock_uncertainty 2.0 -setup [get_clocks CLK]

使用-from 和-to选项也能指定时钟扭斜,这对包括多个时钟域的设计有用,例如:

pt_shell>set_clock_uncertainty 0.5 -from [get_clocks CLK1] -to [get_clocks CLK2]

3.4生成时钟

设计经常包含电路内部生成的时钟。PT 支持用户通过命令create_generated_clock 定义生成时钟与源时钟之间的关系。

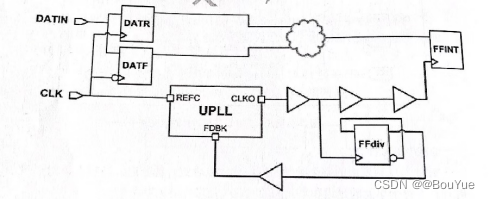

如上图所示,锁相环 (Phase -locked Loop, PLL)输出时钟 CIKO 的频率是PLL 参考时钟 REFC 的2倍。时序单元 FFdiv 用作分频器,将FLL输出时钟的频率降频到参考时钟频率。为了正确定义 PLL 的配置信息,需要用到生成时钟。命令如下:

create_ generated clock

-name CLK_pll

-source [get_pins UPLL/REFC]

-pll_output [get_pins UPLL/CLKO]

-pll_feedback [get_pins UPLL/FDBK]

-multiply_by 2

[get pins UPLL/CLK01

除了 PLL 的输出时钟,还需要定义时钟分频器 FFdiv 的输出。命令如下:

create_generated_clock

name pll_FDBK_clk

-source [get_pins UPLL/CLKO]

-divide_ by 2

[get_pins FFdiv/Q]

3.5门控时钟

随着功耗限制越来越成为设计的关键因素,设计人员经常采用门控时钟,即仅当需要时才使用时钟。当时钟网络包含反相器或缓冲器之外的其他逻辑时,门控时钟信号就会产生。比如,时钟信号是一个 AND 门的输入,某控制信号是AND 门的另一个输入,此时 AND 的输出就是门控时钟。如果不满足建立时间和保持时间要求,门控逻辑就会产生箍制时钟(cipped clock)或毛刺 (glitch)。

PT支持对门控逻辑指定建立时间/保持时间要求,命令如下:

set_clock_gating_check -setup <value>

-hole <value>

<object_list>

PT自动检查门控逻辑输人的建立和保持时间,确保控制信号能在时钟有效之前使能门控逻辑。当控制信息违规时,会产生毛刺或箍制时钟。

四、导出报告

4.1 生成约束报告 report_constraint

PT中的这个命令检查由设计者或工艺库定义的DRC(Design Rule Check)。另外,此命会对确定设计关于建立和保持时间违例的 “全面状况” 也是有用的。这个命令的语法以及最常用的选项如下:

report_constraint -all_violators -max_delay

-max_transition -min_transition

-max_capacitance -min_capacitance

-max_fanout -min_fanout

-max_delay -min_delay

-clock_gating_setup -clock_gating_hold

选项-all_violators显示所有约束的违例者。通常,这个选项用于快速地确定设计的全面状况。报告总结了对某一约束从最大到最小的所有违例者。

pt_shell> report_constraint -all_violators

选择性的报告可-max_transition 、-min_transition 、-max_capacitance、-min_capacitance、-max_fanout、-min_fanout、-max_delay 和-min_delay 等选项获得。-max_delay 和-min_delay 选项报告所有建立和保持时间违例的总结,而其他的则报告 DRC 违例。-clock_gating_setup 和-clock_gating_hold 选项用于显示门控时钟单元的建立/保持时间报告。此外,这个命令还有其他的可用选项,它们可能会对设计者有用。选项的全面细节可在PT用户指南中找到。

pt_shell> report_constraint -max_transition

pt_shell> report_constraint -min_capacitance

pt_shell> report_constraint -max_fanout

pt_shell> report_constraint -max_delay -min_delay

pt_shell> report_constraint -clock_gating_setup -clock_gating_hold

4.2 生成路径延迟报告 report_timing

类似于DC,这个命令用于生成设计中路径段的时序报告。这个命令被广泛使用并提供了充分的灵活性,这有助于明确地关注设计中单个路径或路径集合。

report_timing -from <from list> -to <to list>

-through <through_list>

-delay_type <delay_type>

-nets -capacitance -transition_time

-max_paths <value> -nworst <value>

-from 和-to选项使用户易于为分析定义路径。因为可以有多条从起点到终点的路径,-through 选项可用于为时序分析进一步分离所需的路径段。

pt_shell>report_timing -from [all_inputs] -to [all_registers -data_pins]

pt_shell>report_timing -from inl -to blockA/subB/carry_regl/D -through blockA/mux1/A1

-delay_type选项用于指定终点处报告的延迟类型,它可以按受的值是 max、min、 min_max、 max_ rise、 max_fall 、min_rise、and min_fall。 **PT 默认使用 max类型,它报告两点间的最大延迟。min 类型选项用于显示两点之间的最小延迟。max类型用于分析设计的建立时间,而min 类型用于进行保持时间分析。**其他的类型不常用。

pt_shell> report_timing -from [all_registers-clock_pins] -to [all_registers-data_pins] -delay_type min

-nets、-capacitance 和-transition_time 选项是report_timing 命令最有用和最常用的选项。这些选项帮助设计者调试特殊的路径以追踪可能违例的原因**。-nets选项在路径报告中显示每个单元的扇出,而-capacitance 和-transition_ time 选项分别报告连线上的集总电容和每个驱动或负载引脚的转换时间(摆率)。**没有这些选项将导致时序报告中没有以上提及的信息。

pt_shell>report_timing -from in1 -to blockA/subB/carry_regl/D -nets -capacitance -transition time

-nworst 选项指定了为每个终点报告的路径数,而-max_paths选项为不同的终点定义了每个路径组报告的路径数。这两个选项的默认值都是1。

pt_shell>report_timing -from [all_inputs] -to [all_registers -data_pins] -worst 1000 -max_paths 500

对网表进行静态分析以检查时序违规,时序违例可包含建立/或保持时间违规。综合设计的重点在于最大化建立时间,因此会遇到非常少的建立时间违例(如果存在)。然而,保持时间违例通常会在这一阶段发生,这是因为数据相对于时钟到达时序单元的输入太快。

如果设计没达到建立时间的要求,除了以违例路径进一步优化为目标重新综合设计外,别无其他选样。这可包括组合违例路径或过度约束具有违例的整个子模块。然而,如果设计没达到保持时间的要求,在布图前阶段修正这些违例,或推迟这一步直到布图后。很多设计人员对小的保持时间违例倾向于使用后一种方法,由于布图前综合和时序分析使用统计线载模型,并且在布图前阶段修正保持时间违例可导致同一路径布图后建立时间违例。然而,如果线载模型真实地反映了布线后延迟,在这一步修正保持时间违例是明智的。在任何情况下必须注意的是,明显的保持时间违例应在布图前阶段修正,以最小化布图后可导致的保持时间修正的数目。

布图后步骤包括用反标注的实际延迟分析设计时序,这些延迟由提取版图数据获得。分析是在含有时钟树信息的布线后网表上进行的。

最后

以上就是热情蜜蜂最近收集整理的关于EDA16--STA静态时序分析--PT指令(二)一、初始化二、读入设计三、时序约束四、导出报告的全部内容,更多相关EDA16--STA静态时序分析--PT指令(二)一、初始化二、读入设计三、时序约束四、导出报告内容请搜索靠谱客的其他文章。

发表评论 取消回复