在同步电路设计中,各功能逻辑单元之间的数据传输由一个同步信号控制,这个执行统一指挥的信号就是时钟信号,因此需要在设计之初创建时钟,基于该时钟频率进行优化设计,使设计性能达到时序收敛的目的。

创建时钟

时钟信号为一个周期性信号,定义时钟需要包括以下主要信息:

(1)时钟源点

时钟源点可以根据情况定义为设计中一个端口,一个网络,也可以是一个逻辑单元的PIN脚。为端口时用[get_ports 端口名],为网络时用[get_nets 网络名],为PIN脚时用[get_pins 引脚名]。

(2)时钟周期

时钟周期定义为时钟的震荡周期,为时钟频率的倒数。时钟周期是时序分析中最基本的、最小的时间单元。用{-period period_value}表示

(3)时钟占空比

时钟占空比主要定义时钟高低电平在一个时钟周期内的分布情况。用-[waveform edge_list]表示

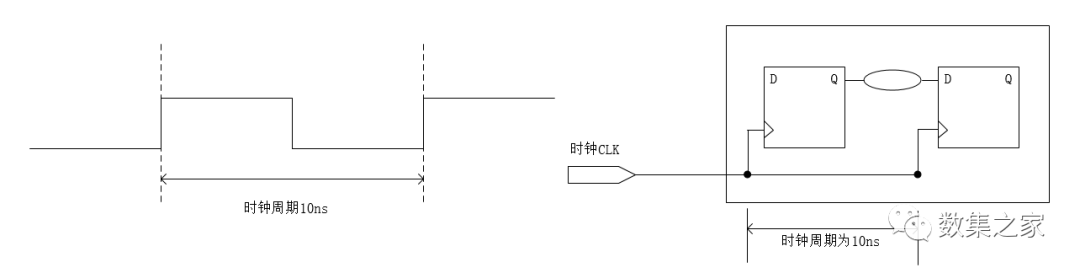

通过使用SDC命令creat_clock来创建时钟,比如通过该命令定义一个从CLK端口输出并且时钟周期为10、占空比为50%的时钟信号,命令如下。

creat_clock -period 10 -waveform { 0 5 } [ get_ports clk ]

如上图所示,该命令可以对所有内部触发器到触发器类型的路径进行约束。

(4)命名时钟

每个时钟定义都会给时钟信号命名。用 -name选项可以指定一个字符串作为时钟名称。当-name选项没有明确指定字符串并且时钟已被声明时,工具将指定自己的名字给时钟信号命名。时钟信号一旦被定义并且命名,所有其他依赖于此时钟信号的SDC指令只需要提到时钟信号的名称,而不用提供其他任何特征。当提到时钟信号名字的时候,时钟信号的所有特征就都知道了。时钟名称提供了更加简单的方法来统称时钟信号的所有特征。

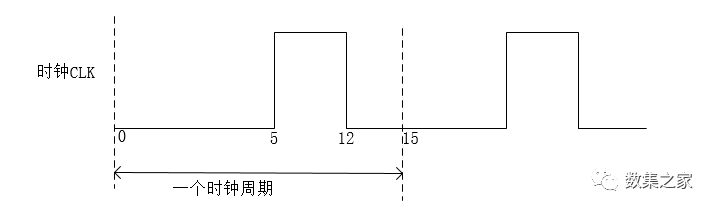

下面以定义一个占空比不是50%的时钟为例。

creat_clock -name BDYCLK -period 15 -waveform {5 12} [get_ports CLK]

时钟信号波形如下图所示。

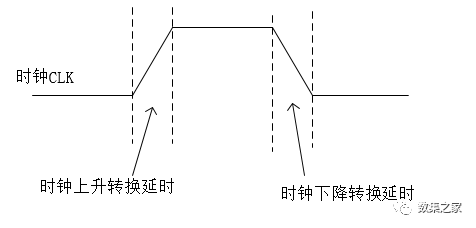

(4)时钟转换延时

时钟转换延时定义时钟在高低电平状态下切换所需要的延时。

通过SDC命令set_clock_transition来定义时钟转换延时信息,示例命令如下:

set_clock_transition -rise 0.1 [get_clocks clk]

set_clock_transition -fall 0.12 [get_clocks clk]

以上命令定义名为clk的时钟信号上升转换延时为0.1ns,下降转换延时为0.12ns。

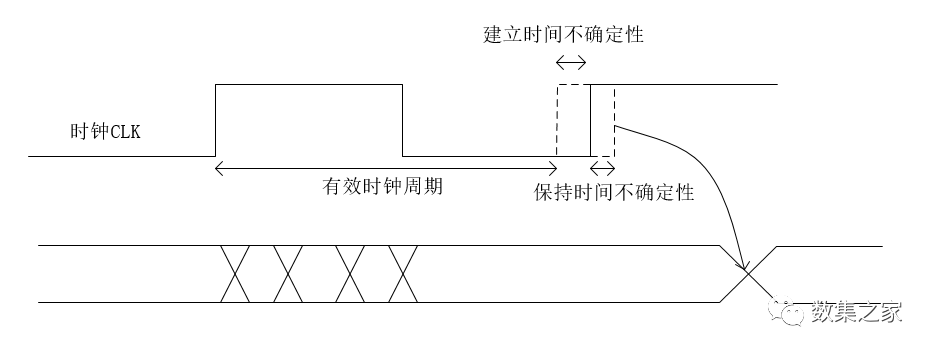

(5)时钟不确定性

由于实际时钟本身与理想时钟有一定的误差,所以通过时钟不确定来涵盖这些实际的导致误差的因素,比如时钟抖动、时钟偏斜等因素。

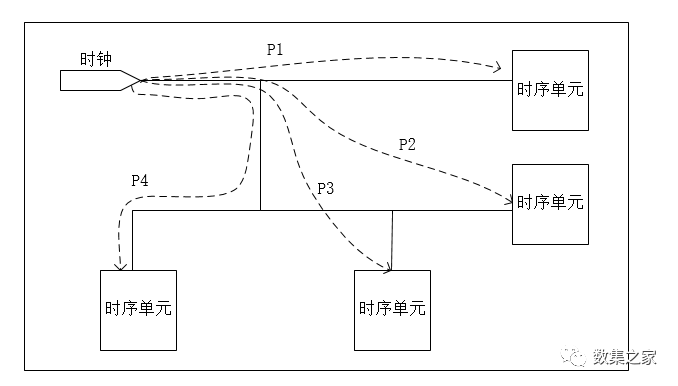

由于芯片内部各个触发器的位置不同,导致每个触发器到时钟源点的距离不相同,所以时钟源点的时钟信号到达每个触发器的时间与理想情况的时间有误差。如下图所示,假设路径P1的时间为0.5ns,路径P2的时间为1ns,路径P3的时间为1.2ns,路径P4的时间为1.3ns。那么,时钟不确定性的延时为0.8ns。

通过使用SDC命令set_clock_uncertainty来定义时钟不确定性信息,示例如下:

set_clock_uncertainty -setup 0.2 [get_clocks clk]

set_clock_uncertainty -hold 0.05 [get_clocks clk]

以上命令定义名为CLK时钟信号的不确定性为:建立时间为0.2ns,保持时间为0.05ns。其结果如下图所示。

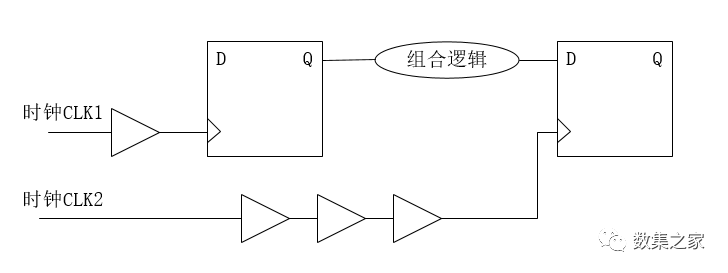

设计中可能存在由不同的时钟信号驱动的时序路径,如下图所示。

不同时钟域之间也可以定义时钟不确定性,示例命令如下:

set_clock_uncertainty -from CLK1 -to CLK2 -hold 0.05

set_clock_uncertainty -from CLK2 -to CLK1 -hold 0.05

set_clock_uncertainty -from CLK1 -to CLK2 -setup 0.1

set_clock_uncertainty -from CLK2 -to CLK1 -setup 0.1

以上命令定义名为CLK1和CLK2时钟之间的不确定性为:建立时间为0.1ns,保持时间为0.05ns。

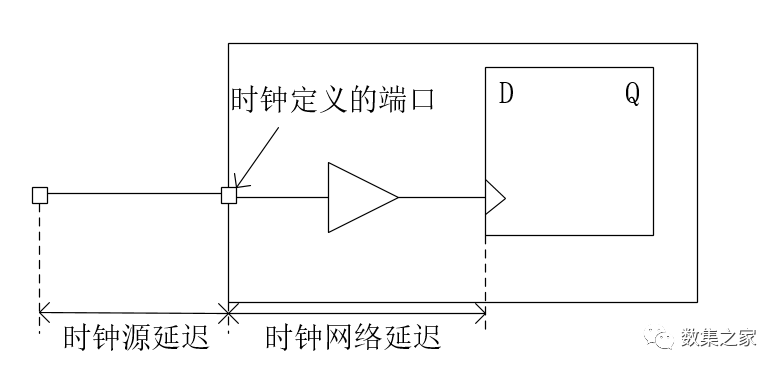

(6)时钟延迟

时钟信号从时钟源输出端到达时序单元时钟输入端是需要传播时间的。时钟延迟由时钟源点到达时钟定义的端口的延时(source latency)和时钟定义的端口到时序单元时钟输入端的延时(network latency)两部分组成,如下图所示。

通过使用SDC命令set_clock_latency来定义时钟延迟信息,示例命令如下:

set_clock_latency 1.8 -rise [all_clocks]

set_clock_latency 2.1 -fall [all_clocks]

以上命令定义了时钟网络延迟:上升延迟为1.8ns,下降延迟为2.1ns。

set_clock_latency 0.851 -source -min [get_clocks CLK]

set_clock_latency 1.322 -source -max [get_clocks CLK]

以上命令定义了时钟源信号到达时钟CLLK输出端的延时,最大延迟为1.322ns,最小延迟为0.851ns。

时钟网络延迟与时钟源延迟的一个明显区别是,时钟网络延迟是时钟树生成前的设置。当实际时钟树生成后,时钟网络延迟的设置将会通过命令set_propagated_clock被时钟树的实际结果替代,而时钟源延迟会一直存在,即使使用实际的时钟树传播延时信息。

最后

以上就是自觉御姐最近收集整理的关于时序约束之时钟约束01的全部内容,更多相关时序约束之时钟约束01内容请搜索靠谱客的其他文章。

发表评论 取消回复