最近在面试中经常遇到时序方面的知识,干脆做个总结,以后复习也方便

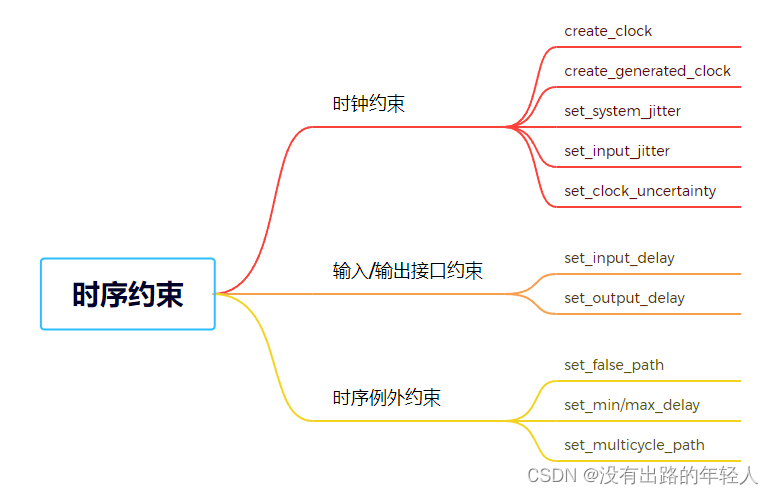

常见时序约束主要分为三类:时钟约束,输入/输出接口约束,时序例外约束。

create_clock主要是对主时钟进行约束定义,帮助时序分析工具定义时序路径分析的一个时间零点,时钟传输过程中的延时和不确定性也都会基于这个时间零点进行计算和分析。

create_generated_clock主要是对衍生时钟约束,衍生时钟主要是指由已有的主时钟进行分频,倍频或相移出来的时钟信号,比如MMCM等。衍生时钟并不直接定义频率,占空比等参数,而是定义其与时钟源的相对关系,如分频系数,倍频系数,相移差值,占空比差值等。

set_input_jitter更改某个时钟信号的默认时钟抖动值,指定时钟的峰峰抖动值,但只能约束主时钟的抖动值,且每条指令只能约束一个主时钟。

set_system_jitter是对系统抖动进行定义,主要用于系统电源存在较大噪声,比如器件内核电压VCCINT由于大量节点同时开关,串扰,温度突变等因素导致。

set_clock_uncertainty是对除时钟抖动以外的所有可能影响时钟周期性偏差的因素进行约束。

虽然使用set_system_jitter和set_input_jitter命令约束的抖动值最终都会计算到时钟不确定性时间中用于时序分析,但使用set_clock_uncertainty命令约束的时钟不确定性值并不会影set_system_jitter和set_input_jitter命令约束的抖动值,而是在他们之外,额外增加约束值计算到时钟不确定时间中用于时序分析。

set_clock_latency是对时钟延时值的设置,主要用于外部芯片输入时钟情况即源同步接口,通常也把这个延时计算到input_delay中。

set_input_delay用于指定输入数据引脚相对于其时钟沿的路径延时,主要用于数据路径中的pin2reg,分析从外部芯片到自己内部寄存器的延迟,需要满足自己芯片内部寄存器的建立保持时间 ,设定的最大值和最小值分别用于建立和保持时间分析。

set_output_delay用于指定输出数据引脚相对于其时钟沿的路径延时,主要用于数据路径中的reg2pin,分析从自己内部寄存器到外部芯片的延迟,需要满足外部芯片中寄存器的建立保持时间,设定的最大值和最小值分别用于建立和保持时间分析。

时序例外约束可以对某些路径放宽时序要求,减少对布局布线资源的占用,从而尽可能多地释放出宝贵的资源给时序约束要求较高的关键路径,合理分配资源,能够更好的确保整个系统的时序收敛。

set_multicycle_path指定从起始时钟沿到目标时钟沿所需的时钟周期数。常用于放宽某些时序路径的时序要求。

set_false_path指定在设计中不做分析的时序路径,即在布局布线中可以作为最低优先级的路径。

set_min/max_delay主要用于数据路径中pin2pin,具体如何确定取决于实际的应用。

时序约束的推荐顺序:

- 主时钟约束

- 虚拟时钟约束

- 衍生时钟约束

- I/O约束

- 虚假路径约束

- 最大/最小延时约束

- 多周期约束

最后

以上就是疯狂悟空最近收集整理的关于时序约束概述常见时序约束主要分为三类:时钟约束,输入/输出接口约束,时序例外约束。时序约束的推荐顺序:的全部内容,更多相关时序约束概述常见时序约束主要分为三类:时钟约束,输入/输出接口约束,时序例外约束。时序约束内容请搜索靠谱客的其他文章。

发表评论 取消回复