第四课

Timing constraints

最后需要完成DC能够读入的tcl脚本

setup_timing

目标:定义时序电路中所有路径的时序约束,约束分为三个部分:

1.input logic paths

2.internal paths

3.output paths

约束具体取决于芯片的spec,工艺等。

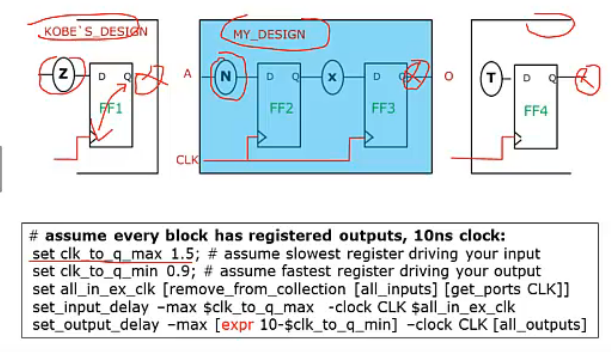

DC默认的外部环境是由同步时钟驱动的:1.输入信号由posedge驱动的器件产生,2.输出信号将输出至posedge驱动的器件。

- timing path

综合过程中软件会把电路分为一个一个path(路径),每个路径都有start point和end point。

Start point:Input port或者Clock pin of flip-flop or register

End point:output port或者any input pin of a sequential device, except clock pin

Timing Constraints

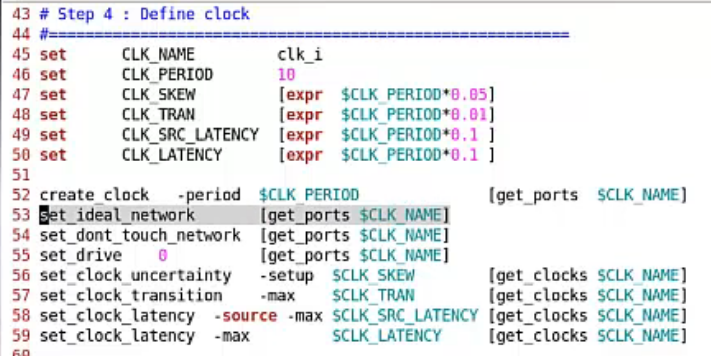

- Clock

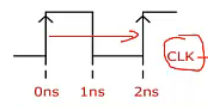

clock period:时钟的周期约束。默认情况下单位是ns,50%占空比,并且会设置成理想的时钟:

create_clock -period 2 [get_ports clk]

clock skew:同一个时钟对不同时钟接收端的最大延迟,其中包括clock jitter和margin的影响。

set_clock_uncertainty -setup Tu [get_clocks clk]

latency:从晶振到模块内时钟信号的延迟。

transition:边沿升高/下降需要的时间。

set_clock_latency -source -max 4 [get_clocks clk] //有-source表明是模块外的延迟,没有则指模块内的延迟。

set_clock_latency -max 2 [get_clocks clk]

set_clock_transition Tt [get_clocks clk]

**设计DDR的时候时钟的占空比会很重要。

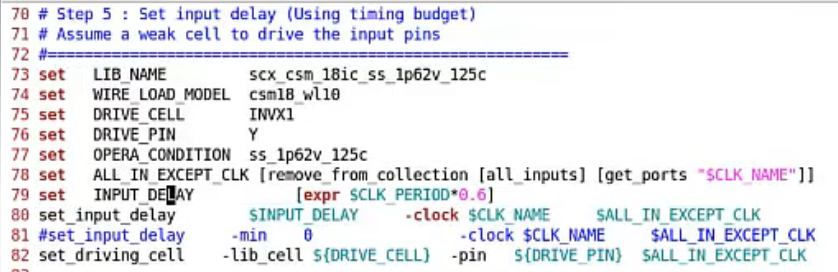

- Input

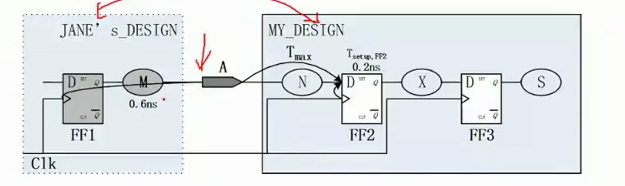

Input delay:表示外部驱动输入信号的时钟到输入信号端口之间的延时,延时是相对于CLK而言,也就是下图中组合电路M的延时。

set_input_delay -max 0.6 -clock Clk [get_ports A]

设置input delay之后DC会优化N的延时,以满足STA的要求。

clock端口是不需要设置input延迟的

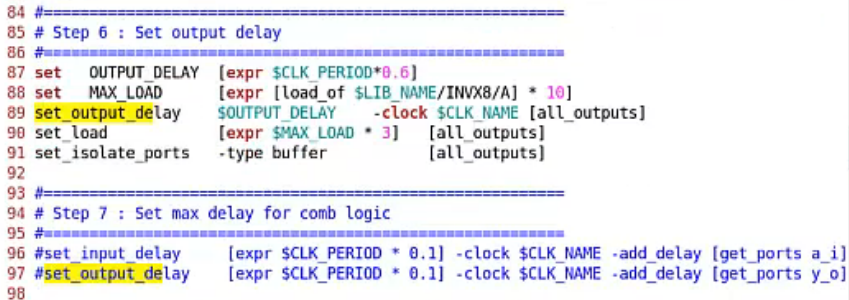

- Output

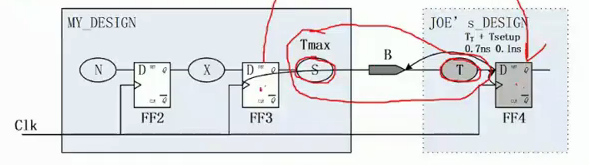

output delay:表示从输出端口到捕捉输出的时钟边沿到来之间的最大延时,也就是下图中组合电路T的延时。

set_output_delay -max 0.,8 -clock Clk [get_ports B]

若是已经做好的芯片,通常在数据手册中可以找到,若是自己设计会在顶层架构时定好;具体的数值来源于计算,经验以及使用的工艺。

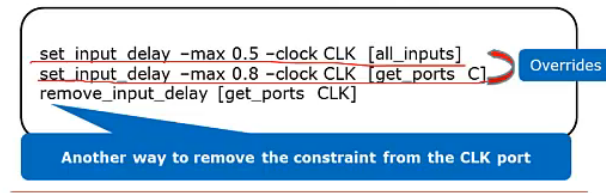

注:若同时写了两种相同类型的约束,那么后一个约束会覆盖前一个约束。

- Combinational path

在对组合电路设置时序时,是无法直接对其添加约束命令的,而是通过对前后寄存器的输入和输出添加约束,从而使DC自动计算出两个寄存器之间组合电路可以接受的最大延时,对其进行优化。

Q:那么对一个纯组合电路该如何施加约束?(即模块内没有寄存器和CLK时钟)

A:创建一个虚拟时钟(virtual clock)。

create_clock -name VCLK -period 2

虚拟时钟不连接在任何port或者pin上,仅仅作为input delay和output delay的参考点。

- Time Budget

当不知道模块的输入输出延时时,可以建立时间预算(Time budget)。

也就是在设计模块时,让输入输出延时额外多出一部分,占到时钟周期的50%以上,这样就可以在连接模块时留出足够的时间余量。

’注:尽量定义输出为reg类型,有利于延时的计算。

总结

需要告诉DC的信息:

1.时钟周期→DC知道寄存器和寄存器之间的最大延时

2.输入端口和输出端口的外部电路的延时→根据CLK知道输入端口所对应的,模块内部可以允许的最大延时

实例

1.已经执行过综合之后,需要清理当前DC内存中的所有设计:

remove_design -hierarchy

执行命令以后再用list_designs可以查看,发现内存当中已经没有设计了。

2.检查代码是否还有问题(例如递归、连线错误):

check_design

返回0表示存在不可接受的错误,返回1表示存在可以接受的问题。

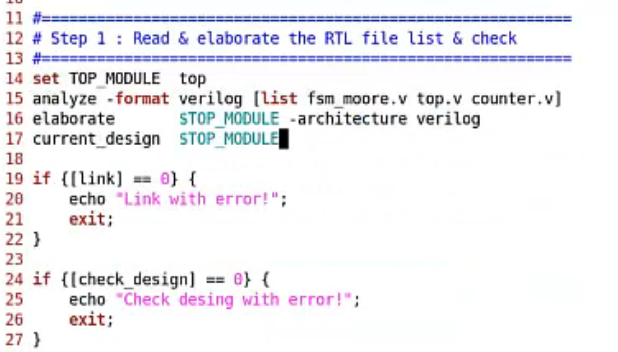

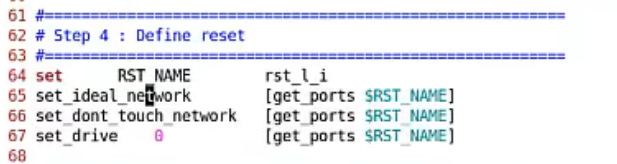

以上操作写成脚本如下所示:

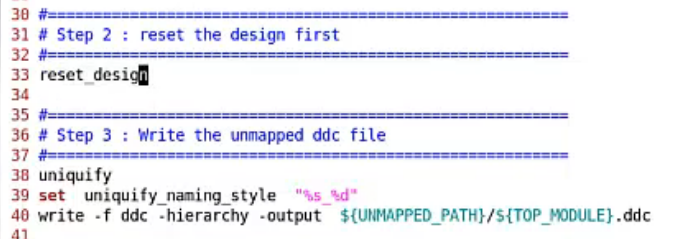

3.确保本次添加的约束干净,则可以使用以下命令清除之前添加的所有约束:

reset_design

4.开始利用前面所学的命令给时序路径添加约束

所有的路径都必须添加约束(除了跨时钟电路 )

检查是否有漏掉的路径可以用以下命令:

check_timing

- 检查tcl脚本的语法错误

dcprocheck ../script/xxx.tcl

最后

以上就是复杂月亮最近收集整理的关于DC 视频教程 第四课的全部内容,更多相关DC内容请搜索靠谱客的其他文章。

发表评论 取消回复