VerilogHDL程序设计与仿真作业7:

——实现74HC/HCT194的双向移位寄存器功能

文章目录

- VerilogHDL程序设计与仿真作业7:

- ——实现74HC/HCT194的双向移位寄存器功能

- 一、实验目的

- 二、实现74HC/HCT194的功能

- 1、设计思路

- 2、实现代码

- 3、测试代码

- 4、仿真

一、实验目的

- 实现74HC/HCT194的双向移位寄存器功能

二、实现74HC/HCT194的功能

1、设计思路

-

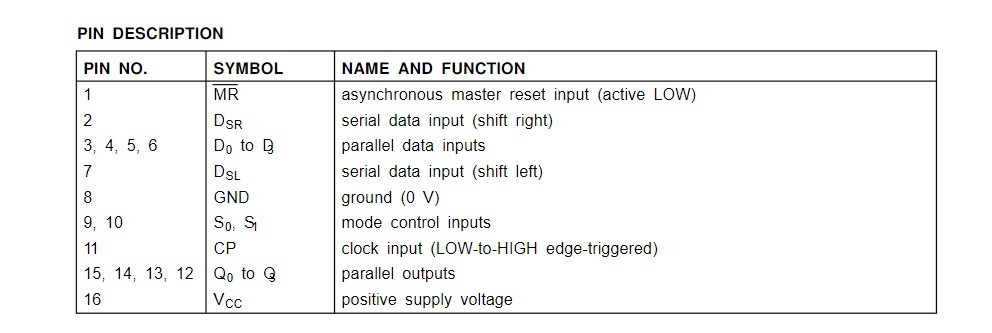

74HC/HCT194的引脚定义

-

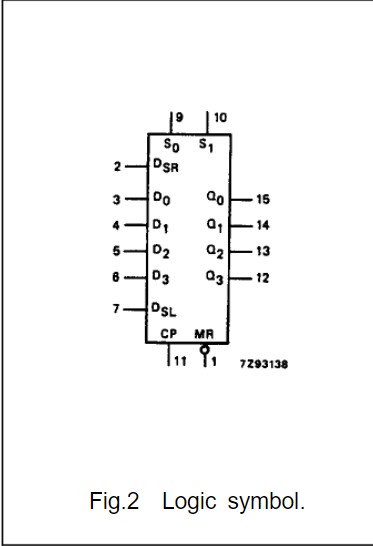

74HC/HCT194逻辑符号

-

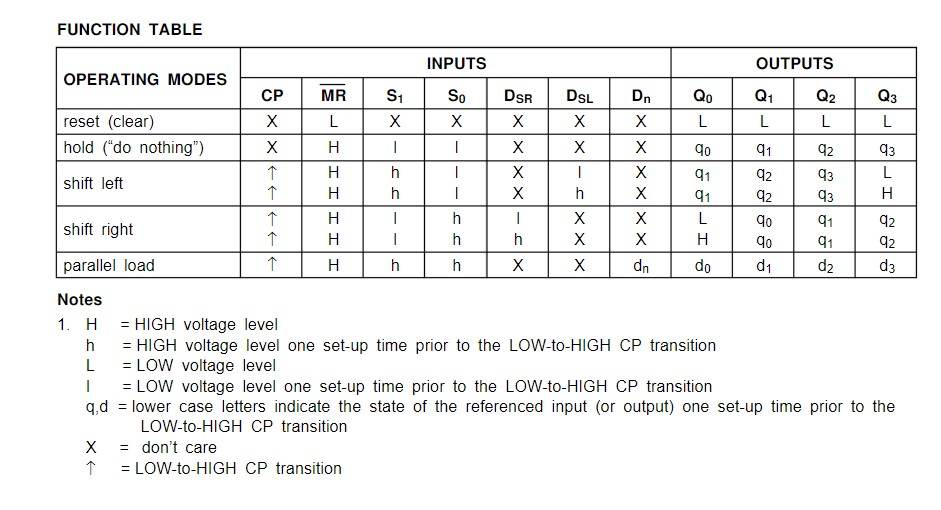

74HC/HCT194的功能表

2、实现代码

//文件名称:_74HC194.v

//fuchaoxinHUST12102020

module _74HC1194(CP, MR_, S, D, DSR, DSL, Dn, Q);

input CP,MR_;

input [1:0] S;

input [3:0] D;

input DSR, DSL;

output reg [3:0] Q;

/*说明:

输入端:CP为时钟信号,上升沿敏感;MR_为异步置零端;DSR右移串行输入数据;DSL为左移串行输入数据;[3:0] D为并行输入数据;

S为控制信号,当[1:0] S=00时,锁存;[1:0] S=01,输出右移;[1:0] S=10,输出左移;[1:0] S=11,并行置数;

输出端:[3:0] Q为输出信号

*/

always @(posedge CP or negedge MR_) begin

if(negedge MR_) begin

Q = 4'b0000;

end

else begin

case ([1:0] S)

2'b00: Q <= Q;

2'b01: Q <= {Q[2:0], DSR} //输出信号右移,右移串行输入数据移动至输出信号的右侧

2'b10: Q <= {DSL, Q[3:1]} //输出信号左移,左移串行输入数据移动至输出信号的左侧

2'b11: Q <= D;

endcase

end

end

endmodule

3、测试代码

//文件名称:Test_74HC194.v

//fuchaoxinHUST12102020

`timescale 10ns/1ns

module Test_74HC194;

reg CP, MR_, DSR, DSL;

reg [1:0] S;

reg [3:0] D;

wire [3:0] Q;

_74HC194 U0(CP, MR_, S, D, DSR, DSL, Q);//实例化元件

initial

$monitor($time,":t MR_=%b, S=%b, D=%b, DSR=%b, DSL=%b, Q=%b n", MR_, S, D, DSR, DSL, Q);

//监视器的显示内容

initial

CP = 0;

always

#1 CP = ~CP;

initial begin

// 预置1111

MR_=1; S=2'b11; DSR=1; DSL=1; D=4'b1111;

#2

// 清零

MR_=0; S=2'b11; DSR=1; DSL=1; D=4'b1111;

#2

// 右移置数,DSR=1

MR_=1; S=2'b01; DSR=1; DSL=1; D=4'b1111;

#2

// 右移置数,DSR=0

MR_=1; S=2'b01; DSR=0; DSL=1; D=4'b1111;

#2

// 清零

MR_=0; S=2'b11; DSR=1; DSL=1; D=4'b1111;

#2

// 左移置数,DSR=1

MR_=1; S=2'b10; DSR=1; DSL=1; D=4'b1111;

#2

// 左移置数,DSR=0

MR_=1; S=2'b10; DSR=1; DSL =0; D=4'b1111;

#2

// 保持

MR_=1; S=2'b00; DSR=1; DSL=1; D=4'b1111;

#2

$stop;//停止模拟仿真

end

endmodule

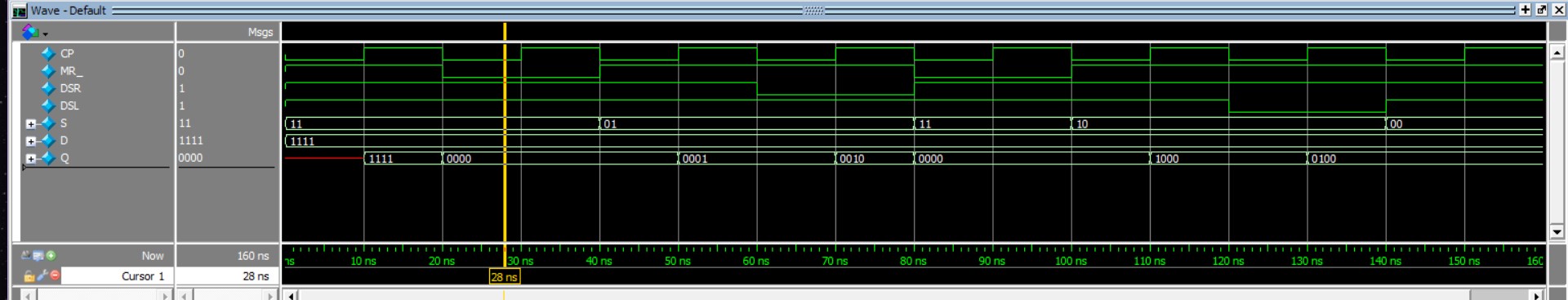

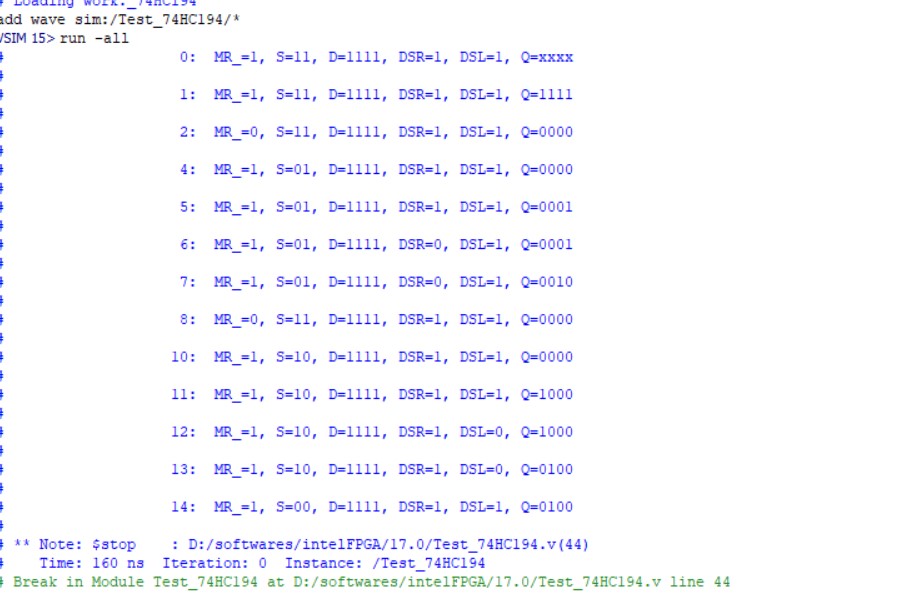

4、仿真

- 波形

- 监控器

最后

以上就是安详背包最近收集整理的关于实现74HC/HCT194的双向移位寄存器功能VerilogHDL程序设计与仿真作业7:的全部内容,更多相关实现74HC/HCT194内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复