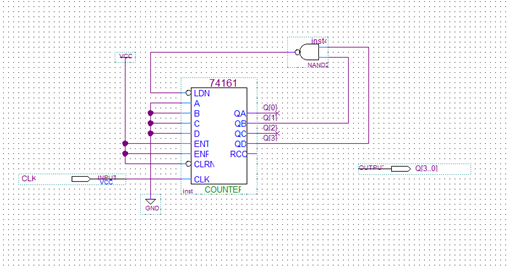

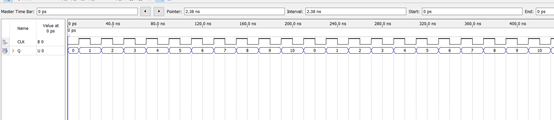

1、 使用74161设计一个可预置的任意进制计数器,使用QuartusII 完成创建工程、编辑电路图、编译,编辑波形文件仿真,记录波形并说明仿真结果,最后在FPGA上进行硬件测试。

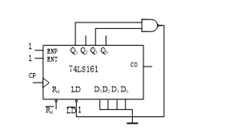

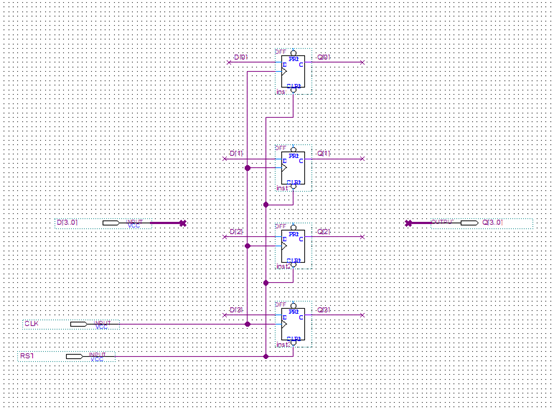

原理:如图所示。预置数为0000,当计数输出端计数到1010时,置数端有效。在CLK下一个上升沿到来时,输出状态转为预置数状态0000,置数端无效,所以计数器继续正常计数,直至再次计数到1010。如此循环,即可实现从0000到1010周期性变化的十一进制计数器。

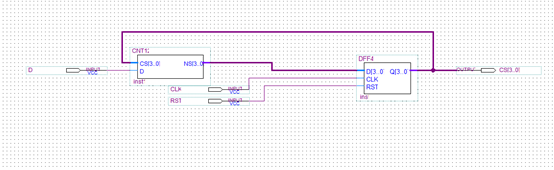

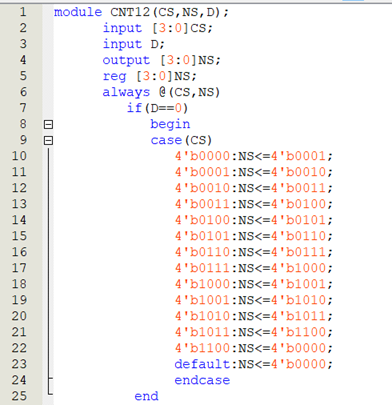

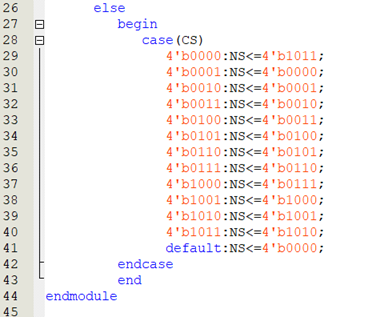

2、根据计数器设计的一般模型,设计一个十二进制加减法计数器。使用QuartusII创建工程、创建电路图、编译,编辑波形文件并仿真,记录波形并说明仿真结果,最后在FPGA上进行硬件测试。

附上源码-模为12的加减法可预置计数器(因为从报告导入,选择截图的方式)

最后

以上就是激动毛豆最近收集整理的关于74161-可预置任意进制计数器(基于QuartusII实现)的全部内容,更多相关74161-可预置任意进制计数器(基于QuartusII实现)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复