数字逻辑电路分为组合逻辑电路和时序逻辑电路,组合逻辑的分析与设计我已经写过,今天来简单写下时序逻辑分析和设计的基本方法。

时序逻辑电路的分析与设计

- 时序逻辑分析

- 时序逻辑设计

- 总结

时序逻辑分析

所谓分析,就是从电路图到功能。

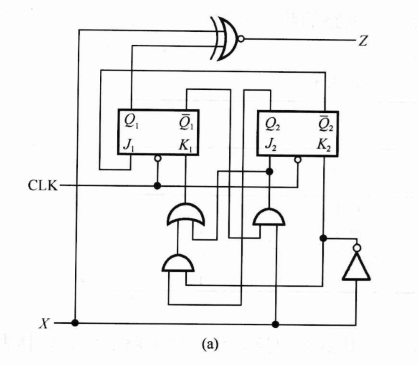

首先给出我们电路图。举个例题

ok这个图就是一个完整的时序逻辑电路,如何分析它呢?

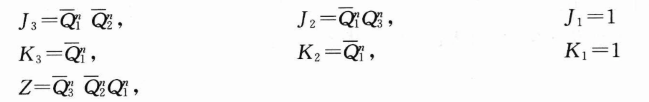

第一步:写三大方程。

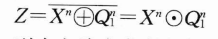

先写输出方程(指的是最终输出,注意里边都写n次幂)

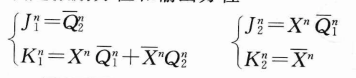

再写激励方程(如果有的话)(当触发器的D,J,K端等表达式是组合电路时才需要,否则不需要,这一步需要明白各种类型触发器的标准方程)

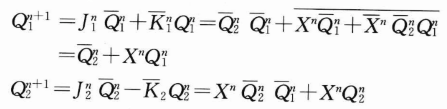

最后写次态方程(Q的次态和Q的现态的关系)

写完三大方程,我们就把这个电路图数字化(公式化)了。

第二步:画表

方程的好处是精准,给我们任意时刻一个状态,我们能套公式算出下一个信号后的状态,但是每次都计算实在是太麻烦了,如果能一眼看出来状态之间的转换关系就好了。因此我们需要画表。

画什么表?有几种类型:

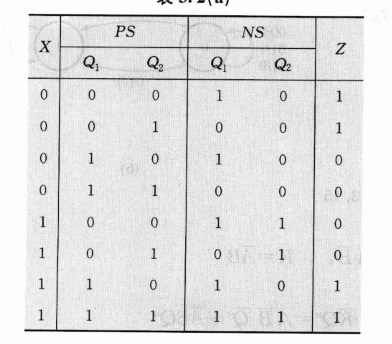

1)状态转移(真值)表:

每一行都分别是输入/现态/次态/输出。看着很清晰,对吧。

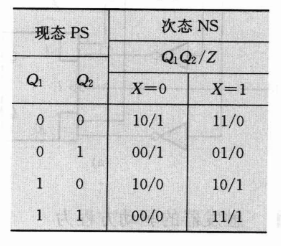

2)状态表

表达的信息和状态转移真值表相同,只是画的方式不同而已。

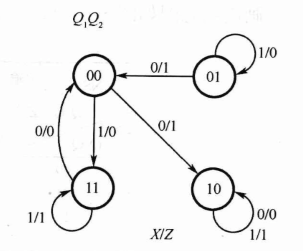

第三步:画图

表是很直观,但是我们还有更直观的工具——图!

通过状态转移图,我们可以很清晰地看出状态之间的变化。分析到这一步,一个时序逻辑电路可以说是一目了然了。

时序逻辑设计

设计,就是从功能到电路。举个例子。

OK,告诉了我们功能就是实现这个图,我们需要设计一个时序逻辑电路。有几个步骤:

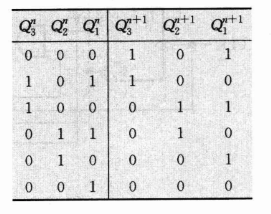

第一步:可以画个表

第二步:通过卡诺图的帮助,写三大方程

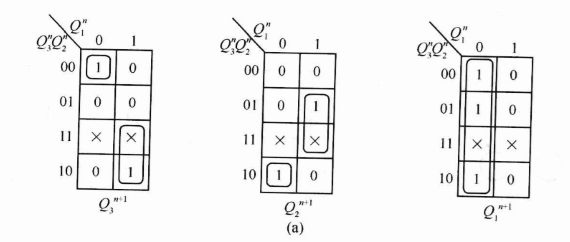

三大方程我们在时序逻辑分析中已经讲过了,就是输出方程,激励方程和状态方程。注意:我们先写状态方程,也就是现态和次态的关系。怎么写?利用卡诺图,有三个次态,我们对每个次态都画一个卡诺图。

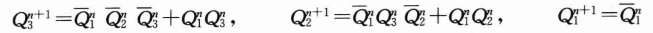

OK,利用卡诺图化简得到次态表达式

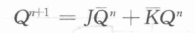

假设我们用JK触发器实现,我们知道JK触发器的标准方程

和上边求出的状态方程对照,我们就知道了1,2,3三个次态各自的J1,K1,J2,K2,J3,K3了。

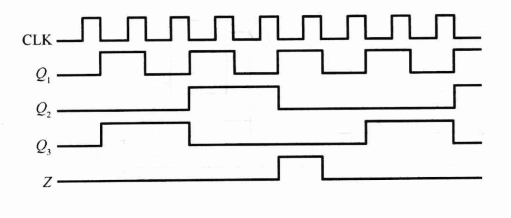

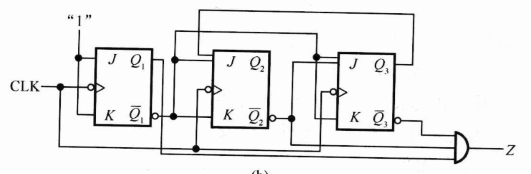

第三步:画电路图

设计的最终目的一定是得到实际电路。画时序逻辑电路要按照一定的顺序去画,比如个人的习惯是先画时序部分,触发器摆开,CLK信号接上,然后画激励也就是JK,画完之后在整个电路最下边画出输出电路(输出电路本质上是个组合逻辑电路)。最终分为上中下三层——上层是触发器,中层是CLK信号,下层是输出组合逻辑电路。

总结

时序逻辑电路让我们数字机器有了“存储信息”的能力,是计算机硬件的底层实现。

最后

以上就是开朗银耳汤最近收集整理的关于时序逻辑电路的分析与设计时序逻辑分析时序逻辑设计总结的全部内容,更多相关时序逻辑电路内容请搜索靠谱客的其他文章。

发表评论 取消回复