文章目录

- TTL门电路

- 回顾前面几种门电路

- 双极型三极管

- TTL反相器

- 静态输入特性和静态输出特性

- 输入端负载特性

- 其他参数(CMOS也适用)

- 尖峰电流

- 其他TTL门电路

- 其他逻辑功能的门电路

- OC门

- 三态门

- 第三章整体需要额外精读

- 本章小结

TTL门电路

!!对于电子电路,首先要定性得决定器件工作在哪个区域,然后选对正确的模型,然后再分析才可能有正确的结论。

回顾前面几种门电路

- CMOS门电路的基本原理

- 反相器,其他逻辑CMOS电路构成

C:利用了NMOS和PMOS的互补性,而天生的构成了上拉和下拉部分的电路带来的CMOS工艺。在构成的过程中,利用了电路原理的串并结构代替与或结构,直接可以构成其他逻辑运算的CMOS门电路。 - OD门:D指漏极开路,要解决线与,使用时需要上拉电阻,接外电源

- 三态门:实现了高阻态,即实现了物理上连接而电气上不连接的可能(应用:总线)

除了CMOS门电路,还有一小部分市场份额是TTL门电路,这个部分越来越小。

双极型三极管

!!!三极管和MOS管最大的区别是:三极管是电流驱动的。

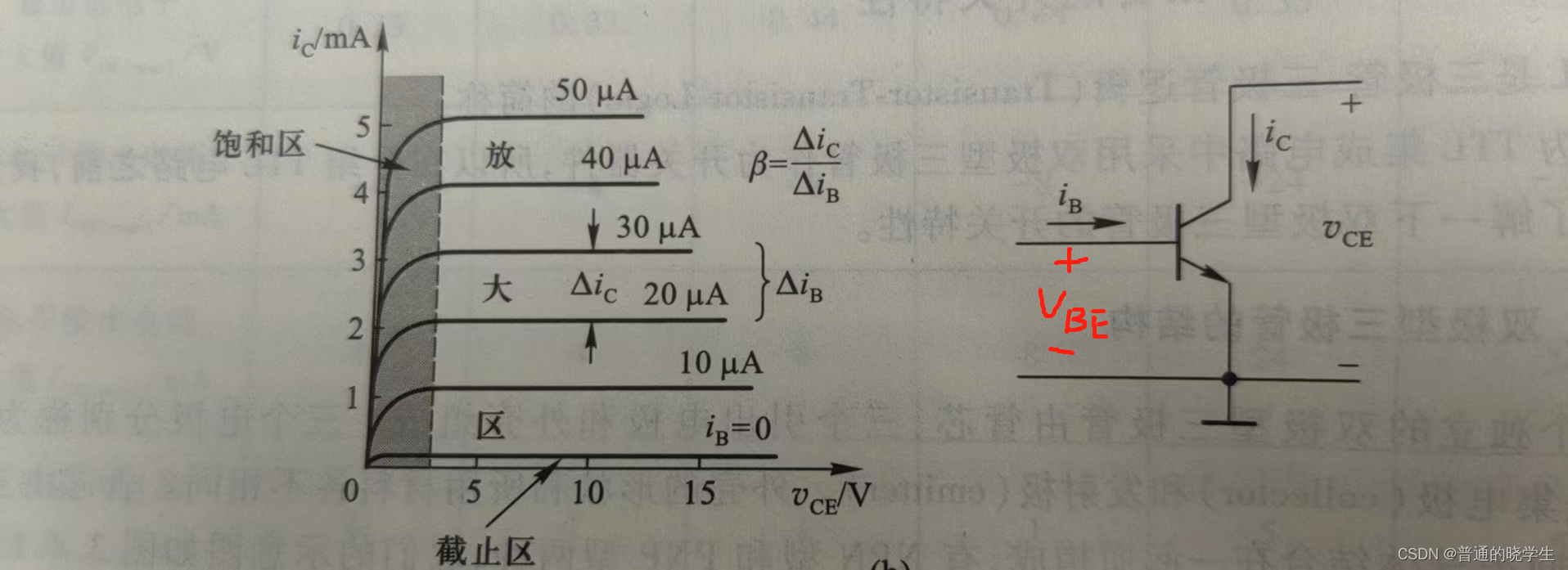

- 输出特性

输出特性曲线分为三个部分:

- 截止区:Vbe = 0,ib = 0,ic = 0

- 放大区:Vce > 0.7V,ib>0,ic随ib正比变化

- 饱和区:Vce < 0.7V,ib>0,Vce很低,ic随ib变化变缓,趋于饱和

电流放大系数β不由电压决定,由掺杂浓度和各个极的面积大小决定(集电极面积最大,发射极掺杂浓度最高,基极做的最薄最小)

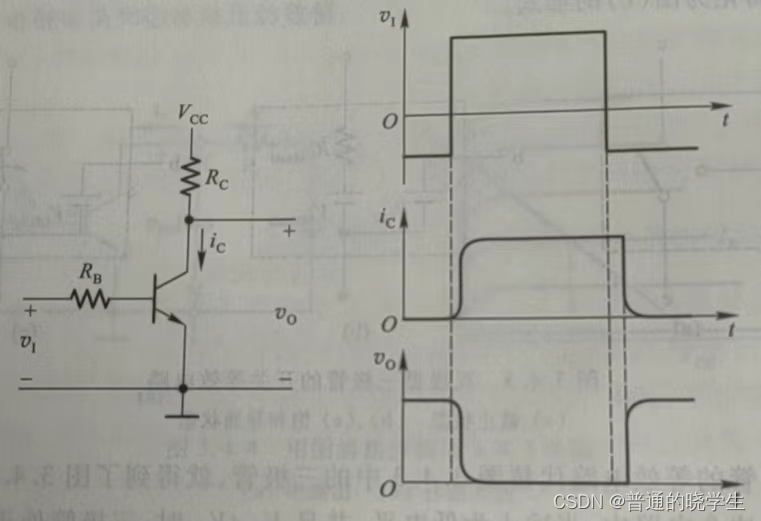

!!!!模电中,我们想让它工作在放大区,这叫做工作点确定,希望有功率放大的特性。而在数电中,我们想用饱和区和截止区。总结:数字电路和模拟电路用到一样的器件,在模拟电路中,我们用线性区,在数字电路中,我们用非线性区,当开关用

- 当想输出低电平时,让三极管工作在截止区

- 当想输出高电平时,让三极管工作在饱和,因为如果是深度饱和,压降可能只有0.1V,0.2V

- 动态开关特性

滞后现象都是由于结电容效应

TTL反相器

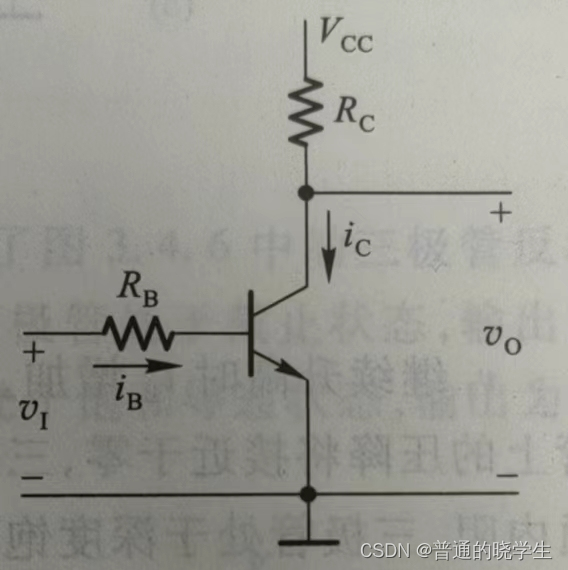

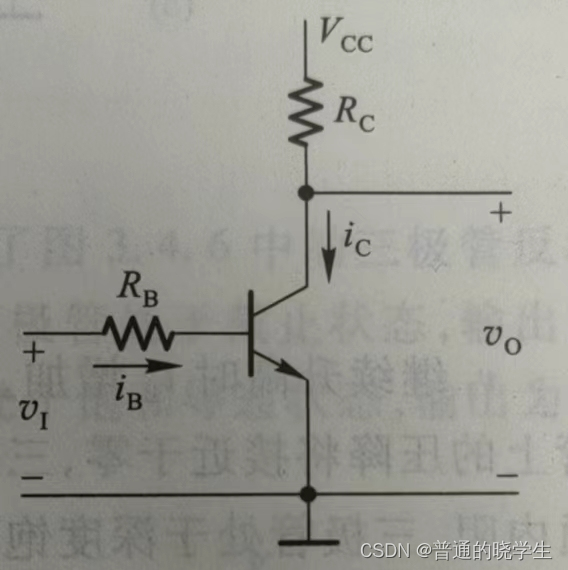

- 用三极管当成反相器并不理想:

因为低电平不能有一个大的变化范围,只能在0.7V以下,再高就可能导通

- TTL反相器

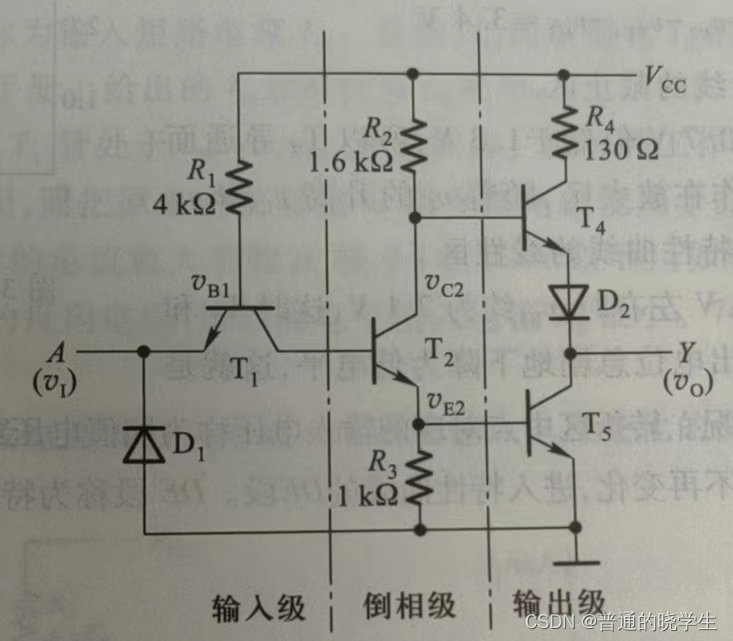

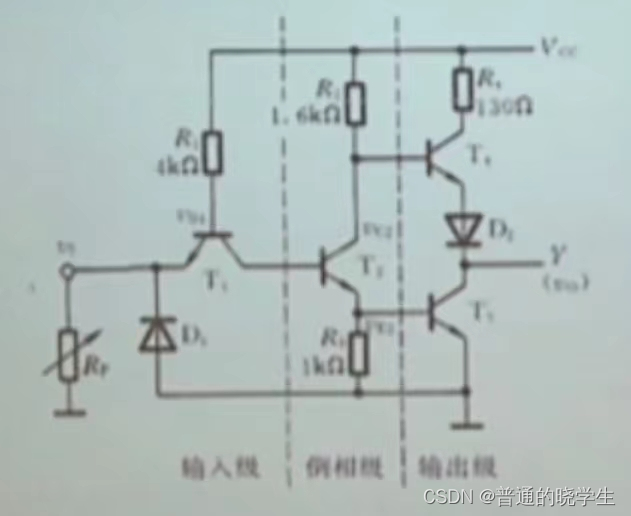

下图是TLL反相器的经典设计,一直用到现在

- 这个电路并不是工程师用笔算出来的,而是抱着要设计一个反相器,这个反相器是对前面电路的一个改进,实际是要提高前面电路的输出能力,要把电阻去掉,提高电路的输入阻抗,刚刚那个电路如果要进饱和,要减小Rb,所以电路输入功耗也比较大。

- 对于一个电压信号的传递者来讲,输入端对于前端来讲,最好做到不取电流,取也是取小电流;对于后端来讲,应该做到输出电阻比较小

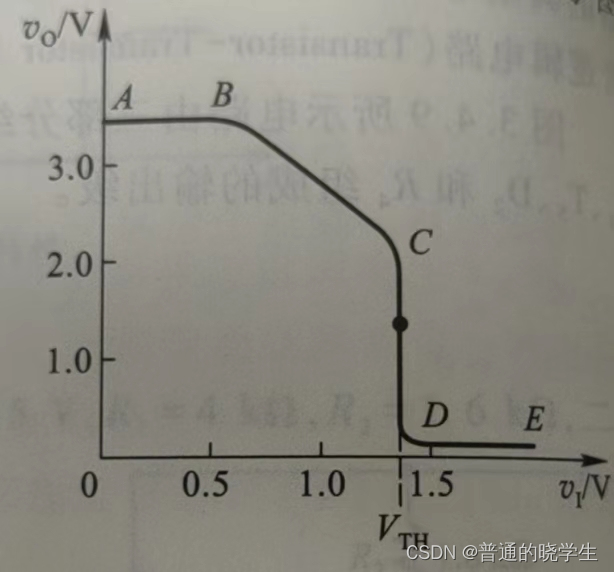

输出特性:

首先来看,这个曲线特性没有CMOS的曲线特性好。AB和DE比较满意,但是BC和CD是明显的线性区。

- AB段中,输入有变化,输出基本没变化,但是输出即便没变化,这个输出也只有3.几V,并没有能力把5V直接接出来,采用了一个设计跟随输出(设计跟随输出的特点:输出电阻小),设计跟随意味着负载增加,电压能坚持一段时间。

- DE段中,输出是低电平,是T5管饱和导通的状态

- 所以这个电路和CMOS的想法一致,仍然想上拉出一个高电平,下拉出一个低电平

开始分析:(重点)

- AB:截止区 Vi < 0.6V,所以Vb1 < 1.3V,T1导通,T2,T5截止,T4导通

- T1为什么在饱和区?

R1是4K欧,而T1右边等效的电阻很大,所以T1很容易进入饱和区,所以,T1的压降很小。

- BC:线性区 0.7V < Vi < 1.3V,T2导通且工作在放大区,T5截止,T4导通,Vi增大=>Vo减小

- CD:转折区 Vi = Vth 约等于1.4V,所以Vb1>=2.1 V,T2,T5同时导通,T4截止,所以Vo迅速下降,Vol约为0

- 当Vi大于1.4V是,集电极电压不会跟着Vi上升了,因为T2和T5都导通了,集电极电压就是1.4V,这时,基极电压是多少?

这时,集电极电压比发射极低,现在集电极正偏,发射极反偏,管子处在倒置的工作状态,这时,两个PN结各自为政,这时基极的电压始终被控制在2.1V,输出再升高也没有有影响,这就得到了DE段

- DE:饱和区 Vi继续增大,而Vo不变

需要说明:

- T2的输出Vc2和Ve2变化方向相反,故称倒相级

- 输出级在稳态下,T4和T5总有一个导通,一个截止,既能降低功耗又提高了带载,称推拉式

- D1抑制负向干扰;D2保证T5导通时T4可靠截止

输入噪声容限:

输入大于1.4V就是高,和能输出的3.4V直接就是噪声容限

同理,输出低电平也可以界定一个容限

需要注意:

- 拿到一个器件,有一个特性曲线,如果不统一思想,每个人可以取出自己的噪声容限,而这个噪声容限就是系统之后工作的一个特性曲线

- 在整个系统中,如果器件是直接级联,那么他们的噪声容限应该按照最差的来

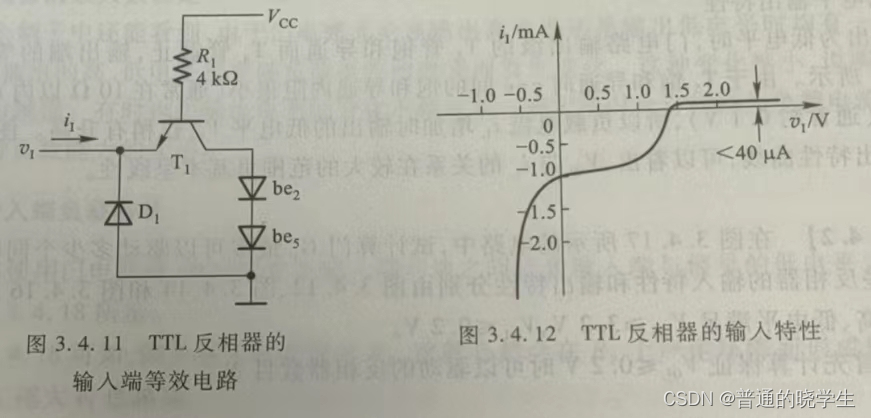

静态输入特性和静态输出特性

输入特性:

- Vi = Vil = 0.2V,Iil约为0.1mA,是流出的

- 当Vi = Vih = 3.4V,T1发射结反偏,Iih很小

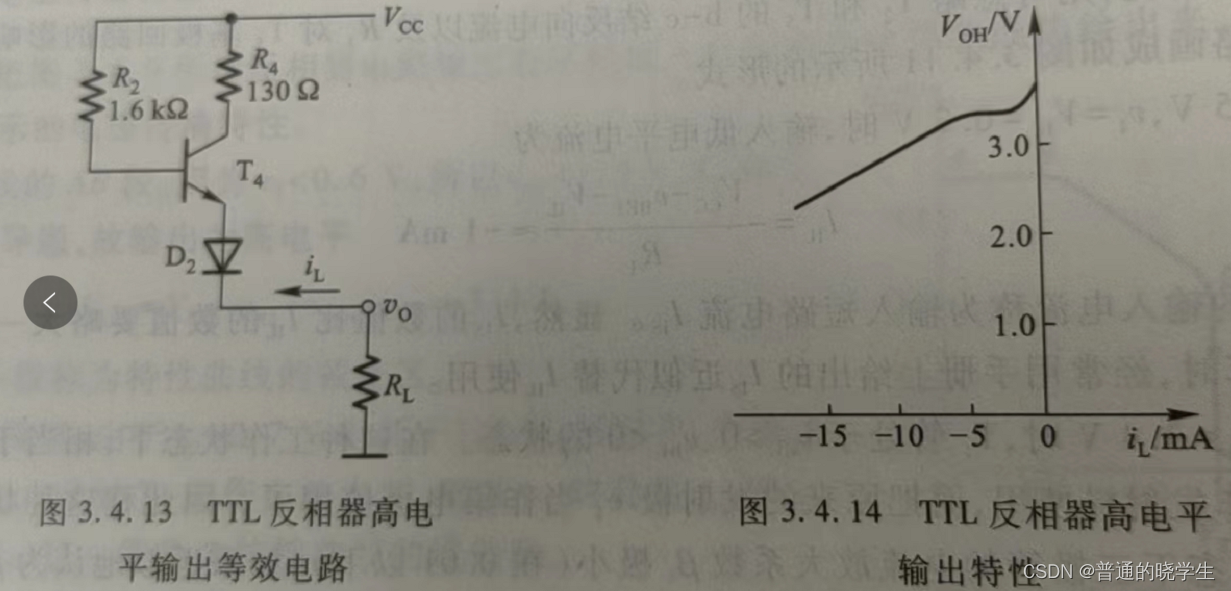

输出特性:

(高电平时)是设计跟随输出,输出电阻小

- 有图下凹的区是T4设计跟随给出的电压补偿能力,当输出因为负载增加,D2下面电压要下降的时候,这时T4导通,T4会把本身压降吐出来,从放大开始往饱和走

- 当负载持续增大,这时T4已经饱和,没有放大能力,等效成一个电阻

但是我们在用的时候不会让它工作在这些区,我们设计这个的时候是从功耗的角度考虑的,输出高电平时带的负载不能太大,因为太大器件受不了。

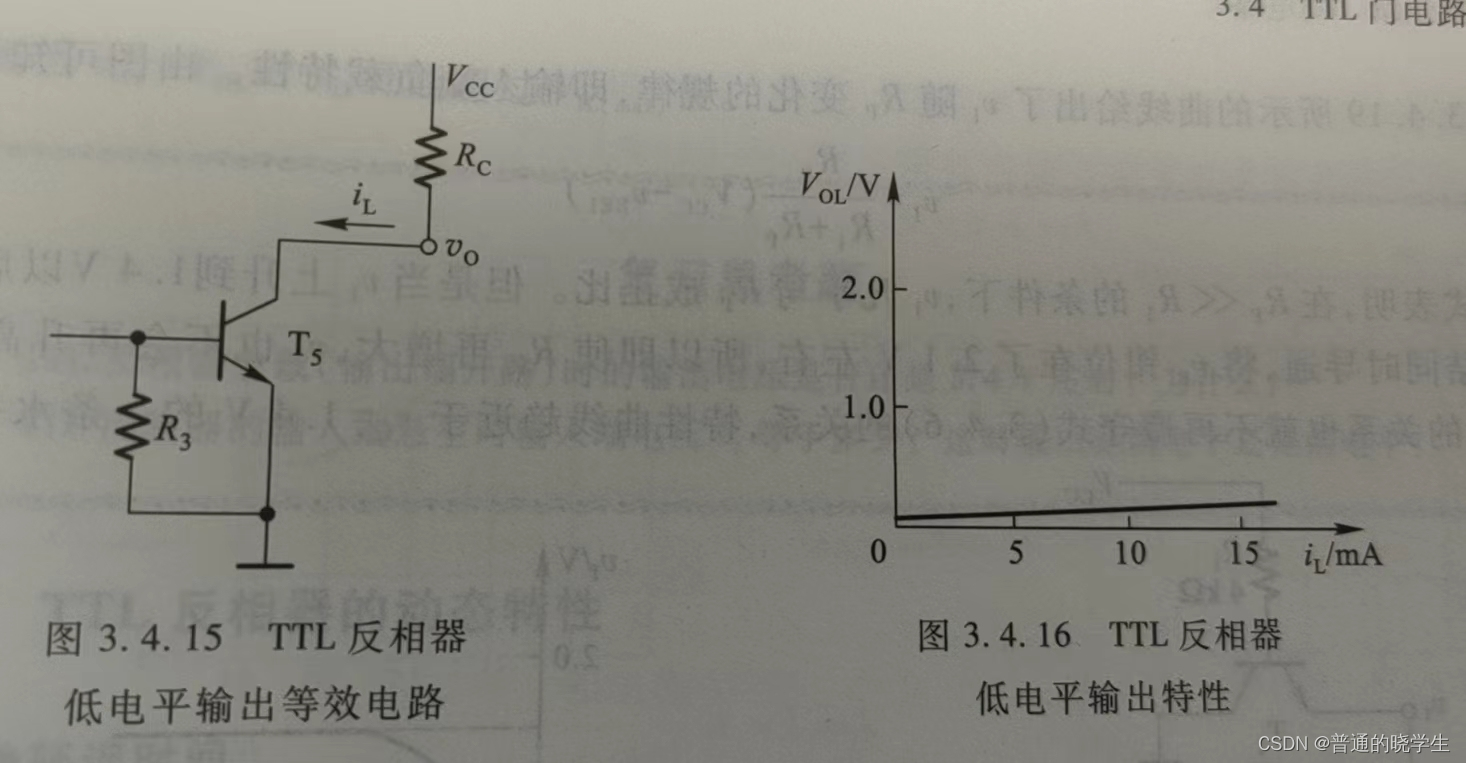

(输出低电平)

输出电平,忽略掉导通压降,从零开始,随着负载增加,电压会上升。

T5相当于一个有内阻的电压源,内阻不变,随着负载的增加,Rc变小,电压就抬上去了

输入端负载特性

这是TTL器件独有的一个特性,因为CMOS器件有一个好处是输入是隔开的,没有电流,只有电压传递,所以输入不需要考虑。但是TTL不一样。

在输入端接电阻Rp接地。

Rp和R1形成了分压关系,当Rp上升,Vi也随之上升,但是根据前面所讲的,Vb1最高只有2.1V,所以输入最高1.4V。

如果TTL反相器,输入什么都不接,空置,输出为0,从输出看,会以为输入接了高电平。所以,TTL输入没用的时候要妥善处理

其他参数(CMOS也适用)

- 扇出系数

驱动能力,CMOS不讲还有一个原因就是理想的CMOS电路驱动能力无限,因为不取电流。

一个门电路,带自己同样类型的门能带多少个。对于TTL电路,这个扇出系数根据电压传输曲线,输入曲线,高低电平的输出曲线综合分析。(输出在电压允许范围得知带负载能力,除输入需要的电流)

CMOS门电路有这个问题是因为它的导通内阻还是有的,而且后端有漏电流。(但是远比TTL高,因为电压传输不需要电流)

- 传输延迟时间

-

在真值表中当输入发生变化,从一行跳到另一行,需要多长时间,输入跳了,输出要多长时间才能跳过来。

-

真值表给出的是0和1,是你所选择的器件的高电平或低电平

-

tpd:有效到有效的时间(途中要经过无效),希望尽量小

-

tcd:当输入从有效进入无效,输出保持多久上一个有效,希望尽量大

- 交流噪声容限

当输入信号为窄脉冲,且接近于tpd时,输出变化跟不上,变化很小,因此交流噪声容限远大于直流噪声容限。

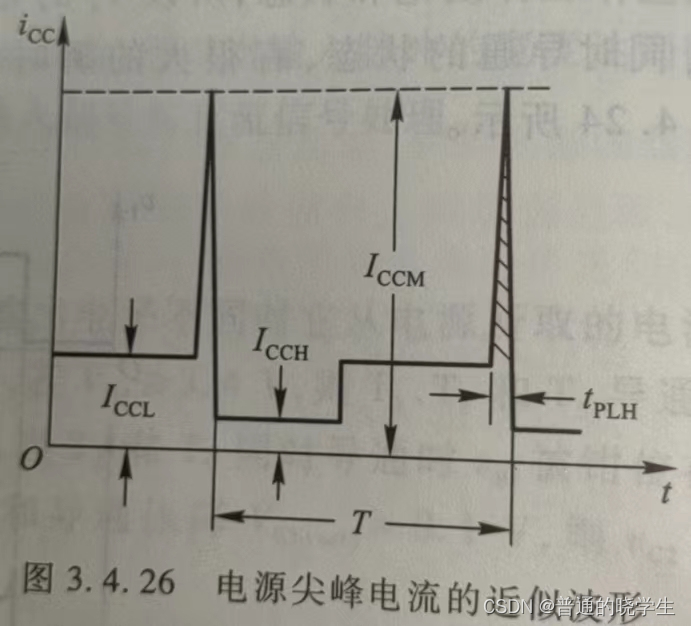

尖峰电流

成因:Vi 上升和下降过程中,瞬时T4,T5同时导通。

设计中需要留裕量;高频,可能变成干扰源。

其他TTL门电路

其他逻辑功能的门电路

与非门,双发射极,同高才为高

- 多发射极实现与

问题:输入为低电平,从电源取的电流值都一样;输入为高电平,几个PN结有几个反向电流

TTL中也没有直接的与门,也都是与非门,要想实现与,后面再加个反相器。原因是高电平导通下拉出来了,其实和CMOS上拉下拉是一样的。

或非门,并联结构实现或(对管结构)

高电平进去数两份,低电平也数两份

与或非。

OC门

推拉输出电路结构的局限性:

1.输出电平不可调

2.负载能力不强,尤其是高电平输出

3.输出端不能并联使用(线与)

因为这个局限性,引出OC门(集电极开路)

和OD门一个原理,使用时需要外接电源和上拉电阻。

- OC门全部截止,这时上拉电阻就是整个电压源的内阻,这个内阻不能太大

- 不能太小,怕电流太大

三态门

EN’ = 0,A和B是与非

EN’ = 1,T4和T5同时截止,高阻态

第三章整体需要额外精读

一、CMOS电路的正确使用 P101

1.输入电路的静电保护

2.输入电流的过流保护

3.CMOS电路的锁定效应

二、CMOS集成电路的各种系列 P106(泛读)

4000,74HC/HCT,74AHC/AHCT

74VHC/VHCT

74LVC,74ALVC

三、TTL集成电路的各种系列 P148(泛读)

74S等

四、TTL与CMOS电路的接口

1.满足电平匹配的要求

2.用TTL电路驱动CMOS电路 P147(电压不匹配)

3.用CMOS电路驱动TTL电路 P148(电流不匹配)

本章小结

- CMOS门电路 —— 反相器 —— 其他CMOS逻辑门

- TTL门电路 —— 反相器 —— 其他TTL逻辑门

- TTL电路,CMOS电路的接口

最后

以上就是狂野心情最近收集整理的关于数电学习(三、半导体二极管门电路)(三)TTL门电路第三章整体需要额外精读本章小结的全部内容,更多相关数电学习(三、半导体二极管门电路)(三)TTL门电路第三章整体需要额外精读本章小结内容请搜索靠谱客的其他文章。

发表评论 取消回复