FPGA系统异步复位同步释放设计

FPGA逻辑设计属于硬件范畴,不是简单的代码实现,更需要有很多的硬件知识积累。

1.1 寄存器和锁存器

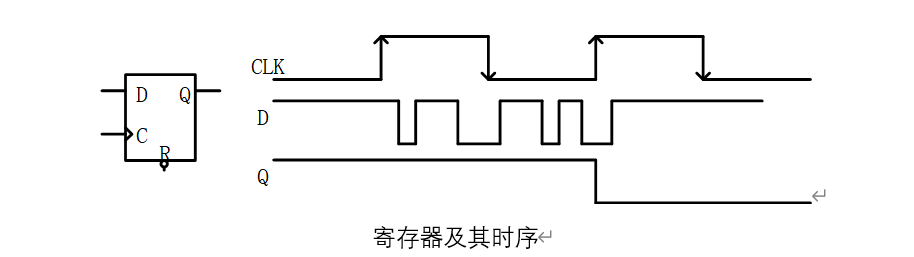

要理解时序电路需要理解里面的两个基本单元寄存器(register)和锁存器(latch)。寄存器:又叫触发器(flip flop),也可以说成D触发器。寄存器是边沿触发,就是在时钟翻转的时候才对输入端采样,然后经过触发器内部电路延时输出采样结果。因此触发器是依存于触发信号(时钟信号)来实现数据的传输,这样在时序优化时能够很好的去做定量优化。

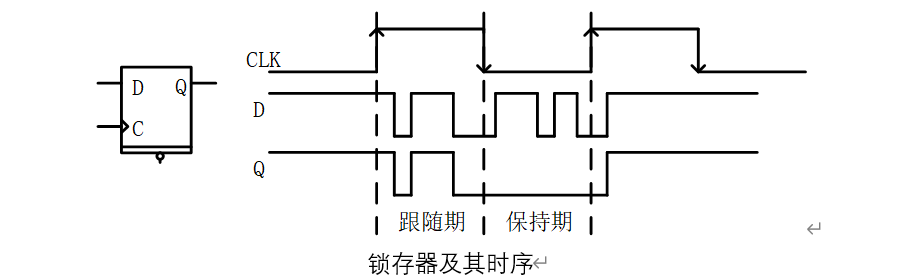

锁存器:这是个电平敏感元件,存在跟随期和保持期。在时钟信号位高电平的时候器件被激活,处在跟随期,输入采样经过内部电路直接输出,也就是在触发信号激活时输入到输出是直通的,输出是跟随输入的。当时钟出现下降沿时,处在保持期,输出锁存输入信号,这时输出的信号保持时钟下降沿时的输入信号。

1.2 同步复位和异步复位

在FPGA逻辑实现中大多数用到的是寄存器。而系统要想稳定的开始工作就需要有一个很好的逻辑开始时间。如果系统所有时序逻辑都在同一个时间点开始工作,则系统时序就能有着很好的鲁棒性。因此系统的开始模块设计也就是系统的复位模块设计就需要满足很严格的时序要求。系统复位一般分为同步复位和异步复位。

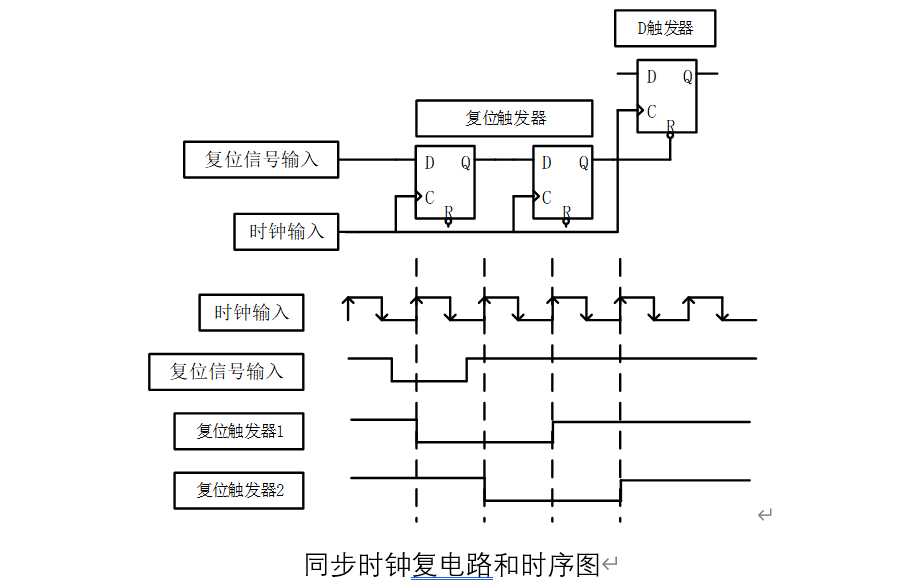

同步复位是复位信号和时钟信号同步,其实就是复位信号作为触发器的输入端,通过时钟控制输出到其他功能寄存器的复位引脚。同步复位信号长度需要满足系统最慢时钟的寄存器复位要求,也就是同步复位输入时间长度应当大于最慢时钟的周期。有个最简单的要求就是复位信号的宽带至少要比系统里面最慢的时钟周期要长,我设计时一般要求至少要大于1.5倍的最慢时钟周期。

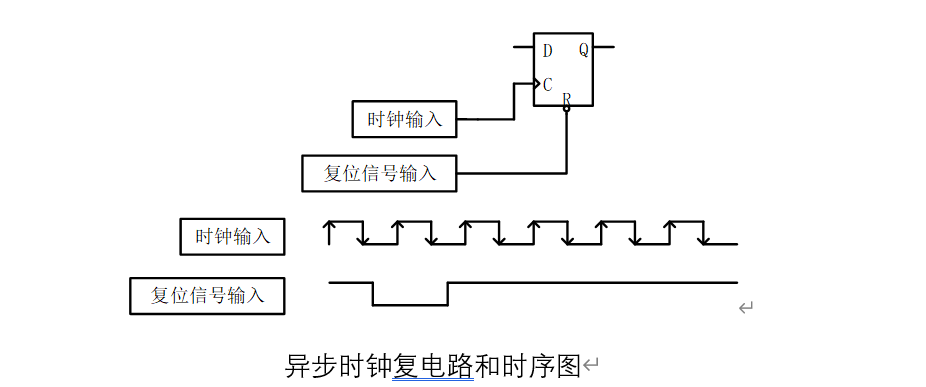

异步复位比较粗暴直接。异步复位是直接把复位信号接到功能寄存器的复位端上,完全独立与时钟,是否复位跟引脚电压直接相关。就是异步时钟复位的输入是随机的,和系统内部逻辑没有起因关系并且对电平毛刺比较敏感,会导致系统D触发器输出产生混乱,因此异步复位容易产生时序时间冲突。而时序电路最怕的就是这种随机的不可靠的时序错乱。

异步复位比较粗暴直接。异步复位是直接把复位信号接到功能寄存器的复位端上,完全独立与时钟,是否复位跟引脚电压直接相关。就是异步时钟复位的输入是随机的,和系统内部逻辑没有起因关系并且对电平毛刺比较敏感,会导致系统D触发器输出产生混乱,因此异步复位容易产生时序时间冲突。而时序电路最怕的就是这种随机的不可靠的时序错乱。

虽然异步时钟存在很多问题,但是他用的资源少啊,复位信号不依赖时钟呀,实现起来简单呀,用起来还是比较爽的。单纯的用异步复位的话需要在外部复位输入加上去抖芯片,避免输入电平毛刺,加上长时间的复位输入可以避免接大多数问题,但是不能保证不出问题。

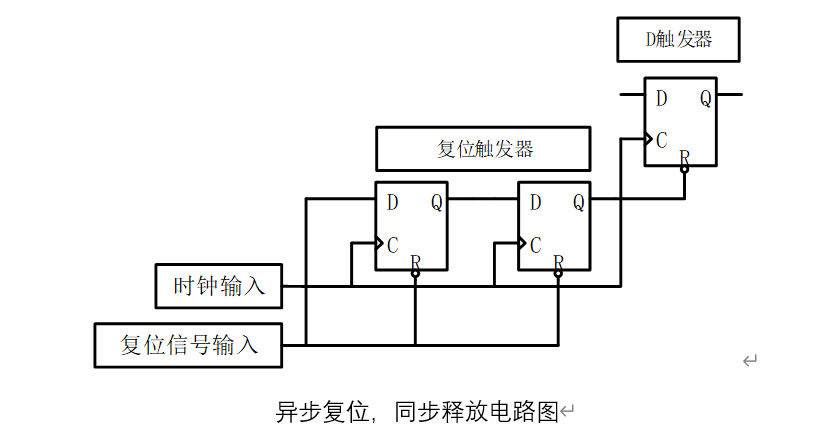

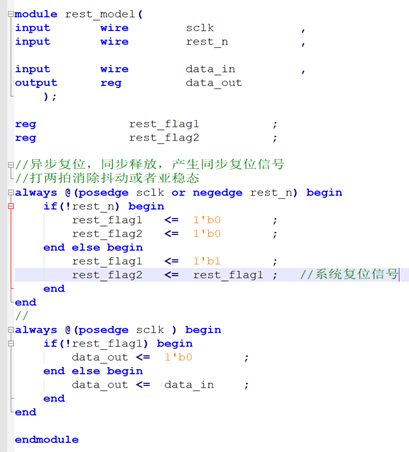

针对同步复位和异步复位的优缺点,可以采用“异步复位,同步释放的方式”来实现系统的复位模块。就是把寄存器分为两种,实现复位信号转化的复位寄存器和系统应用的其他功能寄存器。复位寄存器其实就是异步复位通过打两拍来让去除一定的亚稳态,然后输出一个确定的电平,然后利用这个电平作为功能寄存器复位引脚输入,这样就可以把外部的异步输入转化成依赖时钟的同步复位了。

异步复位,同步释放实现

最后

以上就是美丽钢铁侠最近收集整理的关于FPGA系统异步复位同步释放设计的全部内容,更多相关FPGA系统异步复位同步释放设计内容请搜索靠谱客的其他文章。

发表评论 取消回复