目录

一、为什么不建议全局复位

1.1 异步复位

1.2 同步复位

1.3 xilinx的提供方案

1.3.1 赋初值机制

1.3.2 触发器模式

二、如何去复位

2.1 采用高电平同步复位

2.2 建议异步复位同步释放

2.3 PLL稳定后再复位

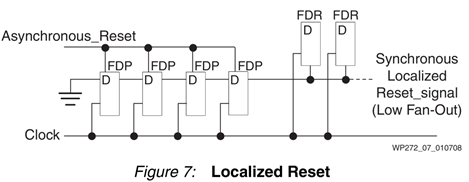

3.4 建议局部复位注意扇出

一、为什么不建议全局复位

复位实质就是保证FPGA初始状态是符合预期的,逻辑能够从预想初始状态进入运行状态。复位方式分为异步复位和同步复位,这两种复位方案各有优缺。在现今FPGA工作频率日渐提高,资源日趋庞大的情况下,全局复位劣势也日渐凸显,所带来的问题就不得不面对了。另一方面,FPGA器件的迭代更新,使得初始化有了新的解决方案,所以复位也就不建议全局复位。

1.1 异步复位

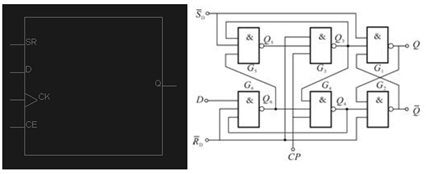

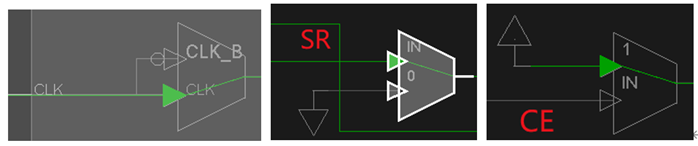

FPGA内部的触发器是D触发器,如图1-1-1所示,“SR”即置位(set)、复位(rst),无论时钟信号是否有效,都可以通过对“SR”控制实现对触发器的复位和置位,所以时钟和“SR”均可影响“Q”的状态,这也就为异步复位可能出现的问题埋下祸根。

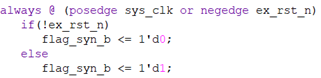

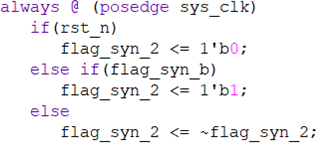

所谓异步复位就是利用触发器这一特性将信号线接到“SR”实现对其的初始化操作。再程序上的体现如图1-1-2所示,也就是在敏感列表中加入复位信号。

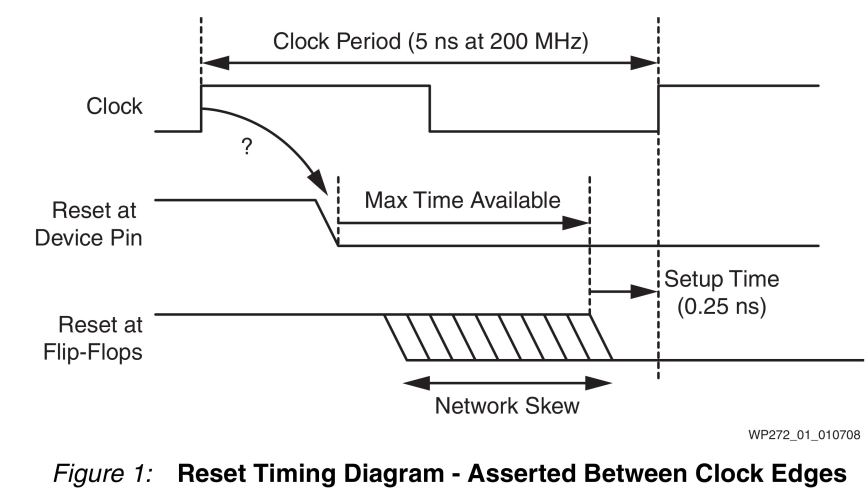

异步复位的好处是相交同步复位不受时钟、脉宽的限制,能够保证寄存器得到有效复位。但由于复位信号与时钟信号间没有必然联系就有可能出现问题,在《WP272》给出的如图1-1-3用于说明异步复位可能出现问题。

第一行是200M的时钟,第二行是引脚输入的复位信号,第三行是到寄存器的复位信号。接下来要综合两个信息来进行分析,一是我们根据图1-1-1可得知,复位信号“SR”和数据“D”都是经过与门进入触发器的。二是数据在时钟上升沿到来之前需要一定的建立时间例如上图的0.25ns。所以在复位释放后需在下一个时钟的上升沿的0.25us完成,除以以外还有保持时间的要求,所以复位信号到各个寄存器的延时是不能大于4ns多些的,否则有的寄存器就会出现因建立、保持时间不满足而无法保证采集数据的准确性,而且复位信号与时钟信号时异步的,随着时钟频率的提高,这种可能性就越大。

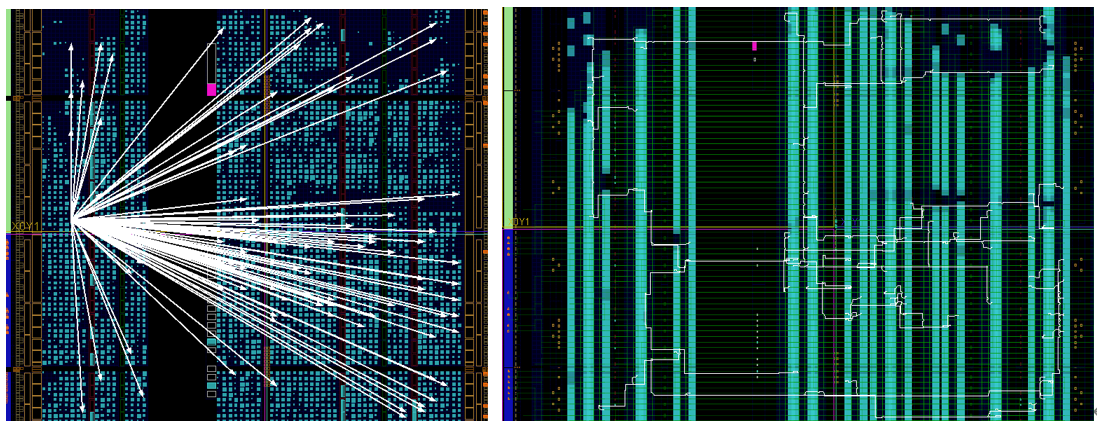

因此,有了异步复位同步释放的方案,但依旧不建议全局复位。因为异步复位时信号线接到“SR”端口,随着器件资源增多,频率提高,全局复位就会造成信号扇出增大,增加时序的复杂些,布局时序难以得到满足,那么依旧会导致在复位释放时出现亚稳态的情况。图1-1-4是某程序的复位信号,占用了很多的布线资源,扇出也很大。那么,同步复位呢?

1.2 同步复位

如图1-2-1是同步复位,同步复位和异步复位的区别在于敏感列表中没有了复位信号,这也说明复位时必须有时钟,否则无法完成复位操作。

对于Altera的FPGA是不支持同步复位的,只支持低电平的异步复位,所以复位信号不会接到寄存器的“SR”上,对于Xilinx的FPGA支持同步复位,会根据逻辑视情况选择性的将复位信号综合到“SR”上,也就是说,复位信号或可综合再查找表中,与其它信号线共同组织选择逻辑由“D”端口到触发器,而将触发器的复位信号接到内部的“SRUSEDMUX”上,顺便说一句,时钟使能也有类似的选择器叫“CEUSEDMUX”,时钟的选择器叫做“SLICEL_CLKINV”,如图1-2-2所示。这也就是为什么《ug494》提出控制集的概念,因为一个slice共享控制信号,而外部来的复位、时钟使能、时钟信号都要经过这几个选择器到触发器,所以要是不同的控制信号就会分配到不同的控制集。

全局的同步复位主要问题是会占用大量的查找表造成资源的浪费,而且还会挤占关键信号的布线空间,降低其布线的自由度,甚至不满足时序要求。也增加了布局布线的时间,记得在之前没有将某些时钟域设置“set_false_path”,实现时间会增长很多。

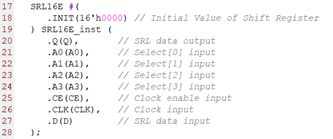

另外,xilinx有些资源是不支持复位的,例如SRL16E 移位寄存器,有些资源是不支持异步复位的,比如DSP48 和Block RAM。

1.3 xilinx的提供方案

1.3.1 赋初值机制

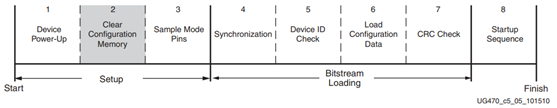

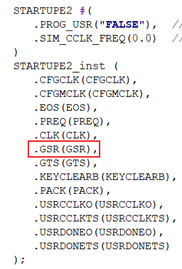

如图1-3-1是FPGA的上电配置流程,在进行到步骤2时会将GSR(全局置位、复位信号)拉高,对RAM、寄存器、查找表等赋初值,这个初始值可以是我们通过类似“reg a = 1;”这样赋值,也可以是Xilinx提供的默认值。

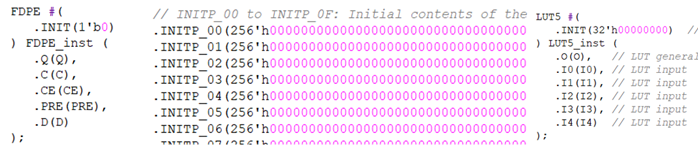

打开原语可以看到原语都会有“INIT”或类似的选项,这就是初始值,在《ug949》中提到,在大多数情况下默认值为零。FDSE 和 FDPE 原语是例外,默认为逻辑 1。每个寄存器在配置结束时将处于已知状态,如同1-3-2所示。

所以我们即便不对寄存器、ram等进行复位,其初值也是确定的,这就为不复位提供了可能。另外,我们也可以控制“GSR”信号来对FPGA进行初始化,如图1-3-3包含该信号的原语 STARTUPE2,但官方并不建议我们利用该信号进行复位,因为这个信号只与用户时钟同步且异步释放,而且系统中有存在多个时钟存在的可能,这就为亚稳态出现创造了条件,得不偿失。

1.3.2 触发器模式

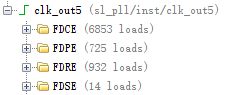

如图2-3-4所示是综合后的触发器类型,有FDCE、FDPE、FDRE和FDSE四种。

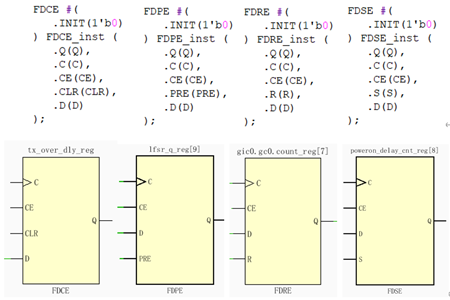

如图1-3-5是触发器的具体类型,触发器的控制集包括时钟输入、时钟使能(高有效)和高有效的SR端口,SR端口可以作为异步复位(FDCE)、异步预置位(FDPE)、同步复位(FDRE)、同步置位(FDSE)四种。其中“FD”为“D-flip-flop”即D型触发器,“C”为“Clear”、“P”为“Preset”、“R”为“Reset”、“S”为“Set”、“E”为“Clock Enable”。置位和复位的区别就在于将SR端口置一后Q是高电平还是低电平,这方面在《UG768》中有详细描述,总的来说就是置位就是置1,复位就是置0。

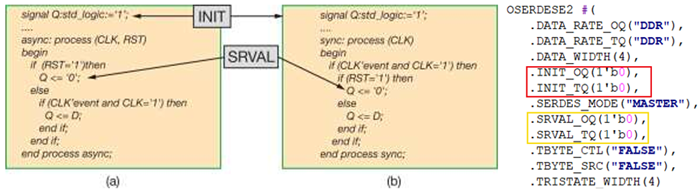

触发器的复位或置位和在第1-3-1节描述的赋初值是不同的,这个是在加载之后由程序控制所进行的操作,如图1-3-6所示。在Xilinx中,赋初值被称之为INIT,置为或复位称之为SRVAL,异步和同步的区别就在于是否需要时钟的参与,在触发器中SRVAL属性并不明显,但在一些较复杂的硬核中都有这连个属性,例如“OSERDESE2”这个原语。

综上,Xilinx的触发器支持高电平的异步和同步复位,我们就可以采用不同的复位方式对逻辑进行复位,具体如何去复位还是要看《WP272》、《WP275》、《ug949》相关的描述。

二、如何去复位

就xilinx如何去复位及原因如下:

2.1 采用高电平同步复位

根据上述分析,同步复位的原因是提高了资源的利用率,vivado会根据逻辑选择性的将复位信号综合到“SR”端口或吸收到了查找表中,进而降低布线难度获得更好的时序。同步复位较异步复位,也会牺牲些资源。Xilinx设计的触发器是高电平复位,如果采用低电平复位就会消耗额外的资源对复位信号做处理。而且有些硬核资源根本不支持低电平复位和异步复,例如DSP。

2.2 建议异步复位同步释放

如图2-2-1所示是异步复位同步释放的时序图,复位信号可能来自于外部的复位芯片、按键等,或内部某时钟域产生的复位信号,如果直接用到其它时钟域就有可能产生亚稳态,所以可以采用复位桥电路,用异步复位SR,同步产生接触复位,使复位信号同步到各个时钟域中去。我们阀控板卡就是采用的这种复位方式。

2.3 PLL稳定后再复位

另外,我们会用到PLL产生不同的时钟,需再PLL稳定后再对逻辑进行复位,也就是现程序中的“pll_locked”,就PLL是否复位可视情况而定,再时钟稳定后会将“pll_locked”拉高表示时钟稳定相位锁定。

如图2-3-1是PLL时钟源时钟丢失后的情况,“pll_locked”会首先拉低,待10us左右后时钟停止,如图2-3-2所示是PLL时钟恢复的情况,再时钟恢复16us后PLL锁定,所以“pll_locked”能够保证时钟的稳定性。

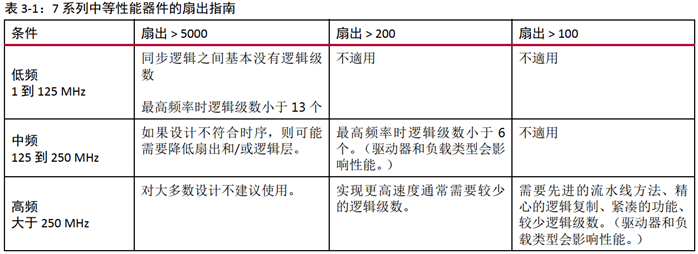

2.4 建议局部复位注意扇出

全局复位必然会增加扇出,影响时序,且时钟频率越高影响越大,这也就是不建议全局复位的原因,如图3-4-1是《ug949》建议的扇出大小,我们可以用“report_high_fanout_nets”查看扇出报告来评估扇出的大小。

看网上说,对于信号扇出不大于16的情况都可以尽可能的被吸收到同一个slice的LUT中去,在vivado中可以使用control_set_opt_threshold进行设置,具体没有研究。

局部复位正如《ug949》建议,需评估每一个同步块,判断是否需要复位以确保正常运行。在确定不需要的情况下,切勿将复位编码为默认项。使用功能仿真应能够轻松地判断是否需要复位,因为不复位有些寄存器会显示高阻态或不定态,但对于FIFO,根据应用情况来说不建议复位,但不复位又没法仿真,这也是个矛盾,目前就加个临时复位来处理。

不复位包括不需要复位也能正常运行的寄存器,也有些特殊资源没有复位接口,例如xilinx 原语SRL16、SRL32、LUTRAM等,如图2-4-2的位移寄存器,只能用GSR方法再上电时复位。

欢迎关注沧小海的fpga微信公众号,回复“复位”获取相关参考文章

最后

以上就是昏睡蜡烛最近收集整理的关于沧小海笔记之xilinx的FPGA为什么不建议全局复位及如何复位一、为什么不建议全局复位二、如何去复位的全部内容,更多相关沧小海笔记之xilinx内容请搜索靠谱客的其他文章。

发表评论 取消回复