1. 概念

锁存器-latch :是电平触发的存储单元, 数据存储的动作只取决于 输入信号 的电平值 ,只有当锁存器处于使能 状态, 输出才会随着 输入发生变化;

触发器-Flip flops: 当收到 输入脉冲时,又称为触发。触发器 输出会根据 规则 改变 状态,然后保持这种状态直到 收到 另一个 触发 ;

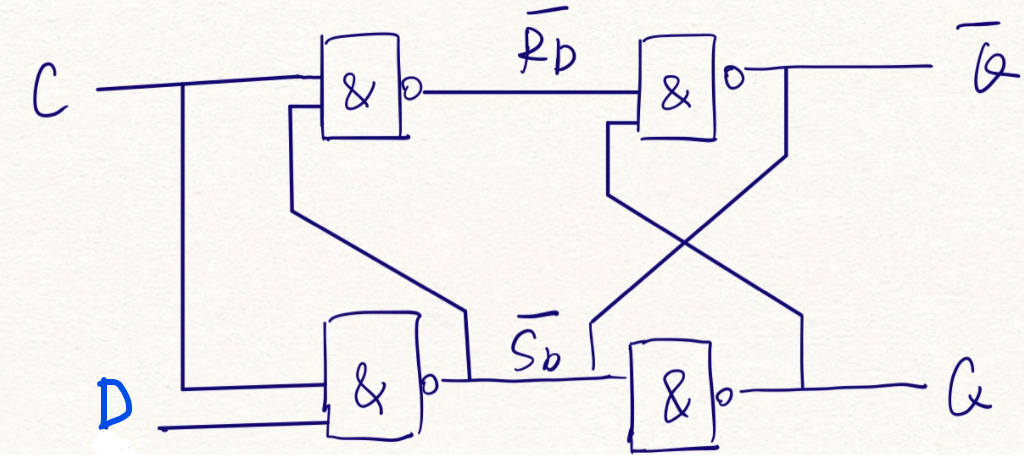

D锁存器

-

当C被拉高时,Q的状态随着D的状态变化

-

当C被拉低时,锁存此时D的状态、

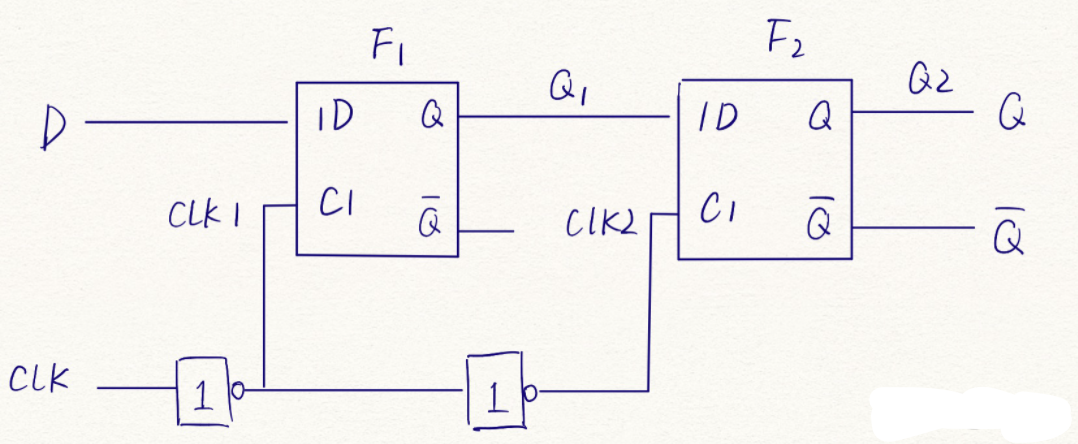

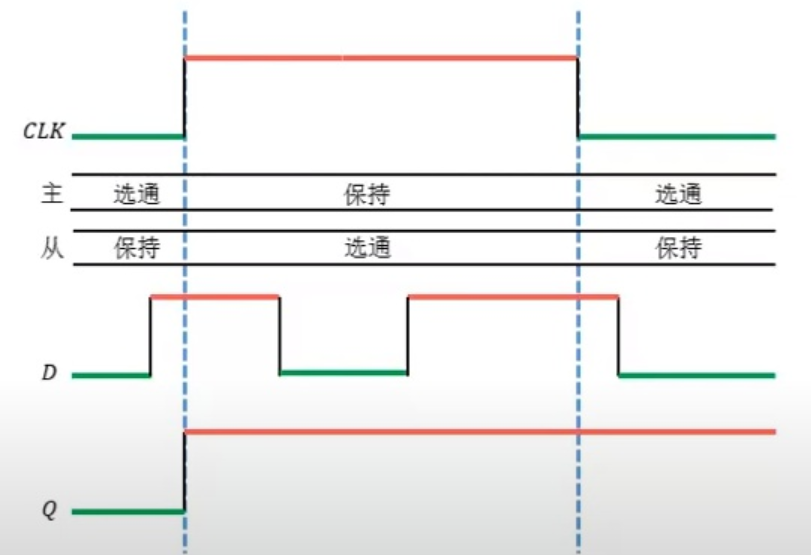

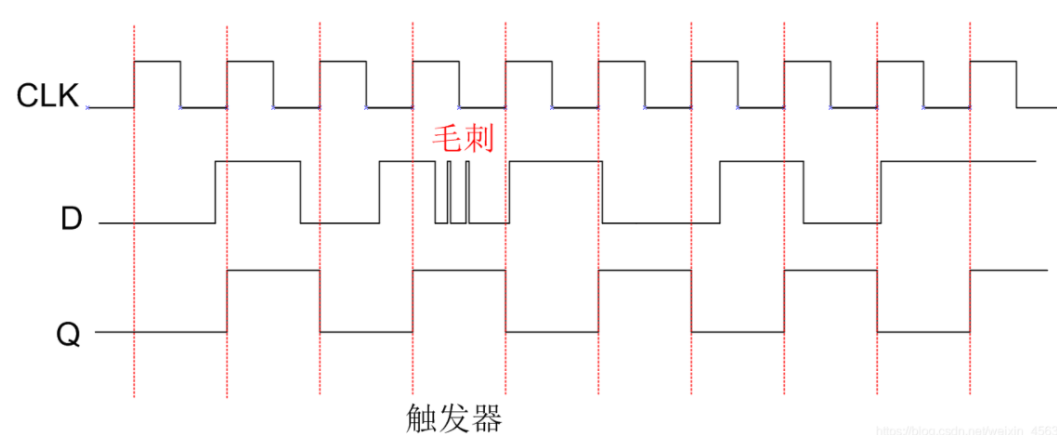

主从D触发器

触发器是边沿触发的。主从D触发器可以很好地解决空翻现象

-

F1为主触发器,F2为从触发器

-

主从D触发器为边沿触发 当激励产生,CLK=0,D=1,F1工作,此时Q1=1,但F2只能等到下一拍才可触发。下一拍CLK=1,Q1=1,F2工作,Q=1。

-

可以有效解决空翻 (即当Clk有效,D不断变化时,一次时钟来到期间,触发器多次翻转 )

2. 两者区别

a, latch 同 所有的输入信号相关,当输入信号变化时,latch 就会变化;

DFF 由 时钟沿触发, 只有当时钟触发时,才会采样当前的输入,产生输出;

两者都是时序逻辑,都会与 上一时间 的输出相关;

b, latch 是电平触发,非同步控制;

DFF由时钟沿 触发,同步控制;

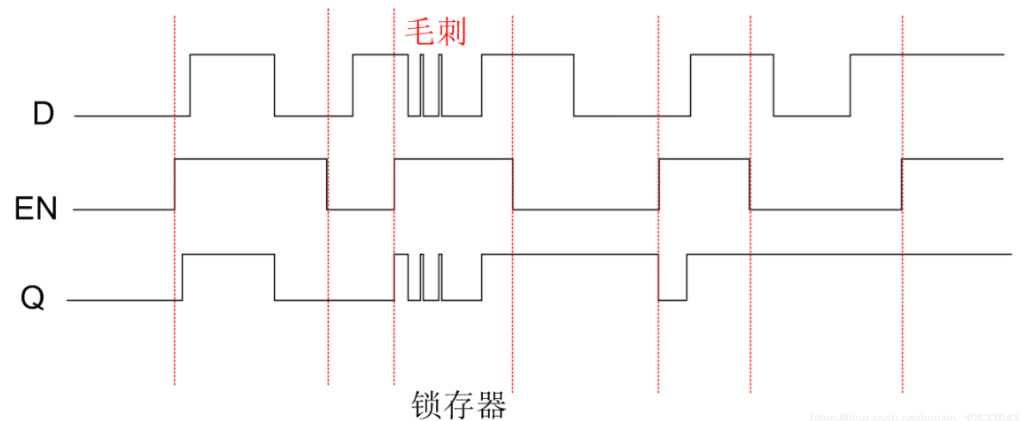

c, latch 对电平敏感,受布局影响打,容易产生毛刺;

DFF不易产生毛刺;

d, 如果使用 门电路 搭建 latch 和 DFF, 则 latch 消耗的门 资源比DFF 要少, 这是latch 优越的 地方;

但是 latch 会将静态时序分析变得 极为复杂,在大多设计中 都避免产生 latch, 其会让设 计 的时序出现 问题 且 很难排查, 另一个危害是 不能过滤 毛刺,在下一级电路中很危险;

锁存器对毛刺敏感

触发器可以过滤毛刺

3. 两者代码

锁存器

Module D_latch(d,clk,q);

Input d;

Input lck;

Output reg q;

always@(clk or d)

if(clk) q<=d;

endmodule触发器

Module D_ff(d,clk,q);

Input d;

Input lck;

Output reg q;

always@( posedge clk)

q<=d;

endmodule异步低有效D触发器

module code(clk,rst_n,d,q);

input clk;

input rst_n;

input d;

output reg q;

always @( posedge clk or negedge rst_n)

begin

if(!rst_n)

q <= 1'b0;

else

q <= d;

end

endmodule异步高有效D触发器

module code(clk,rst,d,q); //关于高有效还是低有效,都是驱动clk对输出端进行使能,有效 即为输 出为0,并不是输出要等于复位信号的值。

input clk;

input rst;

input d;

output reg q;

always @( posedge clk or posedge rst )

begin

if(rst)

q <= 1'b0;

else

q <= d;

end

endmodule注意:关于高有效还是低有效,都是驱动clk对输出端进行使能,有效 即为输出为0,并不是输出要等于复位信号的值。

同步高有效D触发器

module code(clk,rst,d,q);

input clk;

input rst;

input d;

output reg q;

always @( posedge clk)

begin

if(rst)

q <= 1'b0;

else

q <= d;

end

endmodule注: 上述图片来自于网络;

最后

以上就是平淡小猫咪最近收集整理的关于锁存器 和 触发器的全部内容,更多相关锁存器内容请搜索靠谱客的其他文章。

发表评论 取消回复