数字电路基础知识——时序逻辑电路之半导体存储器(D触发器、锁存器(D、RS、JK、T))

在介绍本节之前,一般会有如下规定:

锁存器:电平敏感

寄存器:边沿触发

触发器:边沿触发

数字电路中有关半导体存储器件的主要是D触发器、锁存器、存储器等。主要用来存储数据。用于存储一位数据的存储电路称为寄存器,而可以存储大量数据的称为存储器。

寄存器主要由一组触发器组成,n个触发器组成的寄存器可以存储n位的二进制值数据。

存储器的种类较多,但基本都是由存储矩阵和读写控制电路两大部分组成。根据工作方式的不同,可以将存储器分为随机存储器(RAM)和只读存储器(ROM)。其中RAM又可以分为静态随机存储器(SRAM)和动态随机存储器(DRAM)。

本节主要介绍寄存器组成的相关存储电路,如RS锁存器、触发器。

触发器按触发方式可分为:电平、脉冲、边沿

按逻辑功能可分为:RS、JK、D、T

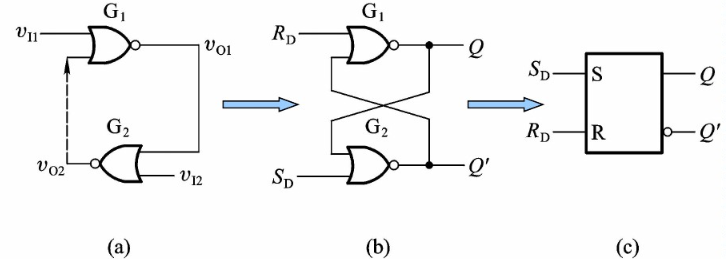

一、RS锁存器

-

SR锁存器的结构

利用两个或非门接成反馈

我自己把这个电路取名为莫比乌斯环锁存电路。^ _ ^ 个人偏好,没有不尊重学术的意思 -

工作原理

Q=1为锁存器的1状态;Q=0为锁存器的0状态

RD和SD分别为置0和置1输入端。

SD、RD如果同时为1时,消失后,下一个状态不定遵循 SD*RD = 0 的约束条件。 -

动作特点

在任何时刻,输入的改变都可以直接改变输出的状态。即电平敏感型锁存器。

所带来的缺点也就是抗噪性能不好。

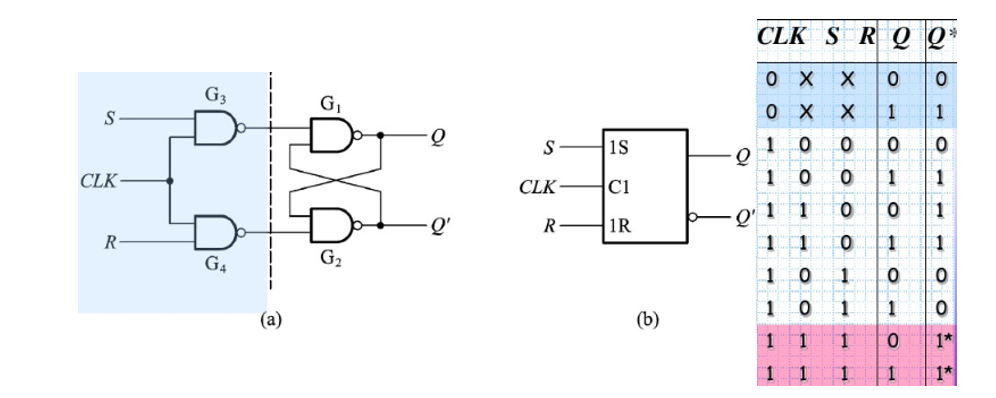

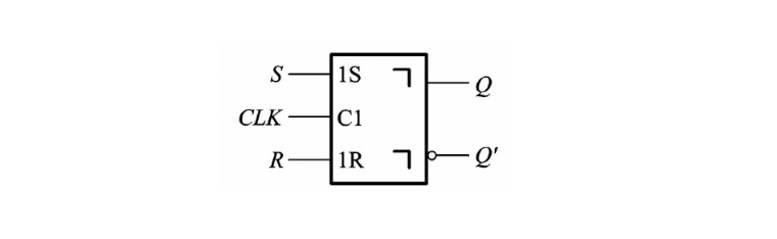

二、电平触发的触发器(SR、D 电平触发器)

- 电路结构

在基本RS锁存器的基础上增加输入控制们和CLK时钟输入信号。

- 工作原理

只有时钟信号有效,S和R才起作用。其真值表如上图所示。

同样也遵循S*R = 0 的约束条件,否则,当S=R=1时,当CLK回到0时或者S、R同时由1变为0,次态将无法确定。 - 动作特点

只有触发器在CLK = 1 的有效电平时间内,才能接受S、R端的输入信号的变化。

在CLK = 1 期间,Q可能随S、R变化多次翻转。 - 电平触发D 触发器

S和R端始终反向可以构成电平触发的D触发器。

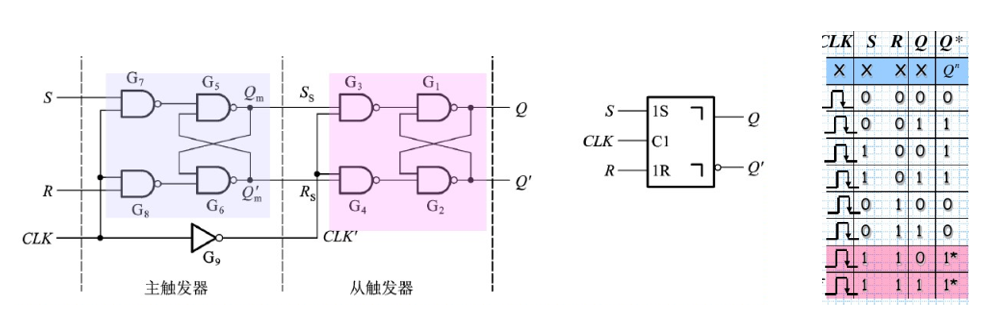

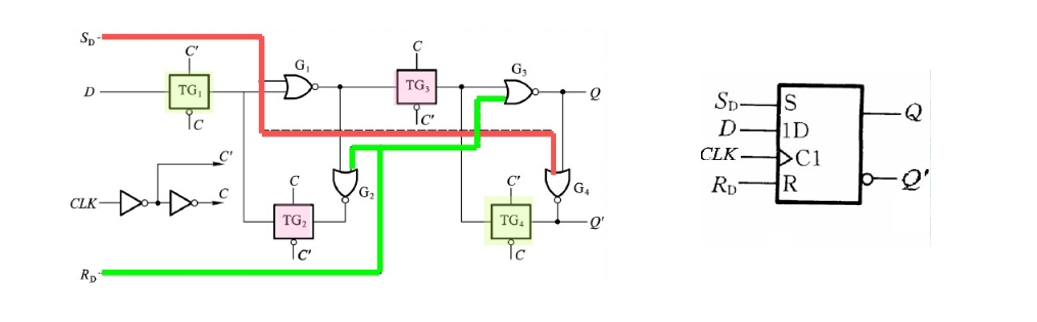

二、脉冲触发的触发器 (主从SR触发器、主从JK触发器)

-

主从SR触发器

结构和逻辑框图及真值表如下:

工作原理:

clk = 1时,主触发器按S、R翻转,从保持

clk下降沿到达时,主保持,从根据主的状态翻转

因此每个clk周期,输出状态只能改变一次

依然存在约束问题。 -

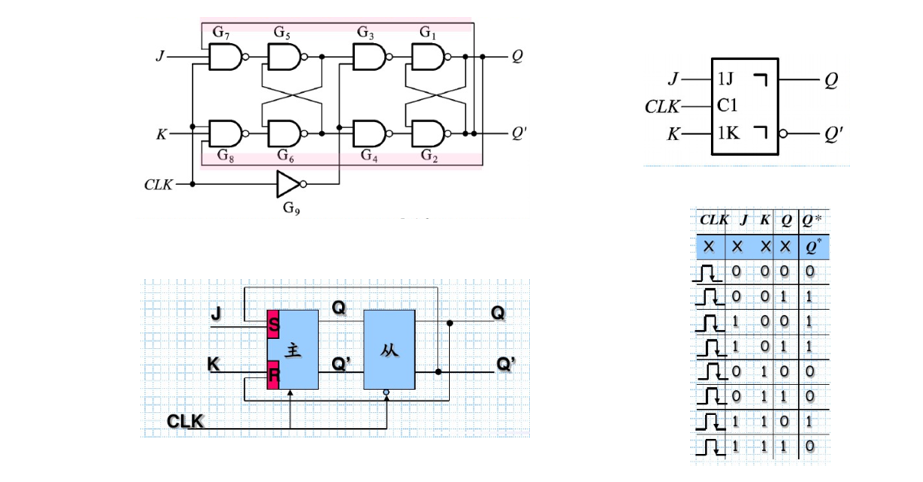

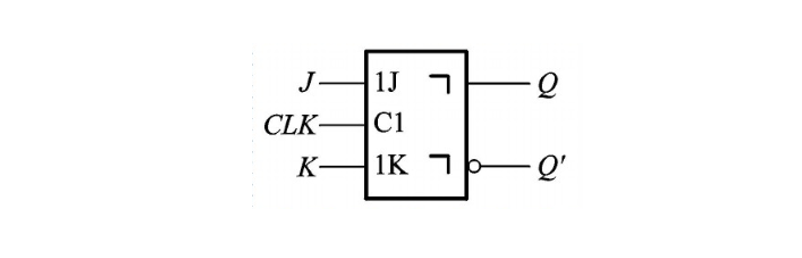

主从JK触发器

主从JK触发器可以解除上述SR触发器的约束限制

即使出现S=R=1的情况下,次态也是正确的逻辑。

若J=1,K=0,则clk=1时,Q*=1,主保持1,Q*=0,主=1。clk下降沿后,从=1

若J=0,K=1,则clk=1时,Q*=1,主=0,Q*=0,主保持0。clk下降沿后,从=0

若J=0,K=0,则clk=1时,Q*=1,主保持,Q*=0,主保持。clk下降沿后,从保持

若J=1,K=1,则clk=1时,Q*=1,主置0,Q*=0,主置1。clk下降沿后,从=(Q*)’

- 脉冲触发方式的动作特点

当clk=1时, 主接受信号,从保持

当clk下降沿到达后, 从按主状态翻转

一个时钟周期,状态只能改变一次

主从SR, 主为同步SR,clk=1的全部时间里,输入信号都对主起控制作用

但是需要注意的是,JK在clk高电平期间,主只可能翻转一次

所以在clk =1期间里输入发生变化时,要找出clk下降沿前Q’最后的状态才能决定次态Q*

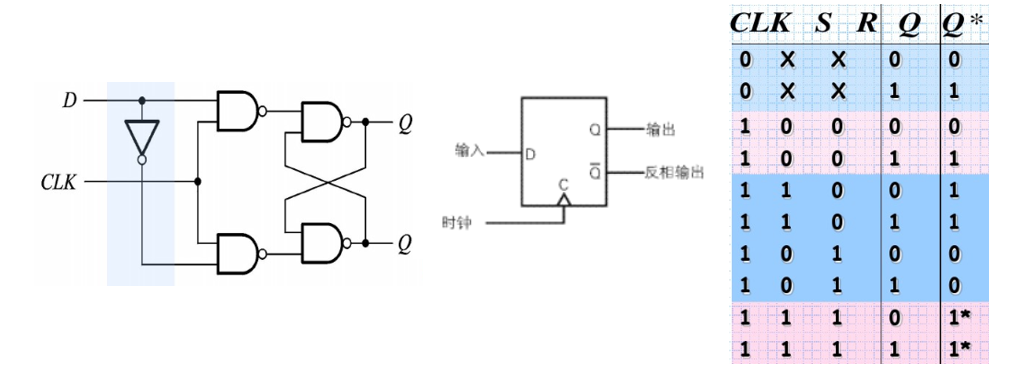

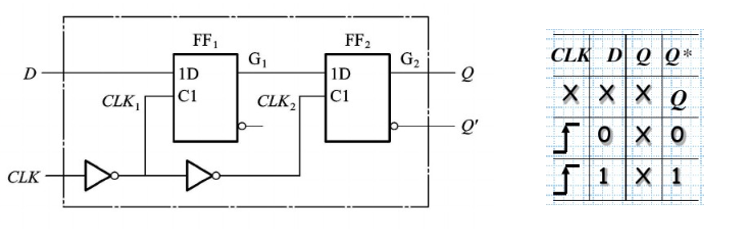

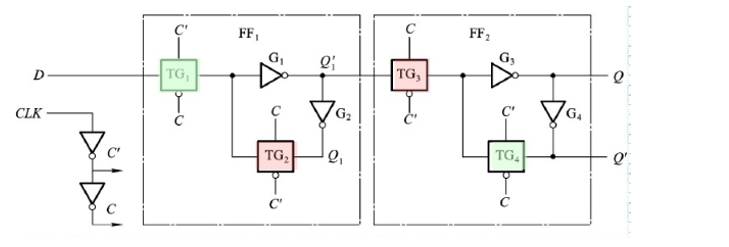

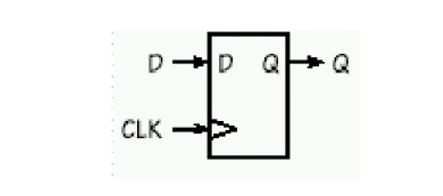

三、边沿触发的触发器 (边沿D触发器)

上面提到的触发器都是电平触发的触发器,其缺点很明显就是不具有很高的可靠性,抗干扰的性能较差,例如JK触发器 在 clk =1 期间里输入发生变化时,都会影响结果,如果最后的信号出现波动会导致信号传输错误的问题。

- 电平触发器的原理结构

- 利用CMOS传输门制作的D触发器如下图,也是广泛采用的电路形式

- 下面是带有异步置位功能的边沿触发器:

四、触发器的逻辑功能和描述方式

- SR触发器

特性方程:Q* = S’R’Q + SR’Q + SR’Q’ = S’R’Q + SR’ = S + R’Q且SR = 0

2. JK触发器

特性方程:Q* = JQ’+K’Q

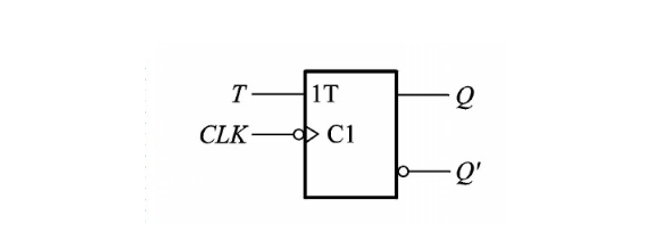

3. T触发器

特性方程:Q* = TQ’+T’Q

3. D触发器

特性方程:Q* = D

最后

以上就是碧蓝糖豆最近收集整理的关于数字电路基础知识——时序逻辑电路之半导体存储器(触发器、锁存器(D、RS、JK、T))的全部内容,更多相关数字电路基础知识——时序逻辑电路之半导体存储器(触发器、锁存器(D、RS、JK、T))内容请搜索靠谱客的其他文章。

发表评论 取消回复