概述

寄存器:存储一组数据的存储电路(由一组触发器组成,由n个触发器组成的寄存器可以存储一组n位的二值数据)

存储器:存储大量数据的存储电路。(可分为随机存储器(Random Access Memory)RAM,和只读存储器(Read-Only Memory)ROM两大类)

静态存储单元:门电路连接而成,其中包括各种电路结构的锁存器和触发器,在不切断电源的情况下,静态存储单元的状态会一直保存下去。

动态存储单元:利用电容的电荷存储来储存数据。缺点:电容充放电需要时间,则它的工作速度低于静态存储单元,且存储的电荷会随着时间的推移和泄露,必须要定期刷新,数据才不会丢失。

SR锁存器

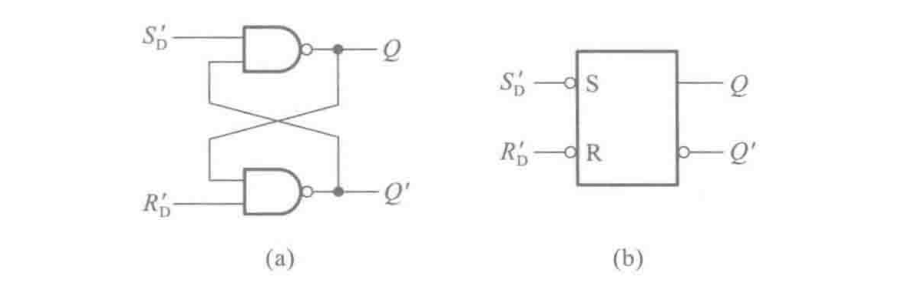

通常有或非门和与非门两种锁存器,在这里我们只介绍与非门锁存器,或非门同理。

锁存器我们希望它实现记忆的功能。

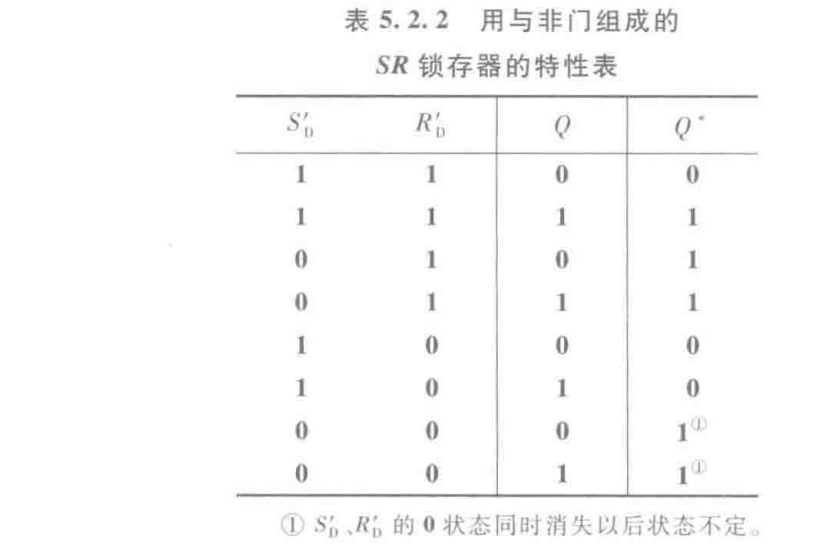

我们通常将SD撇 称为置位端,将RD撇 称为复位端,输入端的小圆圈代表低电平有效。通过图也可以发现S、R都为高电平时,输出保持原有状态;S=0,R=1时,输出置位1;S=1,R=0时,输出置位0;S=0,R=0时,S、R同时回到高电平后锁存器的状态难以确定;

当S为低(有效电平),R为高(无效电平)时,G1(上边的与非门)输出Q必为1,则G2门输出Qn必为~(1&1)=0,G2门输出连接到G1的输入,使G1门输出Q依然为1,此时撤掉S的输入信号(拉高为无效电平),由于Qn输出0,所以Q依然输出1。整个SR锁存器依然保持这Q=1、Qn=0的输出状态;

当S、R均为高(无效电平),假设初始时Q=1,Qn=0,此时G1门输入为S(1)以及Qn(0)输出Q依然为1,G2门输入R(1)Q(1)输出依然为0;假设初始时Q=0,Qn=1,此时G1门输入为S(1)以及Qn(1)输出Q依然为0,G2门输入R(1)Q(0)输出依然为1;综上,当SR=1时,SR锁存器表现出保持Q输出不变的状态,与(前提是Q=~Qn)

当S、R均为低电平(有效信号时),此时理论上来说Q、Qn均输出1,且可以保持稳定。但是当S、R同时撤掉有效信号(拉高)时,

第一:假设G1、G2同时运算,这是Q、Qn输出的1作用在与非门上导致输出两个输出0,0又作用在与非门导致输出1,循环往复,类似于矩形波,这与上面说的S、R为高电平时锁存器表现出保持Q输出不变的状态相违背;

第二:实际上这一状态无法保持稳定。当S、R同时升高为1时,由于实际工艺存在延迟及G1、G2门无法同时运算等多种不可抗力,当G1门率先运算时,此时S、R为1,Qn=1,故G1门输出Q为0,导致G2门输入变成1和0,Qn输出1,总输出Q=0,Qn=1;而当G2门率先运算时,此时S、R为1,Q=1,故G2门输出Q为0,导致G1门输入变成1和0,Q输出1,总输出Q=1,Qn=0;因此输出不具有稳定性。以上所说的不稳定性,仅限于S、R为有效信号的情况下同时撤去信号时,如果一个变无效、一个仍有效,或者两个信号均保持为低电平(有效)不变,SR锁存器仍具有稳定性。

通常,将Q=1,Qn=0称为电路的1状态,Q=0,Qn=1称为0状态。

(这里参考了CSDN博主「爱吃土豆的柯基」的分析)

原文链接:https://blog.csdn.net/m0_37885718/article/details/116454431

最后

以上就是重要大门最近收集整理的关于SR锁存器——数电第五章学习的全部内容,更多相关SR锁存器——数电第五章学习内容请搜索靠谱客的其他文章。

发表评论 取消回复