一.简介

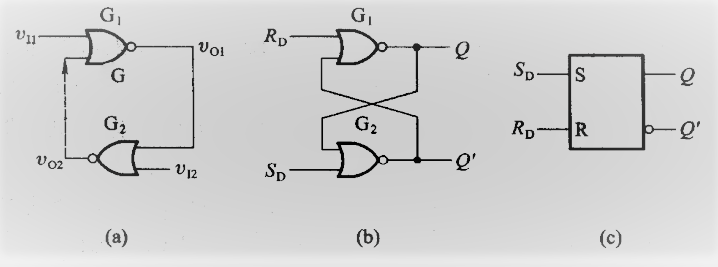

SR锁存器(Set-Reset Latch)属于静态存储单元的一种。一般由两个或非门或者与非门组成。

本文以或非门组成的SR锁存器为例,与非门组成的锁存器和或非门组成的锁存器原理、特性表相似。

二.电路图以及特性表

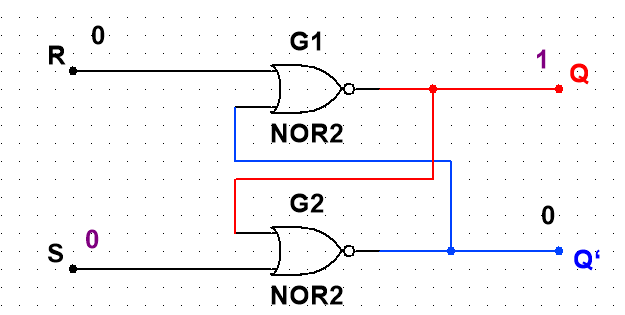

a.电路图

其中Q和Q’称为输出端,并且定义Q=1、Q’=0为锁存器的1状态;反之,Q=0、Q’=1为锁存器的0状态。SD与RD称为输入端,SD称为置位端或置1输入端;RD称为复位端或置0输入端。

b.工作原理

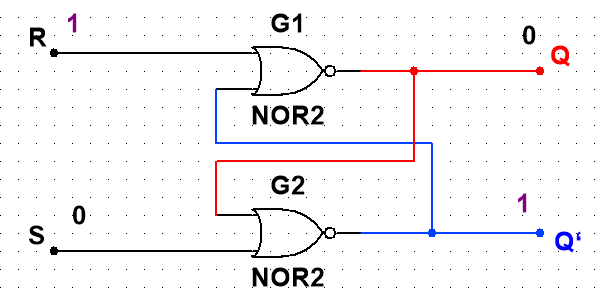

(1)当RD=1、SD=0时,如图:

此时Q控制Q’,Q=0,则Q’=1,即锁存器处于0状态。

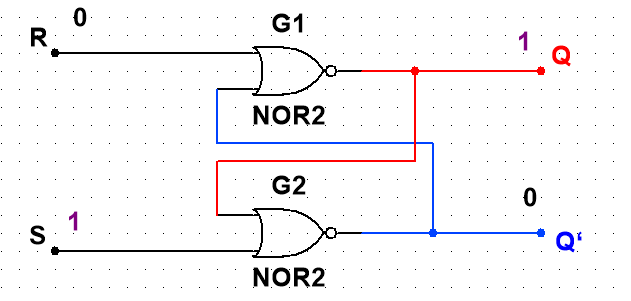

(2)当RD=0、SD=1时,如图:

此时Q’控制Q,Q’=0,则Q=1,即锁存器处于1状态。

(3)当RD=SD=0时,如下分析:

-

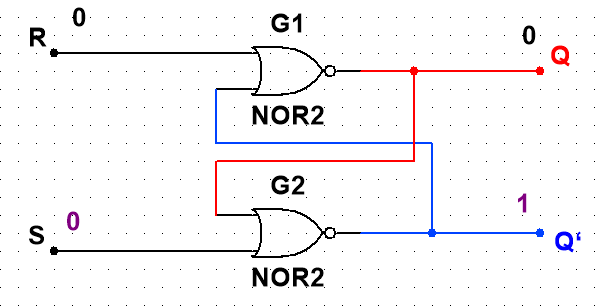

若状态(1)中的RD变为0,SD不变,即RD=SD=0时,如图:

此时,由于Q’端的高电平接回到G1的输入端,因而0状态保持不变,即Q=0、Q’=1。 -

若状态(2)中的SD变为0,RD不变,即RD=SD=0时,如图:

此时,由于Q端的高电平接回到G2的输入端,因而1状态保持不变,即Q=1、Q’=0。

(4)当RD=SD=1时,Q=Q’=0,既不是1状态,也不是0状态,属于不允许状态,所以SR锁存器的约束条件为RDSD=0。(此约束条件同样适用于与非门组成的SR锁存器)

三.特性表

a.特性表

| SD | RD | Q | Q* |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | * |

| 1 | 1 | 1 | * |

其中Q代表原来锁存器的状态(初态),Q*代表锁存器新的状态(次态)。

b.对特性表的理解

由第二部分可知,当SD=1、RD=0时,锁存器置1状态;当SD=0、RD=1时,锁存器置0状态;当SD=RD=0时,锁存器状态保持不变。

因此当SD=RD=0时,Q=Q*;当SD=1、RD=0时,无论Q=0/1,Q*=1;当SD=0、RD=1时,无论Q=0/1,Q*=0。

四.总结

| SD | RD | Q | Q* | 备注 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 保持不变 |

| 0 | 0 | 1 | 1 | 保持不变 |

| 1 | 0 | 0 | 1 | 置1状态 |

| 1 | 0 | 1 | 1 | 置1状态 |

| 0 | 1 | 0 | 0 | 置0状态 |

| 0 | 1 | 1 | 0 | 置0状态 |

| 1 | 1 | 0 | * | |

| 1 | 1 | 1 | * |

最后

以上就是不安高山最近收集整理的关于【数电】SR锁存器的全部内容,更多相关【数电】SR锁存器内容请搜索靠谱客的其他文章。

发表评论 取消回复