0x1 前言

计算机组成原理实验项目要求之一,使用Quartus II的VHDL语言制作一个 4位加法器和4位乘法器,并烧到试验箱中进行测试。

关于我所使用的试验箱DICE-E213的部分介绍请参照 Quartus II 实验 (一)——软件和试验箱DICE-E213的基本说明

0x2 四位乘法器

- 首先说明目录结构:

|

|-- and4a

|-- ls283

|-- mul4p

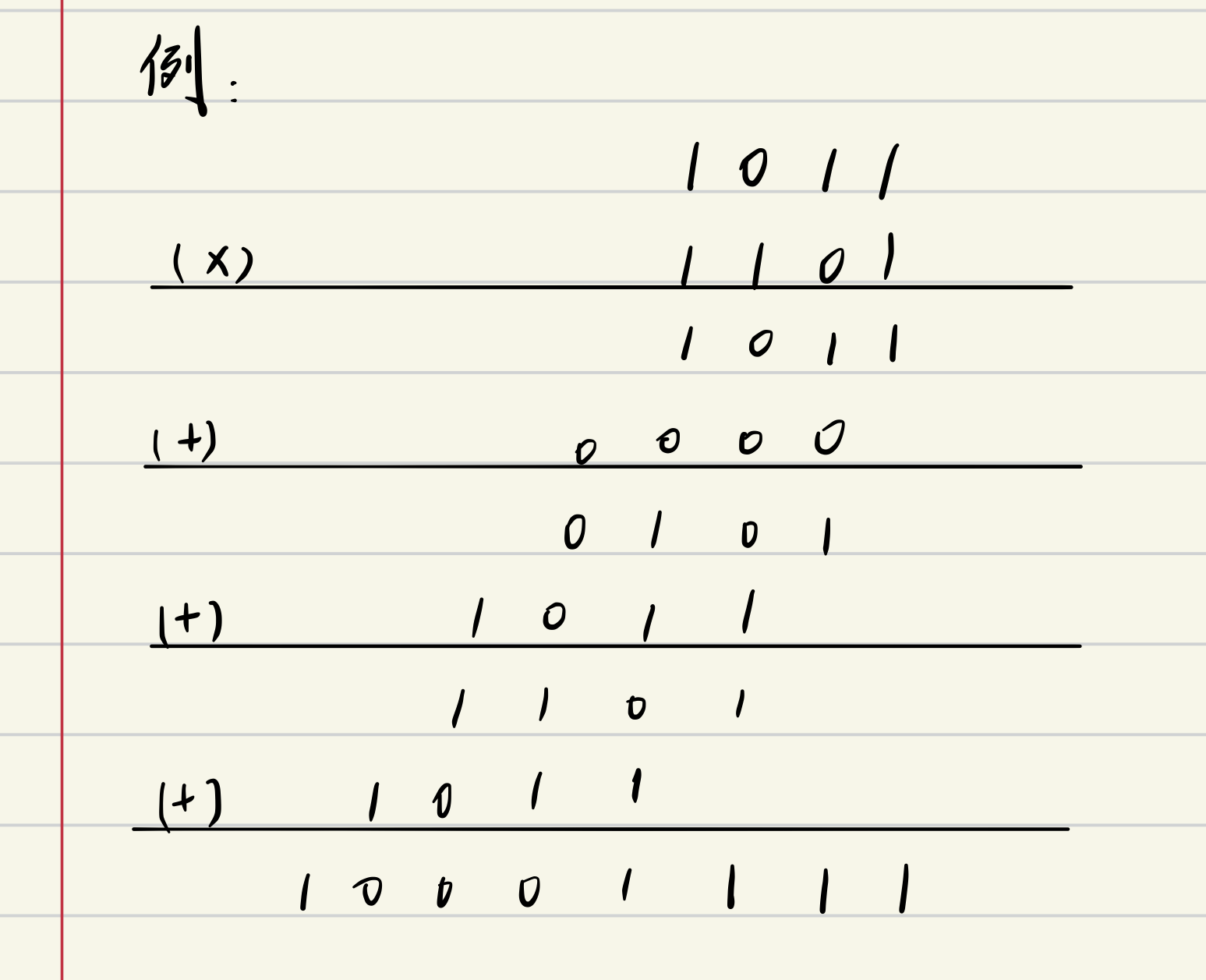

- 二进制加法过程

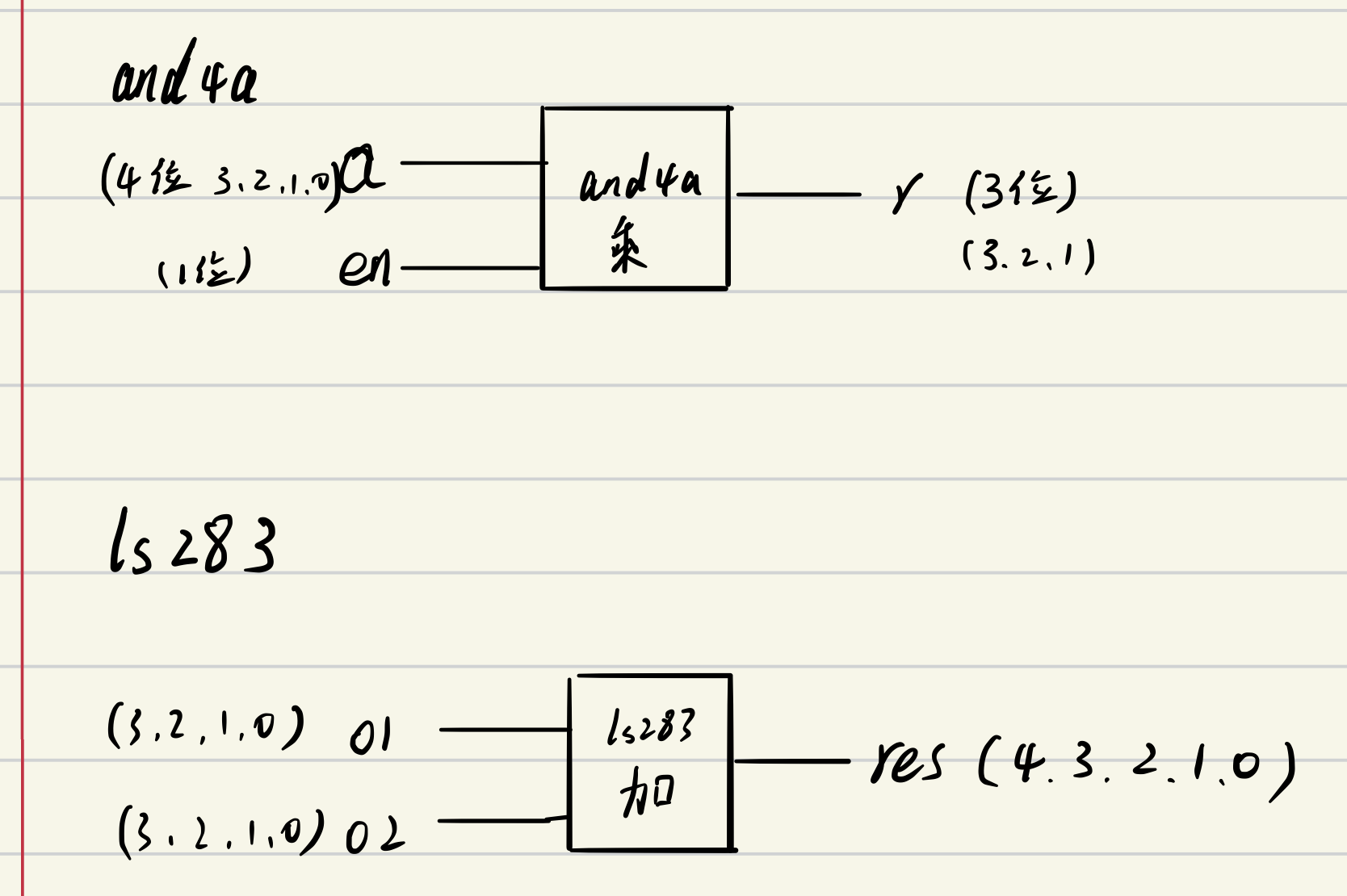

- 模块说明

- and4a 乘法模块,负责将 每一位乘数 与 被乘数 相乘

- ls283 加法模块,负责将中间结果相加。

>>> 需要特别注意的是上述每一个都是一个工程,完成以后需要进行编译;在主程序中需要将上面两个模块引入,才能正常调用。

-

and4a

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.std_logic_unsigned.all;

Entity and4a is

Port(a:in std_logic_vector(3 downto 0);

en:in std_logic;

r:out std_logic_vector(3 downto 0));

End and4a;

Architecture behave of and4a is

Begin

Process(en,a(3 downto 0))

Begin

If (en='1') then

r<=a;

Else

r<="0000";

End if;

End process;

End behave;

-

ls283

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.std_logic_unsigned.all;

Entity ls283 is

Port (o1,o2:in std_logic_vector(3 downto 0);

res:out std_logic_vector(4 downto 0));

End ls283;

Architecture behave of ls283 is

Begin

Process(o1,o2)

Begin

res<=('0'&o1)+('0'&o2);

End process;

End behave;

-

mul4p

这部分是主程序

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.std_logic_unsigned.all;

Entity mul4p is

Port (op1,op2:in std_logic_vector(3 downto 0);

result:out std_logic_vector(7 downto 0));

End mul4p;

Architecture count of mul4p is

component and4a port (a:in std_logic_vector(3 downto 0);

en:in std_logic;

r:out std_logic_vector(3 downto 0));

End component;

Component ls283 port (o1,o2:in std_logic_vector(3 downto 0);

res:out std_logic_vector(4 downto 0));

End component;

Signal sa:std_logic_vector(3 downto 0);

Signal sb:std_logic_vector(4 downto 0);

Signal sc:std_logic_vector(3 downto 0);

Signal sd:std_logic_vector(4 downto 0);

Signal se:std_logic_vector(3 downto 0);

Signal sf:std_logic_vector(3 downto 0);

Signal sg:std_logic_vector(3 downto 0);

--signal tmp1:std_logic;

Begin

sg<=('0'&sf (3 downto 1));

--tmp1<=op1(1);

u0:and4a port map(a=>op2,en=>op1(1),r=>se);

U1:and4a port map(a=>op2,en=>op1(3),r=>sa);

U2:ls283 port map(o1=>sb(4 downto 1),o2=>sa,res=>result(7 downto 3));

U3:and4a port map(a=>op2,en=>op1(2),r=>sc);

U4:ls283 port map(o1=>sc,o2=>sd(4 downto 1),res=>sb);

u5:ls283 port map(o1=>sg,o2=>se,res=>sd);

u6:and4a port map(a=>op2,en=>op1(0),r=>sf);

result(0)<=sf(0);

result(1)<=sd(0);

result(2)<=sb(0);

--result(7 downto 0)<="00000000";

End count;

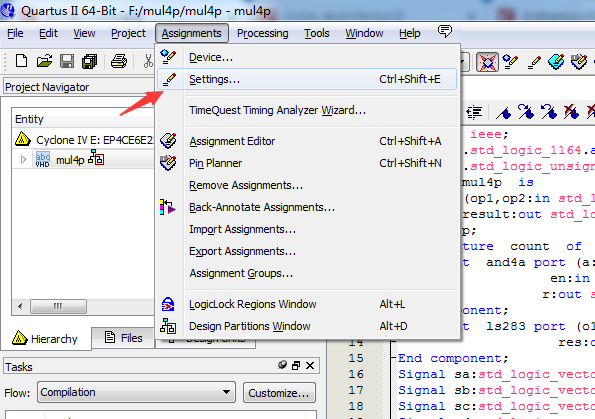

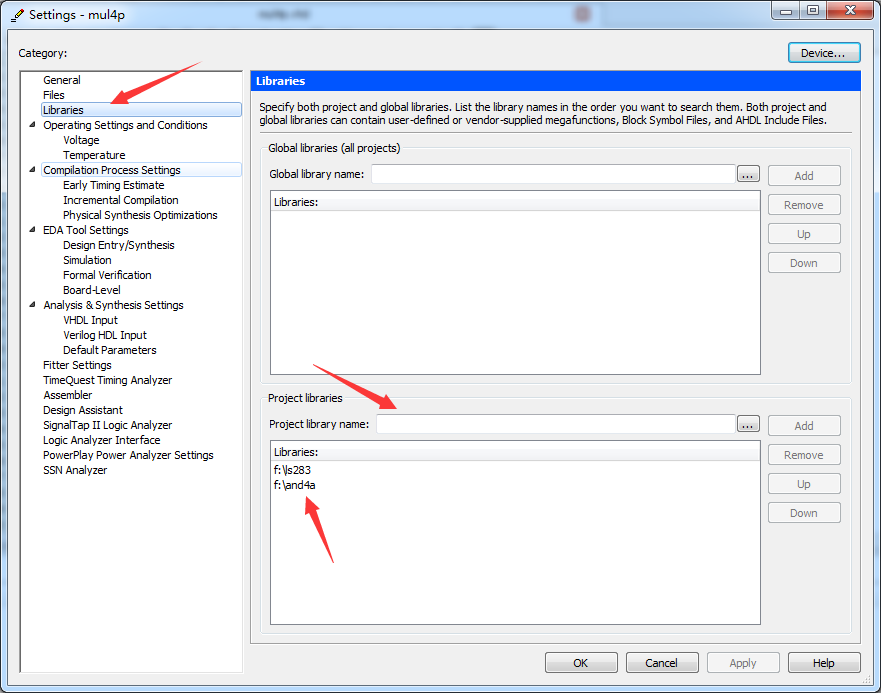

将上面两个模块引入主程序工程的方法是:

如图所示将另外两个工程的文件夹引入主程序工程。

编译!

-

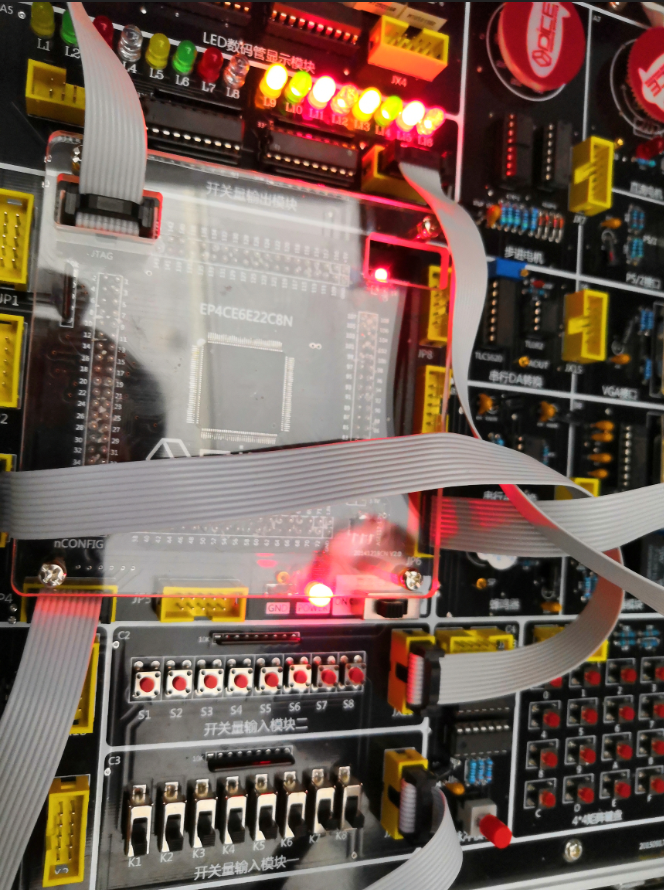

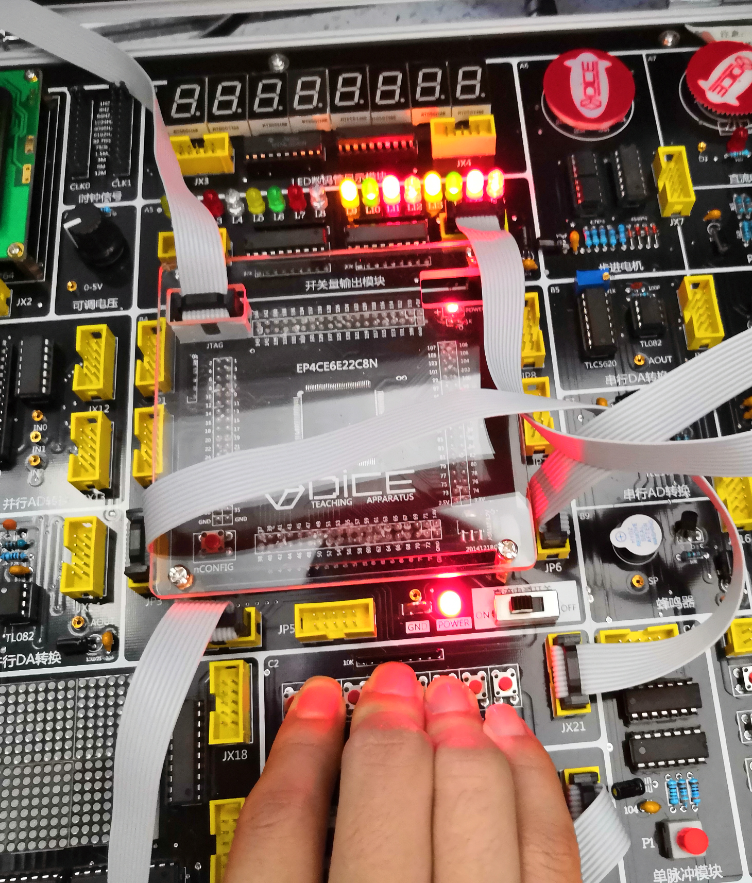

上电!烧进实验箱

这个过程不在赘述,过程中如出现问题,可以参考 Quartus II 实验 (一)——软件和试验箱DICE-E213的基本说明

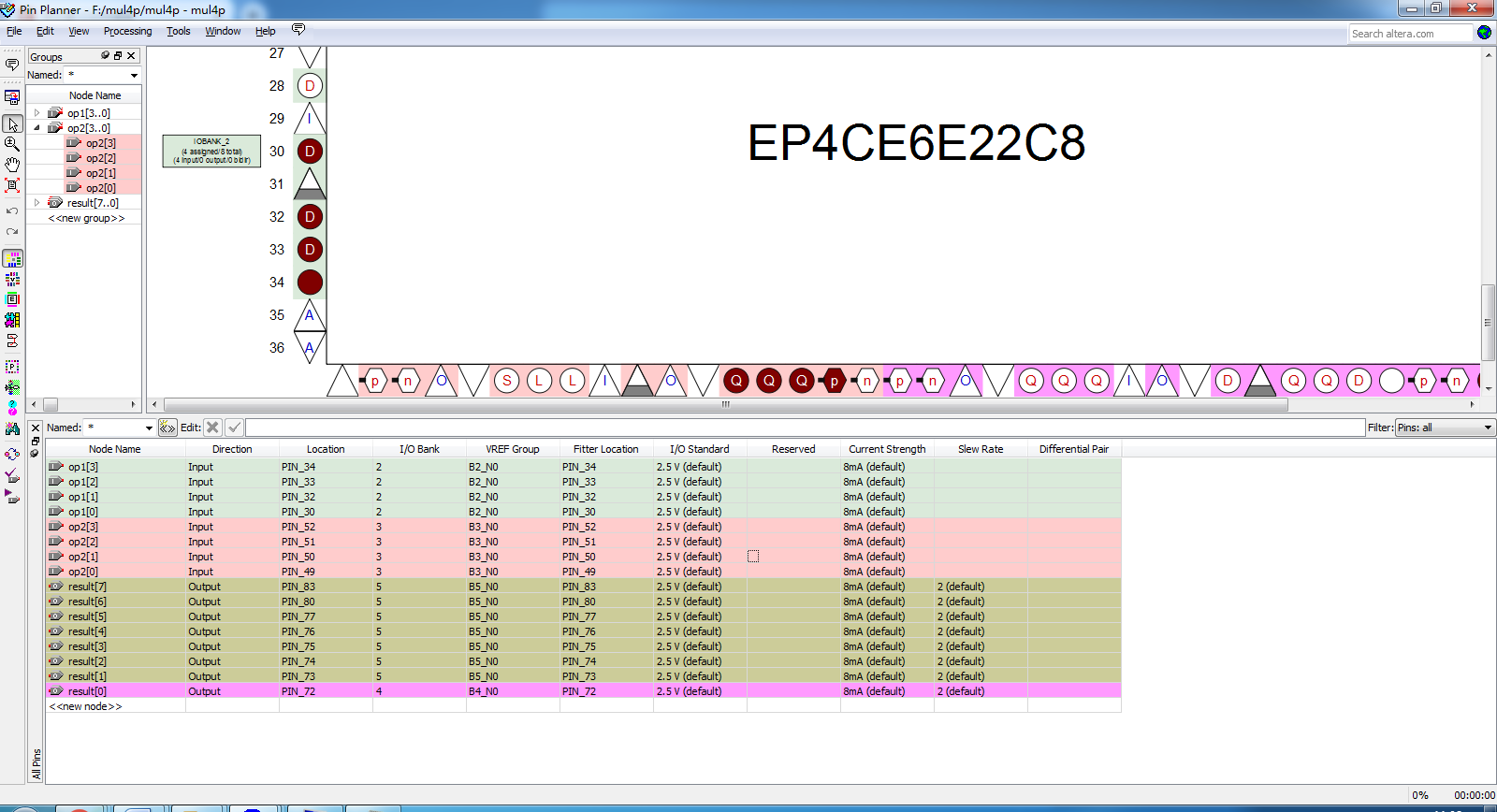

- 自定义引脚如图所示:

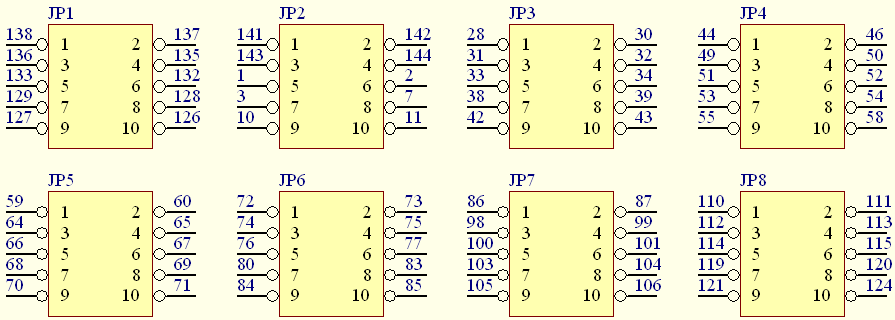

- 试验箱引脚组参考图(试验箱参考文档):

参照上图不难看出,我使用的引脚组是

输入1:JP3(2,4,5,6)

输入2:JP4(3,4,5,6)

输出:JP6(1,2,3,4,5,6,7,8)

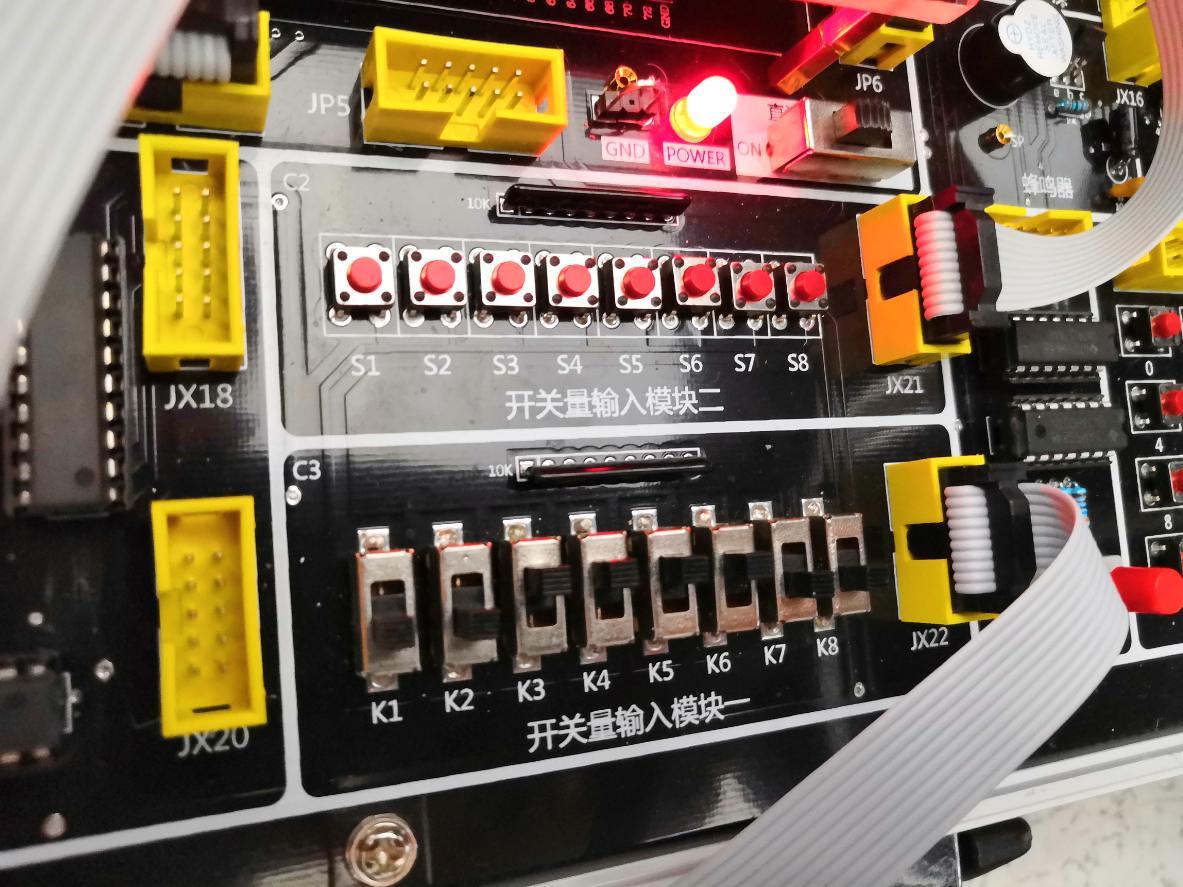

测试之前说说明一下:对于本实验箱:按钮输入的一组:按下0弹出1,对于推动开关输入的一组:推上1推下0,输出灯泡:亮0灭1。

测试试验箱的流程在有 Quartus II 实验 (一)——软件和试验箱DICE-E213的基本说明 详细介绍。

-

测试

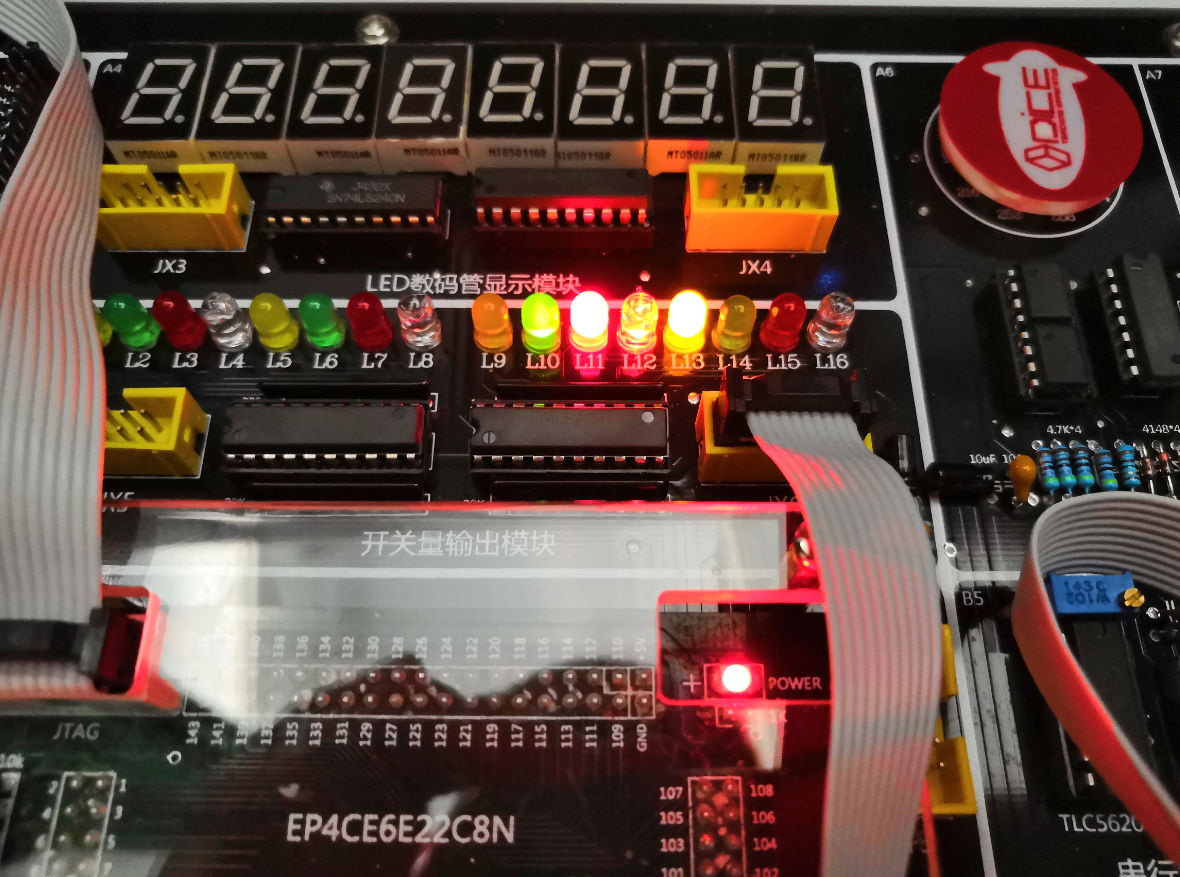

此时上排按钮表示1111,下派开关输入量为0000,结果0000 0000 灯全亮。

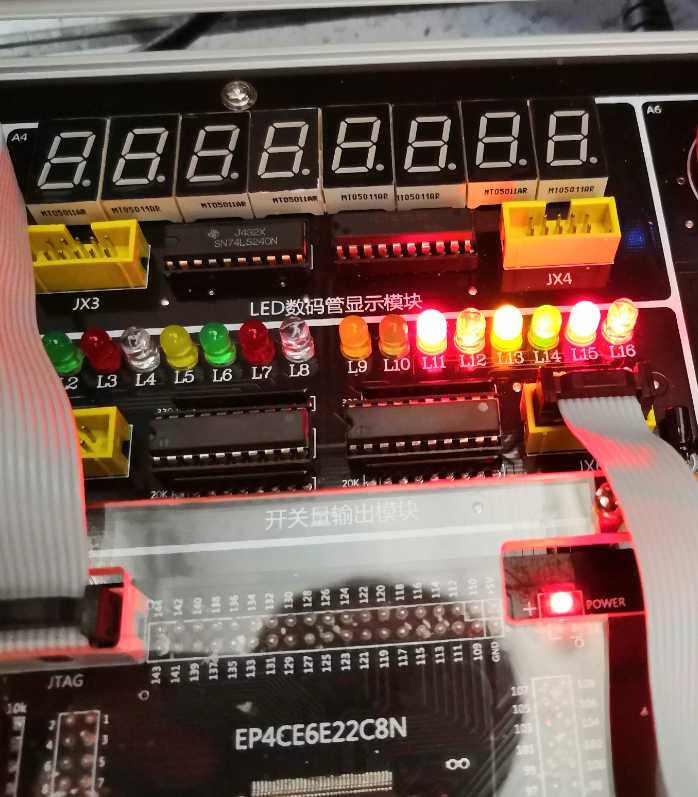

此时上排1111,下排1111,结果应为225 即 11100001

此时上排1000,下排1100,结果应为3,即 0000 0011

当上排按钮全部按下,上排0000,无论下派为何值,结果都为0000

-

结果正确,实验结束!

0x3四位加法器

操作和乘法器一样,不再赘述。

只做一点简要说明:

结构:halfadd-->fulladd-->adder4

贴出代码

- halfadd

Library ieee;

Use ieee.std_logic_1164.all;

Entity halfadd is

Port(a,b:in std_logic;

S,c:out std_logic);

end halfadd;

Architecture add of halfadd is

begin

S<=a xor b;

c<=a and b;

end;- fulladd

Library ieee;

Use ieee.std_logic_1164.all;

Entity fulladd is

Port(a,b,cin:in std_logic;

S,c:out std_logic);

end fulladd;

Architecture add of fulladd is

signal m,n,k:std_logic;

component halfadd is

Port(a,b:in std_logic;

S,c:out std_logic);

end component;

begin

U0:halfadd port map(a,b,m,n);

U1:halfadd port map(m,cin,S,k);

c<=n or k;

end;- adder4

Library ieee;

Use ieee.std_logic_1164.all;

Entity adder4 is

Port(a,b:in std_logic_vector(3 downto 0);

cin:in std_logic;

S:out std_logic_vector(3 downto 0);

co:out std_logic);

end adder4;

Architecture add of adder4 is

signal c:std_logic_vector(3 downto 0);

component fulladd is

Port(a,b,cin:in std_logic;

S,c:out std_logic);

end component;

begin

U0:fulladd port map(a(0),b(0),cin,S(0),c(0));

U1:fulladd port map(a(1),b(1),c(0),S(1),c(1));

U2:fulladd port map(a(2),b(2),c(1),S(2),c(2));

U3:fulladd port map(a(3),b(3),c(2),S(3),co);

end;最后说一点:工程路径不能有中文。

0x4 在此给出两份文件供大家参考

VHDL 4位加法器 VHDL 4位乘法器 http://sudo.ys168.com/ 公共下载区

备用链接:https://download.csdn.net/download/qq_41420747/11248001

在试验过程中如有错误,欢迎留言,讨论,也欢迎指出我的错误。

最后

以上就是高贵季节最近收集整理的关于Quartus II 实验 (二)——VHDL 4位加法器和4位乘法器0x1 前言 0x2 四位乘法器0x3四位加法器0x4 在此给出两份文件供大家参考的全部内容,更多相关Quartus内容请搜索靠谱客的其他文章。

发表评论 取消回复