格雷码是一种常见的编码方式,相邻状态间只有一位不同;这就意味着相邻两个状态间进行转换时,只有一位发生变化,因而极大的减小了出错几率。(反之,如果使用二进制编码,如011->100时三位均发生改变,因此出错的机率就会大大增加)。格雷码以及其余常见编码的知识详见:

Verilog常见编码方式:二进制码、格雷码、独热码

如上所述,格雷码作为一种错误最小化的编码方式,常用于状态机等多种场合。二进制与格雷码相互转换的问题也很可能遇到,此处就针对这一问题进行分析与仿真。

目录

一、格雷码与二进制码

二、二进制与格雷码的转换

三、仿真验证

四、参考文献:

一、格雷码与二进制码

以3位二进制码和格雷码作为示例,演示两者的编码方式以及相互关系:

| 编号 | 二进制 | 格雷码 |

| 0 | 000 | 000 |

| 1 | 001 | 001 |

| 2 | 010 | 011 |

| 3 | 011 | 010 |

| 4 | 100 | 110 |

| 5 | 101 | 111 |

| 6 | 110 | 101 |

| 7 | 111 | 100 |

二、二进制与格雷码的转换

1、二进制码->格雷码

方式1:从最右边一位起,依次将每一位与左边一位异或(XOR),作为对应格雷码该位的值,最左边一位不变(相当于左边是0);

(Verilog中利用右移与亦或,可以方便的实现二进制到格雷码的转换)

方式2:直接使用条件判断语句如:case语句

2、格雷码->二进制码

方式1:从左边第二位起,将每位与左边一位解码后的值异或,作为该位解码后的值(最左边一位依然不变)。

(如何用Verilog实现?转换结果与已转换位的解码值有关,因此难以像二级制-格雷码转换时一步得到。只能通过循环,历经好几个时钟周期才能转换结束)

方式2:直接使用条件判断语句如:case语句

三、仿真验证

以三位二进制码转换为格雷码为例,进行仿真验证如下:

实现代码如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/03/17 20:14:40

// Design Name:

// Module Name: bin2gray

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

//module bin2gray(

//input clk,

//input rst_n,

//input [2:0]bin,

//output reg [2:0]gout

// );

mid_signal declaration

//reg [2:0]ls_bin;

function declaration

//always@(posedge clk or negedge rst_n)

//begin

// if(!rst_n)

// begin

// gout <= 3'b000;

// ls_bin <= 3'b000;

// end

// else

// begin

// ls_bin <= bin >> 1;

// gout <= ls_bin ^ bin;

// end

//end

//endmodule

module bin2gray(

input rst_n,

input [2:0]bin,

output reg [2:0]gout

);

// mid_signal declaration

reg [2:0]ls_bin;

// function declaration

always@(*)

begin

if(!rst_n)

begin

gout = 3'b000;

ls_bin = 3'b000;

end

else

begin

ls_bin = bin >> 1;

gout = ls_bin ^ bin;

end

end

endmodule

测试文件如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/03/17 20:25:27

// Design Name:

// Module Name: bin_gray_tsb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module bin_gray_tsb(

);

// port declaration

//reg clk;

reg rst_n;

reg [2:0]bin;

wire [2:0]gout;

clk

//initial

//begin

// clk = 0;

// forever #10 clk = ~clk;

//end

// signal

initial

begin

rst_n = 1;

bin = 3'b000;

#15 rst_n = 0;

#20 rst_n = 1;

#20 bin = 3'b001;

#20 bin = 3'b010;

#20 bin = 3'b011;

#20 bin = 3'b100;

#20 bin = 3'b101;

#20 bin = 3'b110;

#20 bin = 3'b111;

end

// instance

bin2gray mb2g(

// .clk(clk),

.rst_n(rst_n),

.bin(bin),

.gout(gout)

);

endmodule

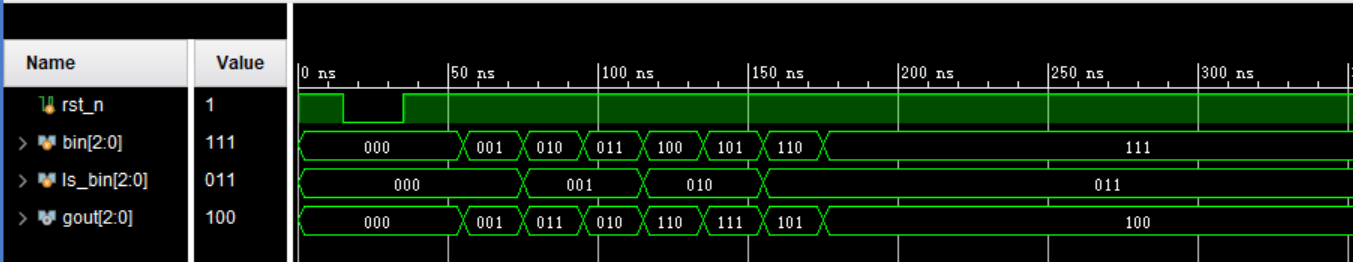

仿真结果如下:

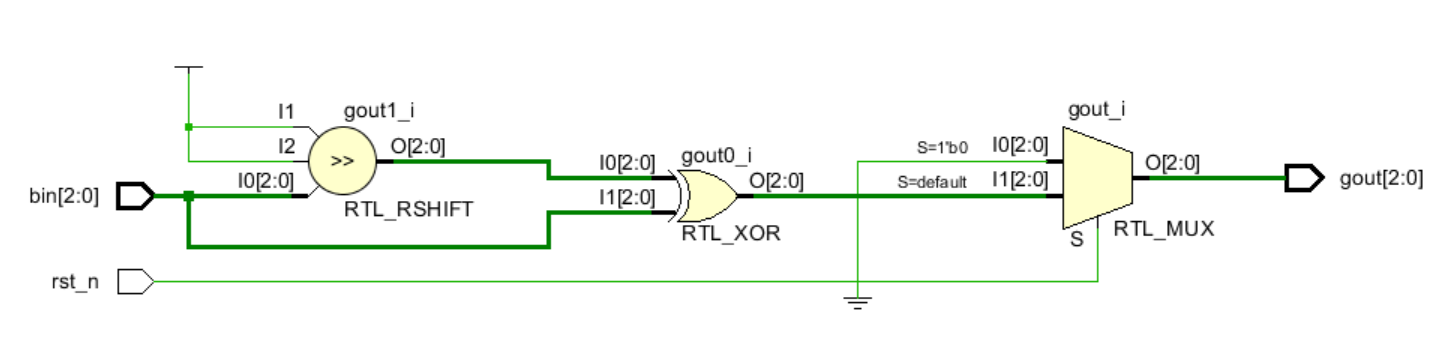

RTL电路如下:

发现,时序逻辑写法反而没有组合逻辑写法方便;

四、参考文献:

Verilog常见编码方式:二进制码、格雷码、独热码

最后

以上就是高贵季节最近收集整理的关于Verilog实现二进制码与格雷码转换的全部内容,更多相关Verilog实现二进制码与格雷码转换内容请搜索靠谱客的其他文章。

发表评论 取消回复