对于现在design中例化好的icg以及工具插进去的icg,不存在clock gating check的问题,因为clock gating 搞成了一个lib cell,不再是latch加上与门的组合。不过design中除了这些icg,还有一些的clock gating check的出现,这些是designer有意或者无意的写法导致。下面介绍什么样的电路可能会被认为是clock gating

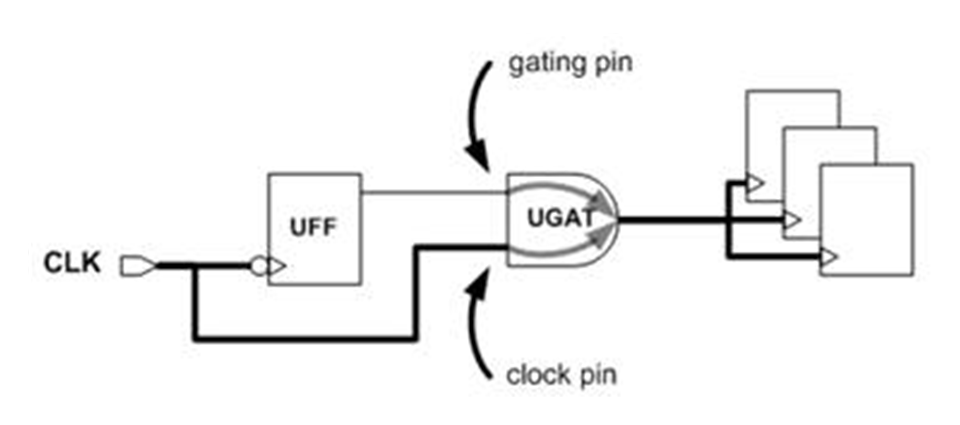

图1

如上图所示的为典型的clock gate电路。其中需要满足的几项条件:

- Gate cell的两个pin必须有一个流过clock

- clock pin流过clock必须是用作clock,后面drive了reg的cp端口,如果只是clock use as data那么不会被认为是clock gate check

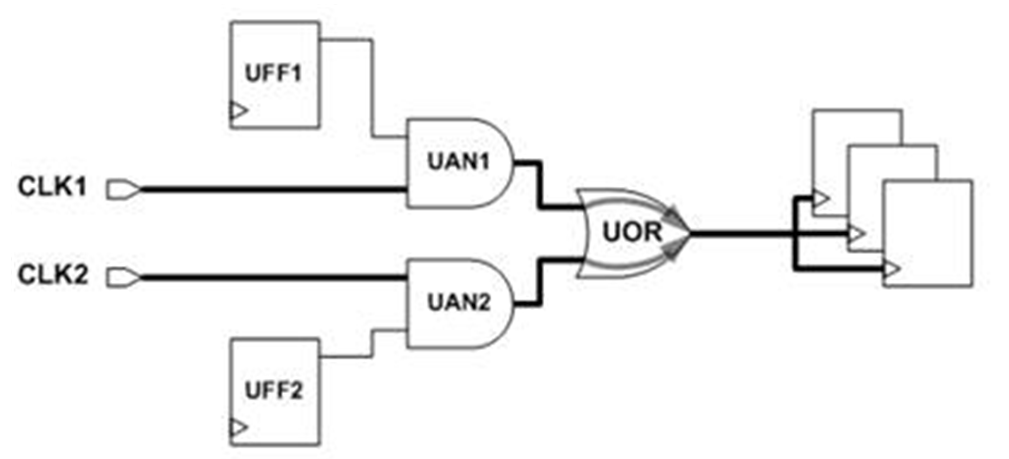

- gate cell的两个pin不能同时为真的clock(2.所描述的clock为真的clock)如图2所示,这种情况不被认为是clock gating check

- 如果两个pin都是clock,只有一个流了下去,那么也可以认为是clock gating check,如图3所示,generated打断了一个clock的流通。

图2

图3

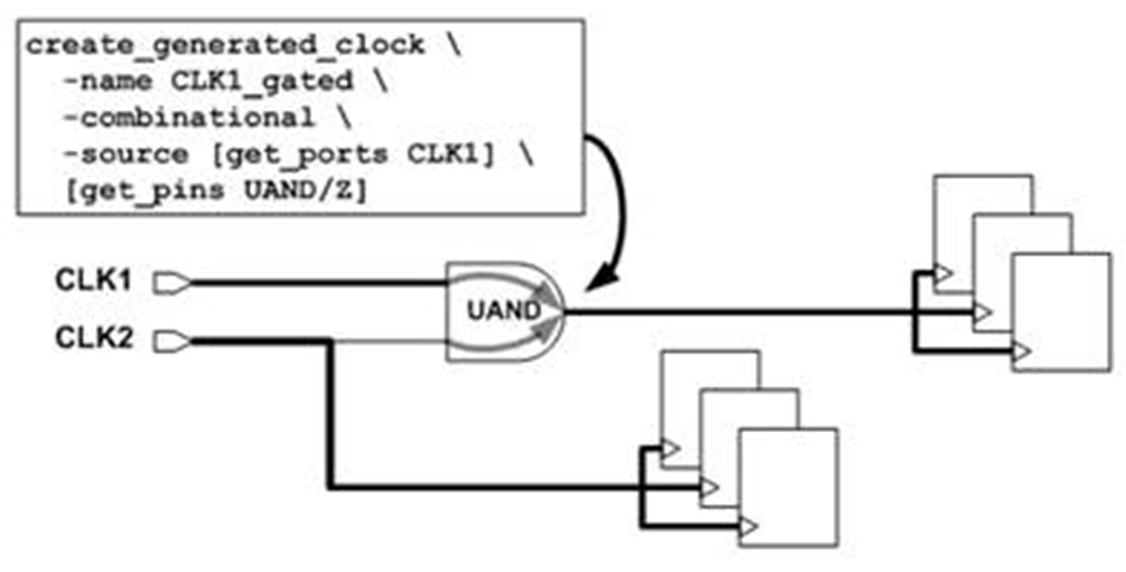

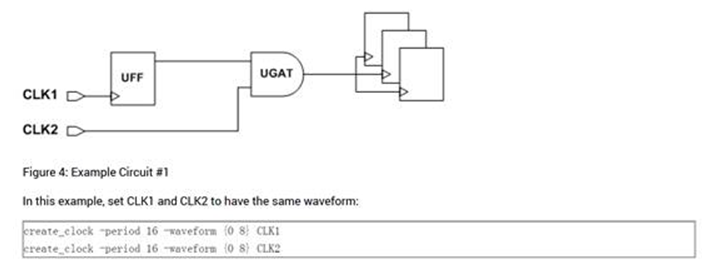

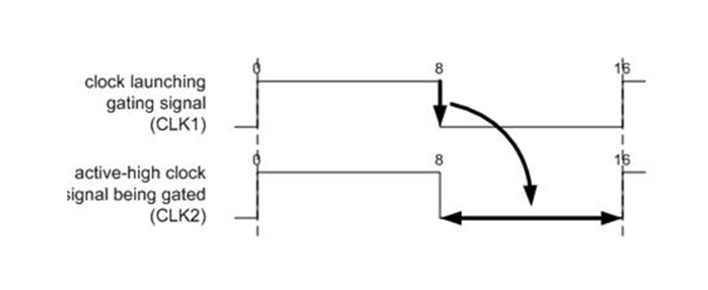

对于gate timing的检查。对于一个and门来说,一个en pin对一个clock pin进行gate,那么我们需要en pin在clock pin的低电平阶段变化,这样才不会影响最终的clock的输出信号。因为在clock的高电平处发生变化,可能会产生clock的毛刺出来,如图4所示。因此我们可以把AND和NADN门的gate check认为是高电平触发。同理OR或者NOR门的gate check认为是低电平触发。

图4

经过图4的分析,再看下面的例子就会很清晰了。途中是典型的and 门的clock gating 检查。我们期望enable数据在CLK的低电平区域内到达。

图5

图5

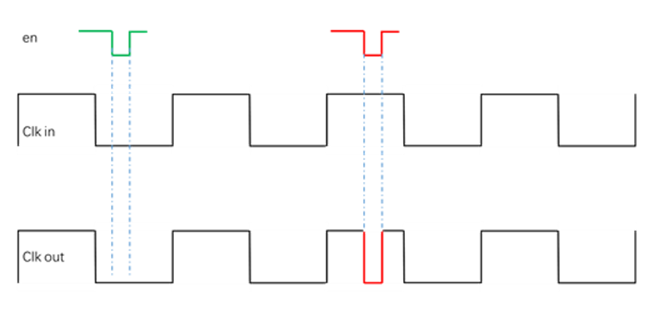

从波形中可以看到,CLK1的EN数据在8倒16s内到达,才不会对CLK2的时钟造成毛刺。而en的发送沿是CLK1的第一个上升沿,也就是0ns。因此可以得到hold 检查和setup检查。无论对于setup还是hold检查,都期望数据能够落到8-16ns内,因此当UFF发送数据的同时,对于hold来说在数据传递到UGAT的数据端口时候,期望CLK2已经在8ns处了,因此对于hold来说,有天然的8ns的clk path latency,非常不容易满足。而对于setup,只要数据送到UGAT的时间长度在16ns之前就可以,也就是setup有很大的裕度。

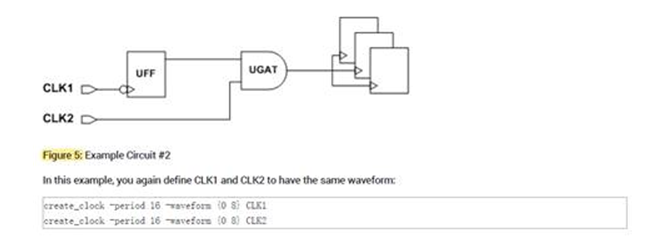

Hold的检查因为需要en在8s后到达and的en pin,所以有较大的vio。Setup则有较大的裕度。这个时候可以通过改变latch的采样方式,把相关的数据发送沿朝后推半个周期,这样setup和hold都更容易meet。如下图6所示

图6

此时UFF下降沿有效,那么UFF有效沿就在8ns处,此时只要满足UFF到UGAT的长度大于CLK2到UGAT的长度,就可以满足hold timing check。对于setup check,相应的裕度也变成了16-8=9ns

而关于OR门的gating 检查也是类似的情况,唯一需要注意的是我们期望en信号在clk的高电平还是低电平来,才不会对我们所需的clk产生毛刺。OR门的timing check不再赘述。

最后

以上就是想人陪钢笔最近收集整理的关于STA -- clock gating check的全部内容,更多相关STA内容请搜索靠谱客的其他文章。

发表评论 取消回复