看别人写的脚本 和视频里教的还是不太一样啊 记录一下不懂的地方

IC设计 - 知乎

复杂时序约束 - 知乎

DesignComplier基本知识问答 - 百度文库

DC综合简单总结(1)

*****************set_dont_touch和set_dont_touch_network****************

?

在综合的过程中,为了不让DC工具自动优化一些我们不希望其优化的模块(比如CLK)我们通常都会设置set_ideal_network和set_dont_touch,我理解为前者在timing_report的时候忽略延迟,后者阻止DC插入buffer。

那么dont_touch的属性,能不能穿过logic?

set_dont_touch和set_dont_touch_network有什么区别,为什么普遍认为set_dont_touch_network会造成未知问题而不推荐使用?

对于ideal_net的这个属性,是不是说直接忽略了延迟,忽略了DRC,如果将clk设定为ideal_net,是不是就不用再设定dont_touch了?

说的有点混乱,请各位大神技术支持,小弟不胜感激!!

=

set_dont_touch不会穿过logic,可以用于cells, nets, references, 和 designs。你不希望DC碰的地方,都可以用它。

set_dont_touch_network可以穿过logic,可以用于clocks, pins, 或 ports,比上面的范围小。当你对设计不十分熟悉时,这个属性可能会传到你不希望的地方去。

ideal_net 顾名思义就是把这条net完全理想化--无穷大的驱动能力,没有延迟。有时会和上面的命令一起用。当你知道了它们的意思,如何使用取决于你的目的和得到的结果

?

对于Ideal_net这个属性,设置的时候有个no_propagate的属性,对于net来说一定要设这个,是不是就是为了阻止其穿过逻辑?那如果我设的是pin并且不加上no_propagate能穿过逻辑吗?

在建立clock的时候,我看到它会自动的设为ideal_net,但是却还是会计算延迟,会不会因为clock path有逻辑的原因?

=

set_ideal_net = set_ideal_network -no_propagate

clock net 如果被用作data,就会有delay,那是因为net上面挂的clk pin的负载,不是ideal net本身

?

我大体上明白了,clk在创建的时候,会默认为ideal net的,但当clk接入到data path的时候,D端就会考虑我clk上的负载,但并不会影响clk的ideal net的属性。

假如我的clk需要门电路做gating,gating后的时钟也有很大的扇出,那我为了忽略掉延迟,是不是需要在gating后重新给clk定义ideal net?因为ideal net不能穿过逻辑。

=

如果你的CG集成好的标准单元,它会自动继承ideal的属性。

*****************set_dont_touch和set_dont_touch_network****************

输入端口到时序器件的数据端口。

要求时间=T2+Tlatency-Tuncertainty_setup-Tsetup

到达时间=T1+Tlantency+Tinput_delay+Tlogic2

时序器件的输出管脚到输出端口

上图中:

要求时间=T2+Tlatency-Toutput_delay-Tuncertainty_setup

到达时间=T1+Tlatency+Tcell+Tlogic5

时序器件到时序器件

路径上的 cell 延迟由 input_transition 和 output_load(包括扇出 pin 上的 load)决定,这个由查抄表可以得到。

而 net 延迟是由 net 上的 R, C 决定的。在没有布局布线之前,我们不知道实际的 R, C 是多少, dc 根据互联线模型(set_wire_load_model)来计算出 R, C。然后根据得到的 R, C 计算出 net 上的延迟:Net_delay=R*C*OC其中系数 OC 是根据操作环境(set_opearting_conditions)中设置的 rc树模型得到。

一般的工艺库的操作环境有三种, WORST, TYPICAL, BEST,分别是最差,典型,最坏。

T=4,周期为4,Tdata为2,两个clk同时到达,slack=4-2=2,

setup check是latch和lauch间隔一个时钟周期,hold check才是在同一个时钟沿

input_transition输入信号的转换时间可以采用两种约束:

1 直接设置转换时间

set_input_transition 0.1 [get_ports A]

2 采用设置输入驱动能力,驱动能力越大,转换时间越小,驱动能力越小,转换时间越大

set_drive或者set_driving_cell

Slew Ratevs.Transition Time

首先,我要说明一下,slew和transition其实并非独立存在使用的词汇。在诸多教材中,一般是以slew rate和transition time,两个词组出现的。

Slew rate,信号改变的速率。

Transition time,信号改变的持续时间。

在静态时序分析(STA)中,一个上升或者下降的波形通常用slew rate来表征其跳变的快与慢。Transition time就是用来记录这个信号在两个电平之间的转换时间。

这里需要注意的是,transition time实际是slew rate的倒数。Transition time如果越大,那么slew rate就会越慢,反之亦然。

上图展示了一些CMOS器件的输出波形图。理想状态下,我们期望得到一个完美的方波,不过,这显然不够现实。实际上,由于对电容的充放电,一个数字信号的波形往往存在上升和下降的电压缓冲区间。

为了能量化这样的波形,我们近似采用一个线性上升或者下降的信号来模拟真实信号波形。注意到,真实信号波形里,不管是上升还是下降的时候,都会存在一定时间的线性区域。

这个线性区域的起点和终点,可能因为某些估算模型而有所不同。在STA中,我们有时候会采用比较宽松的约束模式,例如20%/80%、10%/90%。

当然,我们也可以采用激进一些的模式,如30%/70%。

在一个线性时序模型里,一个信号经过一个时序单元可能产生两种新的信号波形。

当输出信号的slew rate比输入信号的要快,也就是transition time变短了,说明这个单元对这个信号起到了增强驱动的作用。

反之,当输出信号的slew rate比输入信号还要慢,就是transition time变长了,说明这个单元对这个信号起到了削弱驱动的作用。可能的原因是,这个单元的输出端驱动了较大的负载。

所以,当我们要描述一个信号电平有所变化的时候,记得要用slew rate来表述快慢,用transition time来描述持续时间。

》》对于 cell 的延迟,dc 是根据 input_transition 和 out_load 对应的查找表来计算的。

》》 对于 net 的延迟,dc 是根据 wire_load_model 中的fanout_length 和 resistance,capacitance, area 的查找表计算的。

》》 负载其实有两个概念,一个是阻性负载,这个负载当你提供了足够的驱动力就能够正确输出,否则电压就不对;另一个是容性负载,这个负载一般在系统里头,和系统能跑到什么速度相关。

一个输出驱动力大的话就能够带更大的负载,从这个意义上说,认为驱动=负载也是可以理解的。但其实这两个概念还是有些区别,侧重点不同。你上面也引用了,“电路的负载能力是下一级的load(即电容)总和”,这都是完全不同的两个量纲,怎么会一样。系统设计上,假设你需要跑10MHz的频率,你需要10mA的驱动力,则同一个容性负载上,要跑到20MHz的频率,你就需要20mA的驱动力。

作者:飞奔的大虎

链接:https://www.jianshu.com/p/88269d9041d3

来源:简书

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

dont_touch 与dont_touch_network的区别

create_generated_clock

在数字IC设计中,芯片中各个模块的工作频率可能都不太一样。因此有了时钟产生电路(clock generation)。这个电路含有时钟切换电路,时钟分频,倍频电路以及clock reset电路。通常我们通过create_generated_clock来定义时钟分频和倍频电路后的时钟。

create_generated_clock 是用来说明generated clock与source clock的相位(边沿)关系。同时根据source clock找到master clock以及source clock 和master clock的关系, 最终会确定generated clock和master clock的相位(边沿)关系。

在genereated clock的时候一定要明确generated clock与master clock的相位关系(rise->rise or rise->fall or fall->rise or fall->fall), 这些关系由桥梁source clock嫁接,所以有了generated clock和source clock,以及source clock和master clock的关系。

如果根据声明找到的generated clock 和master clock的关系和实际的关系不一致,则会造成一些分析错误。比如静态时序分析STA的时候找不到generated clock和source clock相位关系,会将generated clock的source latency 设置为0。

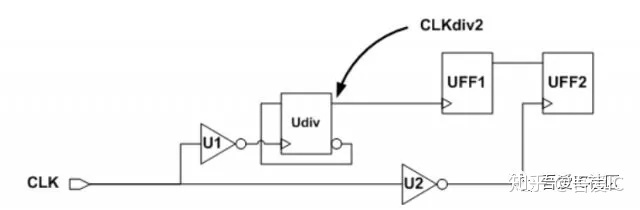

如下图为一个简单的数字IC电路及其波形图。

create_clock -period 10 CLK

create_generated_clock -name CLKdiv2

-divide_by 2

-source CLK

[get_pins Udiv/Q]

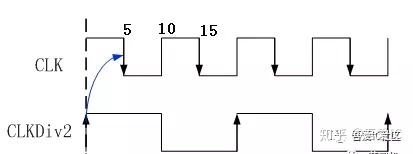

根据上面定义,generated_clock是定义在二分频的输出端Q上,其source为CLK。但是我们知道Udiv这个寄存器的时钟端CK与CLK是反相的(即相位差180度)。

根据声明,generated 和master clock的关系如下(工具会根据source clock 找到master clock,并确定source clock 和master clock的关系,当前source clock即master clock)。但实际电路是source clock和master clock是存在180相位差的,因此以上定义的generated_clock是不正确的。

正确的波形图应该如下图所示:

所以UFF1到UFF2的setup检查为launch clock edge为T=5ns时刻,capture clock edge为T=15ns时刻(默认为single cycle path)。

因此,我们可以通过以下两种方法来定义分频后的时钟

1.改变generated clock的source,即让generated clock和source clock的路径唯一且单一(单一是指,声明的相位边沿关系和实际的相位边沿关系一致)。

一般做法就是将source clock设置在触发器的clock端。如下:create_generated_clock -name CLKdiv2

-divide_by 2

-source [get_pins Udiv/CLK]

[get_pins Udiv/Q]

这样generated clock和source clock的关系和声明的一致。 工具会根据声明的source clock 找到它的master clock,同时确定source clock和master clock相位相反的关系, 由此就确定了generated clock和master clock的关系。

2.直接声明generated clock和master clock的相位边沿关系。如下:

create_generated_clock

-name CLKdiv2

-edges {2 4 6}

-source CLK

[get_pins Udiv/Q]

虽然这两种方法都可以用来定义generated_clock,但是考虑到后期review constraint的便利性,强烈建议使用第二种方式来实现(实际项目中都是采用这种方法)。

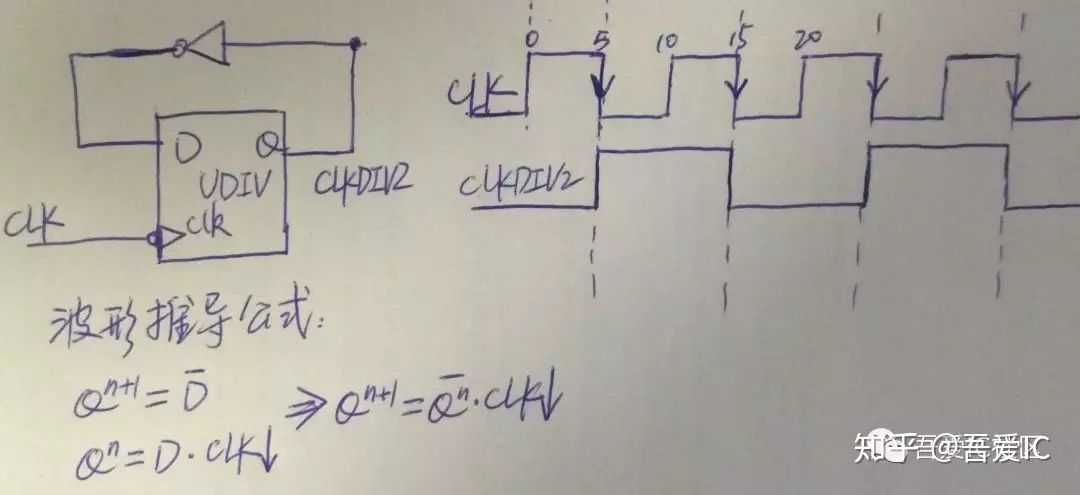

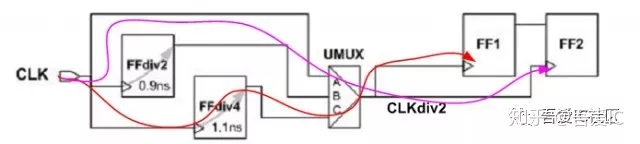

create_generated_clock有多个master_clock的情况

上文讲到了 create_generated_clock 的作用,提到工具会根据声明找到 generated clock 和 source clock 的相位(边沿)关系,同时根据 source clock 找到 master clock 顺便确定 source clock 和 master clock 的关系,最终确定 generated clock 的关系。但是如果有时候虽然确定了 master clock 和 generated 的相位(边沿)关系,但是 master clock 到 generated clock 的路径有很多的时候,也会导致 STA 分析问题。

create_clock -period 10 CLK

create_generated_clock -name CLKdiv2 -divide_by 2 -source FFdiv2/CLK UMUX/Y -master CLK -add

create_generated_clock -name CLKdiv4 -divide_by 4 -source FFdiv4/CLK UMUX/Y -master CLK -add

set_clock_groups -physically_exclusive -group {CLK} -group {CLKdiv2} -group {CLKdiv4}

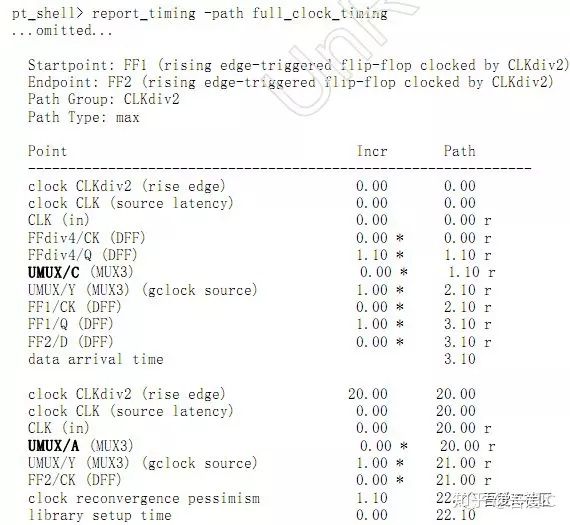

此时,PT时序分析报告如下:

可以知道source latency 选择了不同路径

所以在声明generated clock的时候不仅要保证generated clock 和master clock 相位边沿关系和实际的一致,还要保证generated clock和master clock的路径一。

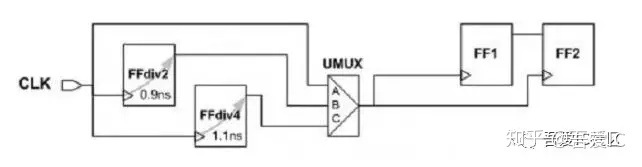

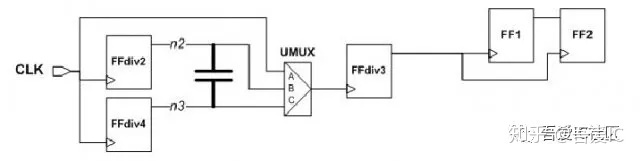

如下图,列出了可以声明唯一generated clock点。

同时考虑到选择器之前各个时钟间有crosstalk,选择器之后没有crosstalk,所以声明如下:Create_clock -period 10 CLK

#####define divide_by_2,divide_by_4 clocks

Create_generated_clock -name CLKdiv2 -divide_by_2 FFdiv2/Q -source FFdiv2/CK

Create_generated_clock -name CLKdiv4 -divide_by_4 FFdiv4/Q -source FFdiv4/CK

#####create clocks arriving at MUX inputs

Create_generated_clock -name CLK_mux -combinational UMUX/A -source UMUX/A

Create_generated_clock -name CLKdiv2_mux -combinational UMUX/B -source UMUX/B

Create_generated_clock -name CLKdiv4_mux -combinational UMUX/C -source UMUX/C

#####define clock at FFdiv3

Create_generated_clock -name CLK_mux_div3 -divide_by 3 -source FFdiv3/CK -master CLK_mux -add

Create_generated_clock -name CLKdiv2_mux_div3 -divide_by 3 -source FFdiv3/CK -master CLKdiv2_mux -add

Create_generated_clock -name CLKdiv4_mux_div3 -divide_by 3 -source FFdiv3/CK -master CLKdiv4_mux -add

####apply physical exclusivity

Set_clock_groups -physically_exclusive

-group {CLK_mux CLK_mux_div3}

-group {CLKdiv2_mux CLKdiv2_mux_div3}

-group {CLKdiv4_mux CLKdiv4_mux_div3}

若直接将 CLKmux, clkdiv2_mux, clkdiv4_mux 省略,然后分别在MUX/Y端定义三个generated clock,其 source 设定为CLK, CLKdiv2, CLKdiv4,也是可以的。

思考题(2018年某SOC公司校园招聘数字后端笔试题)

对于这道数字IC后端实现题,如果你还不会做,请给自己敲个警钟。

芯片A端口OUT1/OUT2分别接到芯片B的D/CLK。芯片A端口约束如下:

create_clock -name CLK -period 10 -waveform {0 5} [get_pins U1/Y]

create_generate_clock -name GCLK -source [get_pins U1/Y] -edge {1 3 7} -master_clock CLK [get_pins U2/Y]

create_generate_clock -name OUTCLK -source [get_pins U2/Y] -master_clock GCLK -divide_by 1 [get_ports OUT2]

set_output_delay -max 8 -clock OUTCLK [get_ports OUT1]

set_output_delay -min 1 -clock OUTCLK [get_ports OUT1]

Q1: 请问对于芯片B, D到CLK的setup/hold check 要求分别是什么?

Q2: 画出CLK和GLCK 的波形?

Q3:如果要求从时钟源到OUT1/OUT2 delay等长,请问constraint怎么写?

如果你对作者分享的干货感兴趣,或者想与作者讨论交流的,欢迎关注公众号(id: ic-backend)。

DC综合中create_generated_clock问题 - 数字IC设计讨论(IC前端|FPGA|ASIC) - EETOP 创芯网论坛 (原名:电子顶级开发网) -

深度解析create_generated_clock - 知乎

和dc没关系 ,这是之前笔试题不会的东西随便找个地方抄一下

作者:吾爱IC

链接:https://zhuanlan.zhihu.com/p/509488300

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

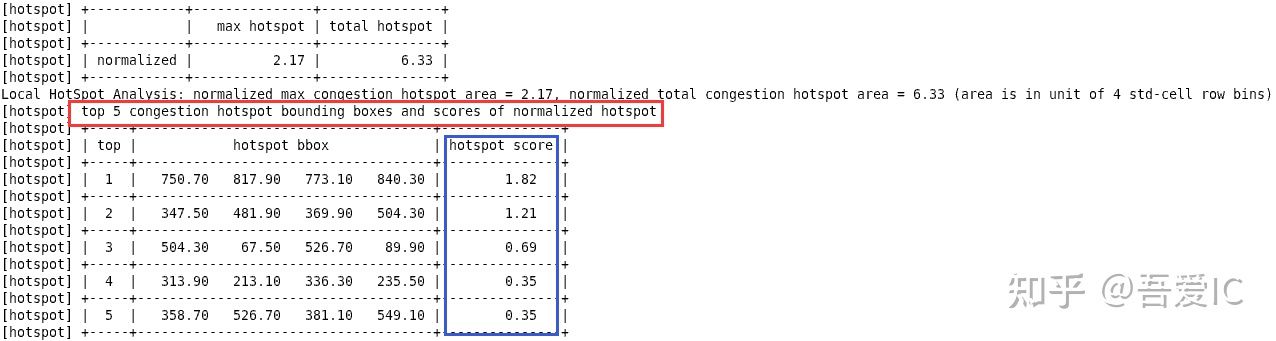

什么是hotspot?

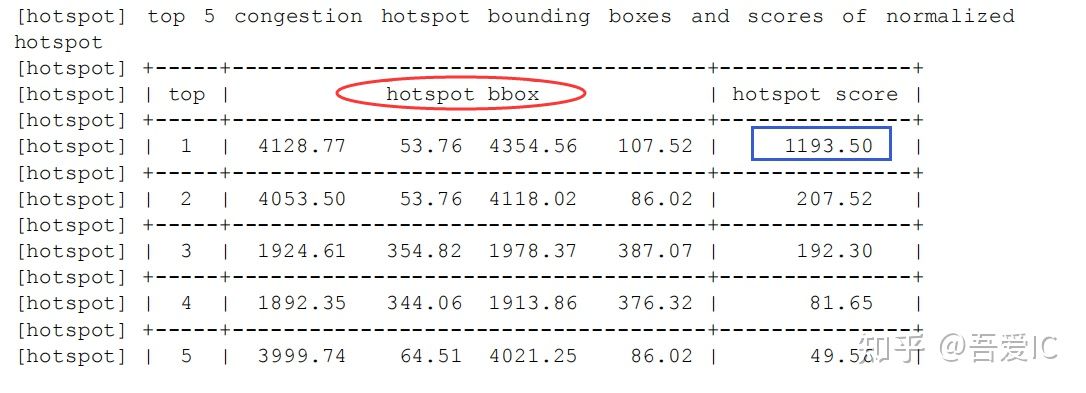

hotspot表征的是设计中congestion的热点,它是用面积来表示hotspot的分数。如果这个分数越高代表的是这个位置有congestion的点比较多。所以这个位置附近就有比较聚集的congestion问题。

工具跑完会报出设计中最差的五个hotspot点。这里如果报出来的五个点的hotspot值小于150,我们认为当前设计不存在非常聚集性的congestion。此时,如果overflow值大于2%,也是有机会能绕通的。

如果工具报出来的hotspot如下图所示,那么第一个点的坐标位置一定存在局部区域的绕线困难。即便此时整体overflow只有1%,此处位置可能也会有short。

最后

以上就是心灵美机器猫最近收集整理的关于【DC】学习笔记1的全部内容,更多相关【DC】学习笔记1内容请搜索靠谱客的其他文章。

发表评论 取消回复