时序约束(三)

前两节主要了解了一下时序分析和时序约束的概念以及根据自己在项目中遇到的时序问题,时序约束和不约束所产生的现象。这一节主要通过vivado工具通过工程实践来看一下时序的细节,同时建立对FPGA底层器件的认识。想用一个比较生活化的例子来理解时序的问题,思考了好长时间,终于找到一个,如下:

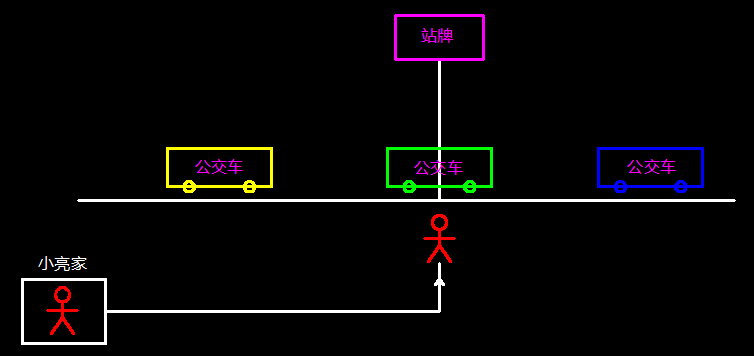

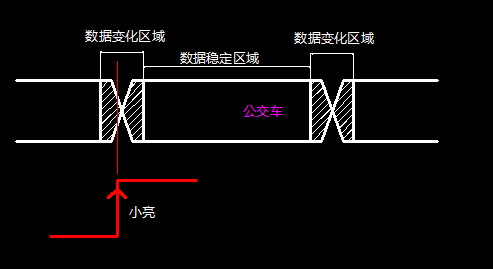

小亮是公司雇员,每天在小区门口搭乘公交上班,假如小亮要想上班不迟到,他就必须从家里出发走到公交站牌时,公交车正好停在那里(公交停留一分钟),并且上车。若果小亮走到公交站牌时,车还没来,或者车已经走了,小亮都会上班迟到!如下图:

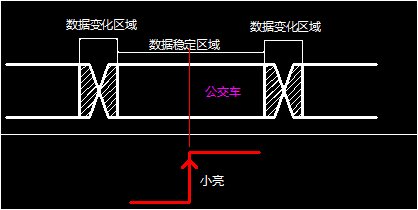

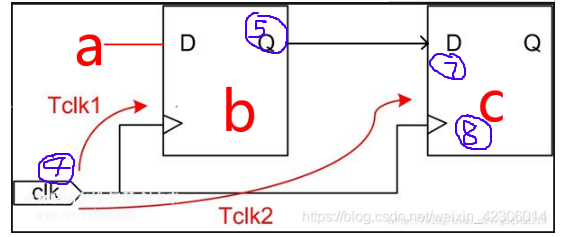

与时序模型做个对比,以下是时序图:

我们把时钟当做小亮,把数据当做公交车。从公交车的角度来讲,你要想搭乘我的车,必须在我停留的一分钟内到达,过期不候。从小亮的角度讲就是小亮到站,车必须在站内停留,否则我就迟到了!所以时序分析就是如果小亮没有搭乘上这一班公交,我们得看看是什么原因,倒地是小亮走得慢,还是公交堵车了。找到原因后我们要告诉小亮和公交司机,具体怎么做,就是时序约束。比如约束小亮走的快一些,或者出门早一些就能搭上公交。

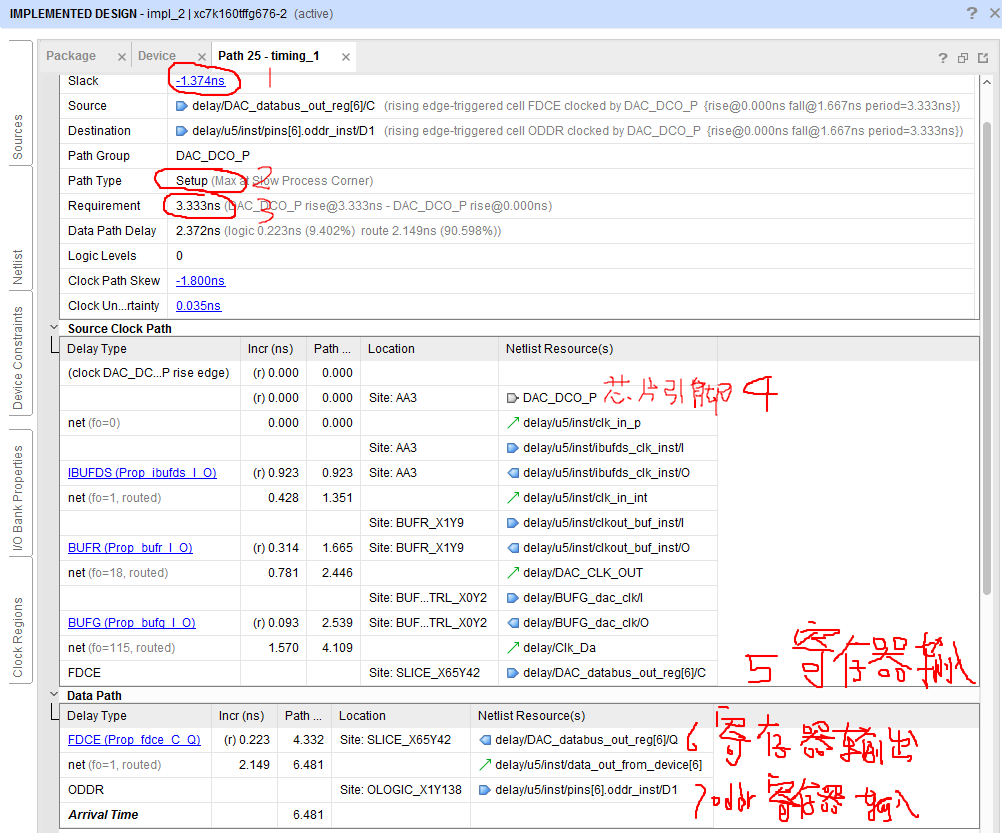

讲了这么多,我们来看一个时序违规的例子:

1.表示建立时间裕量

建立时间讲的是,时钟到来时,数据来没来的情况。建立时间裕量为负,表示时钟上升沿到来时,数据还没到,也就是说,小亮到公交站牌时,公交车还没来。

保持时间讲的是,时钟到来时,数据走没走的情况。保持时间裕量为负,表示时钟上升沿到来时,数据已经走了,也就是说,小亮到公交站牌时,公交车已经出发。

2.时序违规类型为建立时间类型。一共就两种,建立时间违规与保持时间违规。

3.表示两次时钟采样沿之间的时间间隔。同时域时为时钟采样周期,跨时域时为两次时钟采样沿之间的时间间隔。

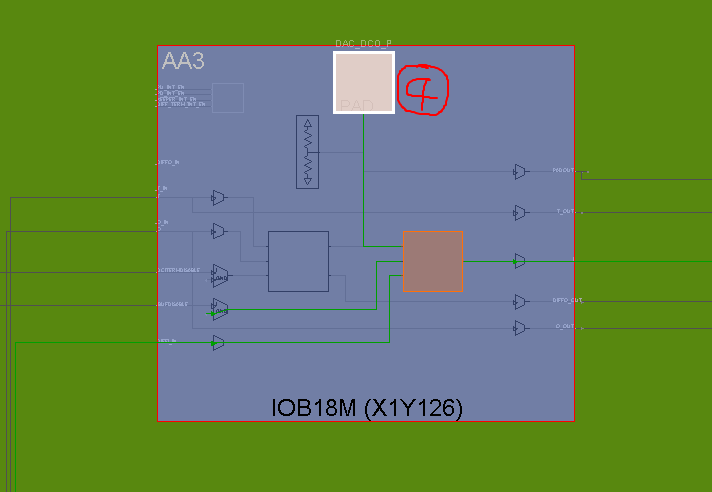

4.表示时钟输入FPGA时的芯片引脚。

5.表示时钟进入第一级寄存器时的时间。

6.表示数据从第一级寄存器出来时的时间。

7.数据到达第二级寄存器输入端时的时间。

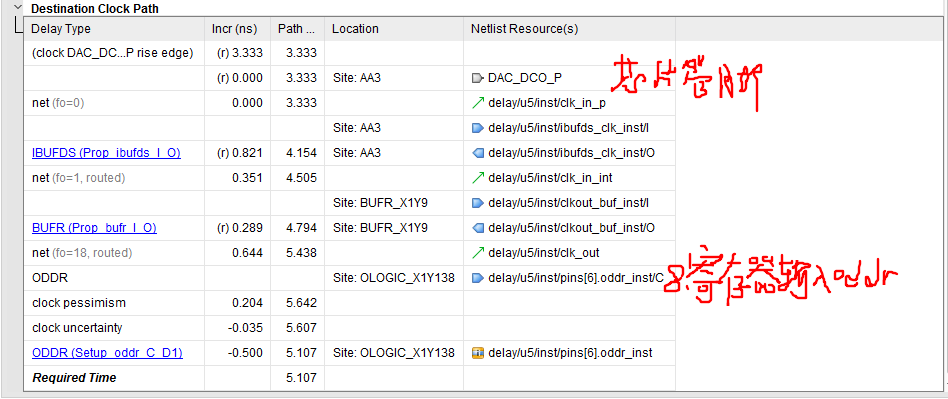

8.时钟到达第二级寄存器输入端时的时间。

我们看看以上的时序报告所描述的数据传输模型如下:

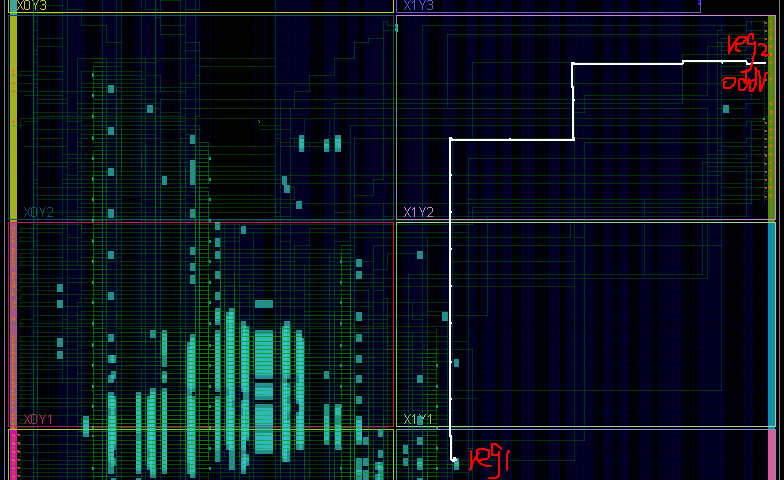

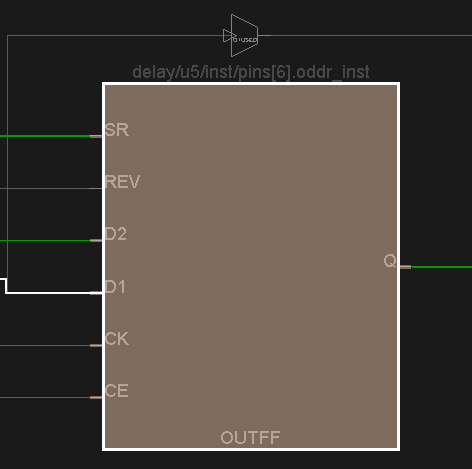

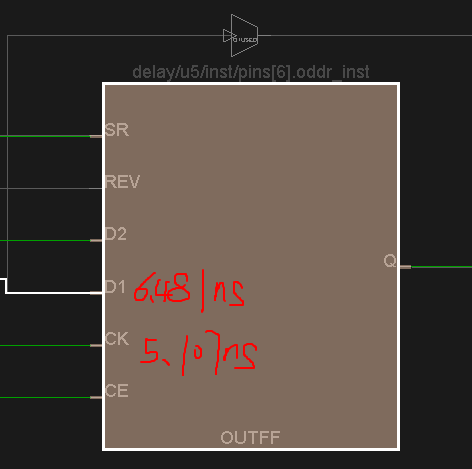

上图中蓝色标注的点与时序报告中标注的点一一对应,7.8两处的时间点分别对应数据与时钟采样沿到达ODDR寄存器的时间。我们看下数据到达7处ODDR寄存器的时间为6.481ns,时钟边沿到达8处ODDR寄存器的时间为5.107ns。我们如上把小亮比作时钟,把公交车比作数据,这也就是说小亮从家出发后5.107ns到达了站牌,而从小亮出发算起,公交车需要6.481ns后才能到达。完犊子,小亮到了站牌,公交车还没到,小亮坐不上公交所以就迟到了。5.107-6.481=-1.374,-1.374正好是1处的建立时间裕量,也就是小亮与公交车到达站牌的时间差。

以上我们看了下时序报告,并且通过数据传输模型简单的分析了以下时序报告,接下来我们看看芯片里面的对应内容,到底是怎么回事:

这个是时序报告中4处的芯片引脚,也就是时钟的输入脚DAC_DCO_P。

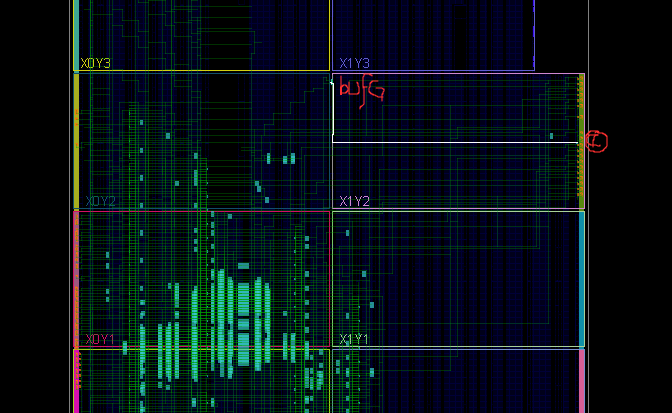

以上表示时钟信号从芯片管脚输入后传到了芯片中心得bufg缓冲器。

以上表示时钟通过bufg传到第一级寄存器时钟输入端。

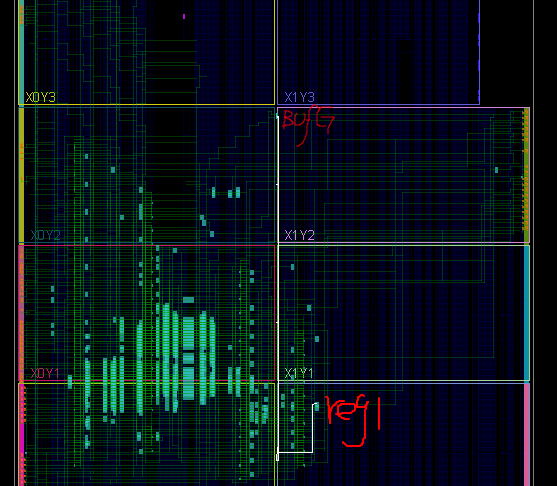

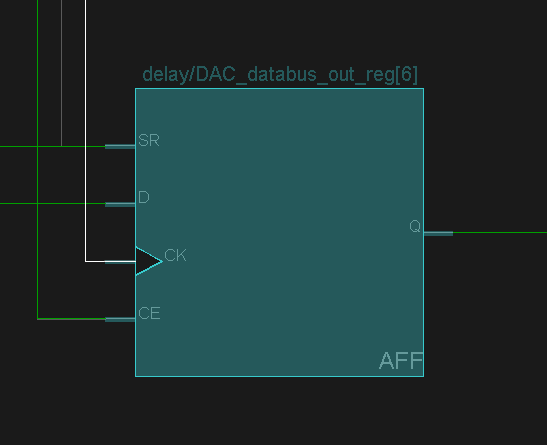

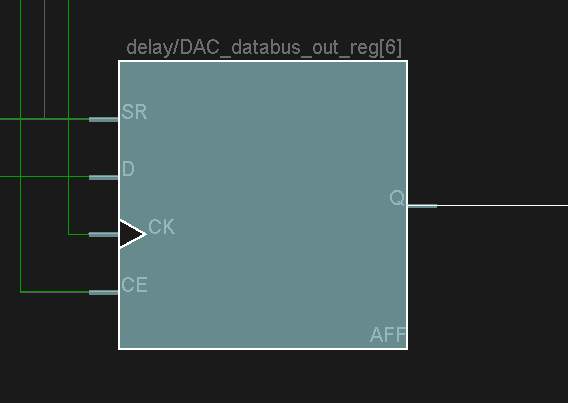

以上表示数据由第一级寄存器传到第二级寄存器oddr,到达这里的时间应该是6.481ns,也就是数据到达时间。

下来就是时钟传输走线路径,由于是类似的,所以就不再抠图了。最终到达第二级寄存器时钟与数据端口的时间如下图所示:

以上结果表示在时序图里如下:

这就是小亮从家里出发5.107ns后到达,公交车在6.481ns后才到,很明显小亮搭不上公交车,时序也要违规了!

以上的分析主要通过一个工程实例来解释建立时序违规的含义。

最后

以上就是迷人中心最近收集整理的关于时序约束(三)的全部内容,更多相关时序约束(三)内容请搜索靠谱客的其他文章。

发表评论 取消回复