时序约束和时序分析,在FPGA设计当中,是相当重要的基本功。但是市面上的教材、资料都相当的枯燥,不易理解,而且内容不多(最多就一章),不能写成一本书。于是,笔者尝试用通俗易懂的文字来解释这部分的内容。

1、什么是时序?

时序是指时间的先后顺序。在绝大多数的数字电路当中,都是依靠时钟来驱动各种电路工作的。时钟就像个领导一样,告诉各种电路,在什么时刻做什么事情。做的事情也是有先后顺序的,如果你不按常规出牌的话,就会出错,然后被领导骂了。

2、什么是约束?

校规就是一种约束,叫你不要逃课,你就不要逃。

3、什么是时序约束?

告诉各种电路,要按照我安排的先后顺序做事,不能乱。这里,电路就像是按照课表上课的学生。

4、什么是时序分析?

仅仅发号司令还不行,总会有些电路不按常规出牌,这时,就要分析一下原因了,就像是分析学生为什么逃课一样。

5、为什么需要做时序约束?

HDL只是描述我们需要什么样的电路,但是电路总得要布局布线的。如果只有HDL而不约束的话,就像是手里拿着元件,但是没有人画PCB一样。幸好综合器,会给我们约束,其实就像是自动布线一样。画过PCB的人,都知道自动布线弄出来的PCB有多烂了吧,所以才需要我们做时序约束。

6、什么是竞争、冒险?

学过数电的人,都很熟悉这个概念,还不清楚的,可以翻翻书,这里就不详细说明了。竞争、冒险的意思就是走线延时可能引起逻辑出错,当然,你做的是低速电路(交通灯之类的),会觉察不到这种问题。但是弄到100M以上的高速数字电路,一点点问题,都有可能导致整个系统不能正常工作。那么在FPGA上面考虑的时序问题,本质上,就是竞争、冒险。

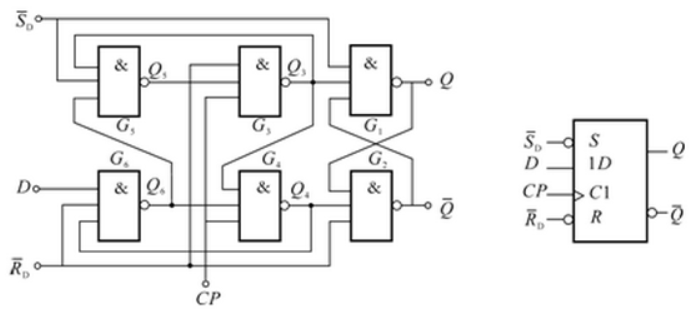

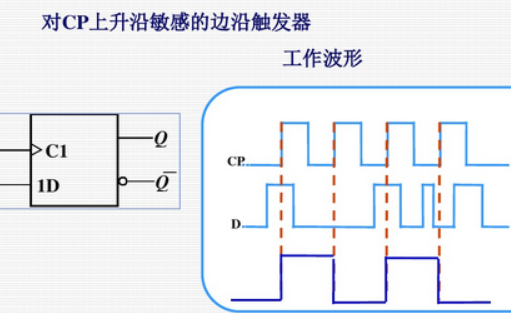

7、Review边沿触发器。

由于笔者比较懒,具体的,可以看一下D触发器的百度百科。特别要注意是,实际方波的边沿不是直的,而是有过渡过程的。此外,数据打入D触发器内部并不是立马生效,而是需要时间的(走线延时,MOS管的反应时间等)。

为了让数据准确无误地进出触发器,于是提出了三个重要概念:建立时间、保持时间、输出延时。

8、建立时间tsu。

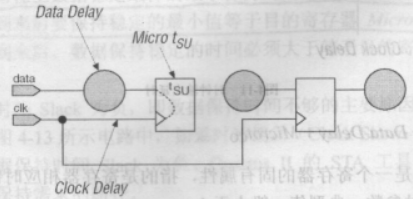

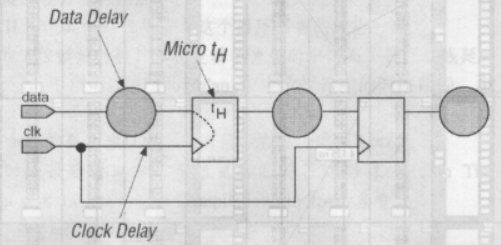

如上图所示,建立时间

其中Micro_tsu是触发器内部固有的建立时间,是常数,一般小于1ns,在大多数情况下可以忽略不计。

而Data Delay和Clock Delay分别指数据延时和时钟延时,这里用延时一词并不能准确地描述这个概念,应该用停留、暂留。(后面均用暂留时间)

所以,数据进入触发器之前,建立时间=输入数据暂留时间-时钟暂留时间,一般来说,数据会比时钟提前到达,而时钟会采集到数据的中部,所以建立时间大于0才是合理的。

9、保持时间th。

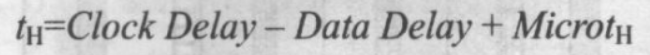

如上图所示,保持时间

其中Micro_th是触发器内部固有的保持时间,是常数,一般小于1ns,在大多数情况下可以忽略不计。

所以,数据进入触发器之后,保持时间=时钟暂留时间-输入数据暂留时间,因为时钟不稳定的话,触发器输出也不稳定,所以时钟要比数据更晚离开,一般,保持时间大于0才是合理的。

上图让你更容易理解建立时间和保持时间。

9、输出延时tco。

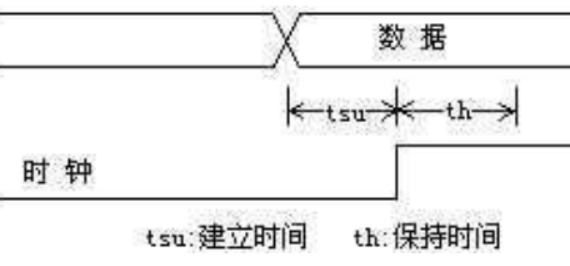

如上图所示,输出延时

其中Micro_tco是触发器内部固有的输出延时,是常数,一般小于1ns,在大多数情况下可以忽略不计。

所以,输出延时=时钟暂留时间+输出数据暂留时间。触发器输出的数据是给后级的触发器使用的,所以输出总得要维持一段时间,这个时间就是输出延时了。如果要保持输出的数据稳定的话,就要让时钟和输出数据同时稳定,因为时钟不稳定的话,触发器输出也不稳定。一般,输出延时大于0才是合理的。

10、引脚到引脚的延迟tpd。

画过PCB的人,都知道电路板,走线也会带来延时,所以这个tpd也很好理解,就是引脚到引脚的走线延时。

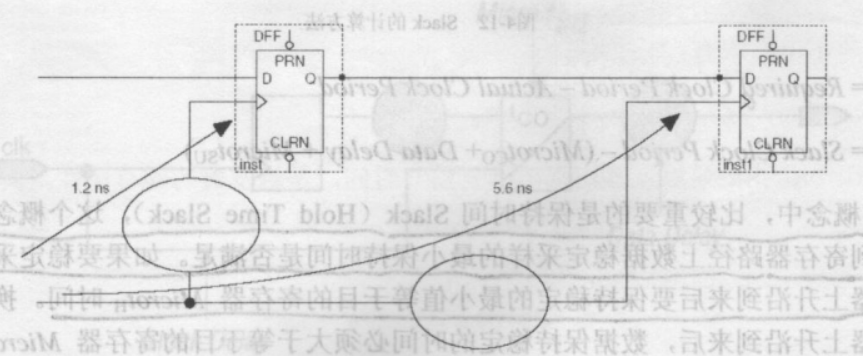

11、时钟偏斜slew。

偏斜又有不对称的意思。如上图,同一个时钟到达两个DFF所需要的延时不同,分别是1.2ns和5.6ns。

这说明了走线的长度不对称(这里特指长度,而不是指几何形状),时钟偏斜t_slew = tcd1 - tcd2 = 1.2--5.6=-4.4ns。

由于全局时钟的slew很小,一般是忽略不计的。

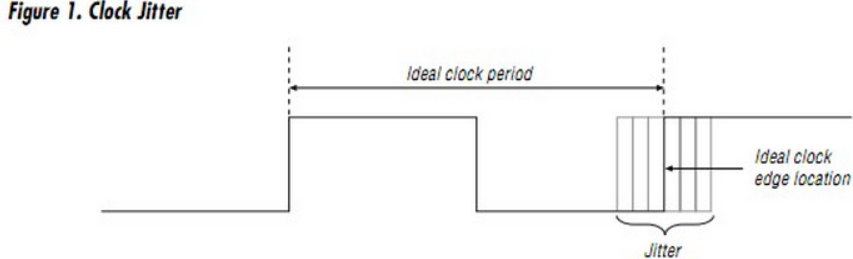

12、时钟抖动jitter。

把时钟送到示波器那里观察发现,每个时钟周期总会有点差异,这种差异是具有随机性的,被称为抖动。

幸好这个抖动,一般影响不大,也是可以忽略不计的。

13、时序余量slack。

时序余量是用来判断设计出来的电路的时序是否满足要求。

时序余量=需要的时钟周期-实际的时钟周期。

比如,我设计了一个乘法器,需要它能跑200M(周期5ns),但是经过综合器自动布线之后,最高只能跑180M(周期5.6ns)。

所以时序余量=5ns-5.6ns=-0.6ns,不能满足需求。一般,时序余量为正,才是合理的。

14、时序违规Timing violation。

时序余量为负,时序不满足要求,就是时序违规了。

最后

以上就是机灵含羞草最近收集整理的关于时序约束的基础概念的全部内容,更多相关时序约束内容请搜索靠谱客的其他文章。

发表评论 取消回复