时序约束方法——输入时序约束

- 一、系统同步输入

- 示例

- 二、源同步输入

- 示例

- 三、UCF源同步DDR边缘对齐示例

- 四、UCF源同步DDR中心对齐示例

- 五、UCF系统同步SDR示例

- 总结

在本节中,我们学习了输入时序约束的方法。其中,偏移输入(OFFSET IN)约束用于指定输入时序要求。那么,我们要对输入进行怎样的约束是由输入时序要求所决定的,而输入时序要求取决于接口的类型(源同步或者系统同步)和数据速率(SDR和DDR)。这些类别包括:

- 系统同步输入

- 源同步输入

- 理想系统同步SDR接口时序图

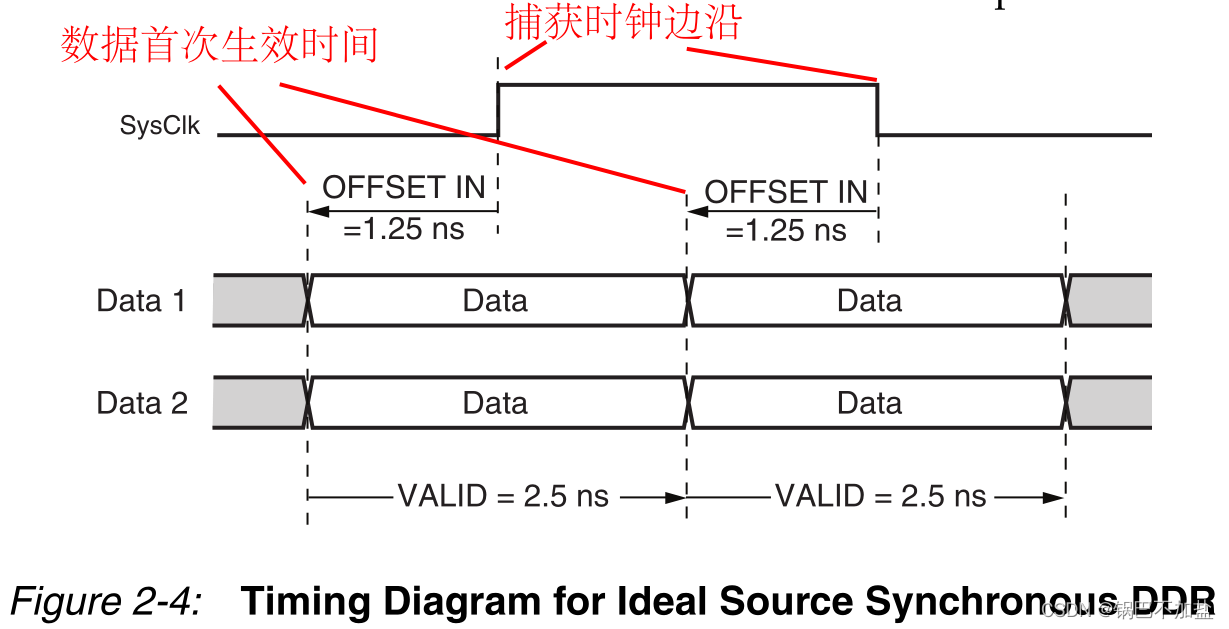

- 理想源同步DDR接口时序图

在这里,我们先介绍一下偏移输入约束的基本语法,如下。

NET "时钟0" TNM_NET = "时钟1";

TIMESPEC "时钟说明名称" = PERIOD "时钟1" 时间0 HIGH 占空比;

OFFSET = IN 时间1 VALID 时间2 BEFORE "时钟2" RASING;

其中,第一行表示在时钟网线时钟0 上附加一个 TNM_NET 约束,把时钟0 驱动的所有同步元件定义为一个名为 时钟1的分组,然后使用 TIMESPEC约束定义时钟周期。

第二行中,关键字TIMESPEC为时钟说明,即Time Specifiations的缩写,时钟说明名称是用来表示时钟说明TS的唯一名称,时间0表示时钟周期,HIGN或者LOW表示时钟周期里的初始电平是高电平还是低电平,占空比表示一个时钟周期内高电平占比,这里要写成百分比形式,比如50%,缺省占空比的情况下默认为50%。

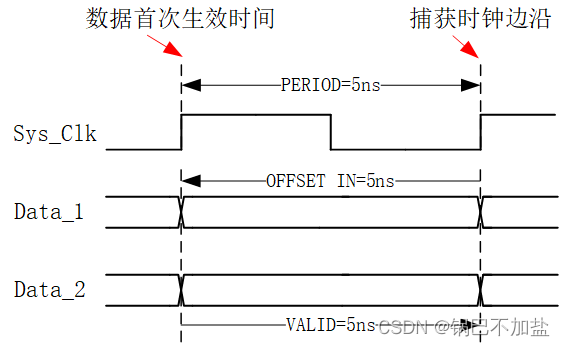

在第三行中,IN或者OUT表示对输入进行约束还是对输出进行约束,时间1表示捕获时钟边缘到数据首次变为有效的时间差值,时间2表示数据保持有效的持续时间,BEFORE或者是AFTER分别表示捕获时钟边缘到数据首次变为有效的时间差值是在时钟沿之前还是之后,时钟2表示数据捕获的工作在时钟1的边沿,RASING表示工作在上升沿处,如果没有指定上升沿(RASING)或者是下降沿(FALLING)时,默认为上升沿(RASING)。其对应的示意图如下。

注意:这里面的三个时间:时间0、时间1、时间2是要带单位的,例如:0.25 ms、5 ns、250 ps等。

一、系统同步输入

在系统同步的接口中,接口所使用的时钟是系统时钟,系统时钟既用于输出数据,又用于捕获数据。由于电路走线产生的延迟和时钟偏移,使得接口的工作频率被限制。

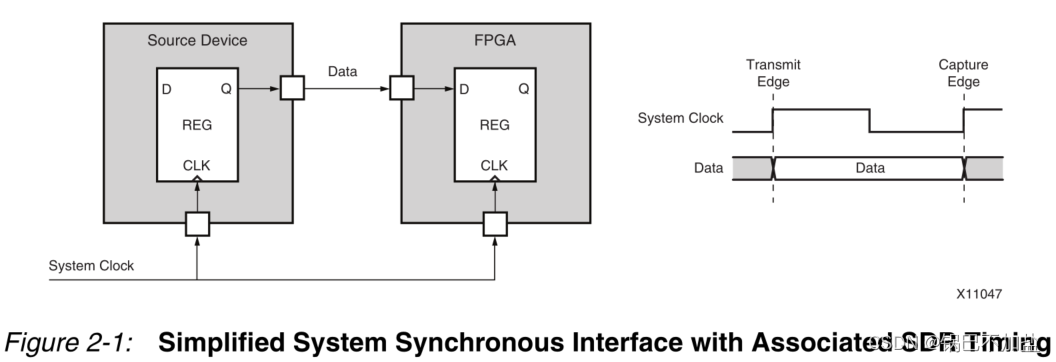

通常,使用系统同步的场景为SDR(同步动态存储器),即只在时钟的上升沿进行数据传输或是数据捕获。如下图所示,是一个同步SDR应用示例,在第一个系统时钟上升沿处,由源设备发送(传输)数据,在第二个系统时钟的上升沿处由FPGA对数据进行捕获。

那么,在这里,我们需要对该输入进行时序约束,指定输入的时序,主要包括以下两个部分:

- 定义与接口相关的输入时钟的时钟周期约束

- 定义接口的全局偏移输入约束(OFFSET IN)

示例

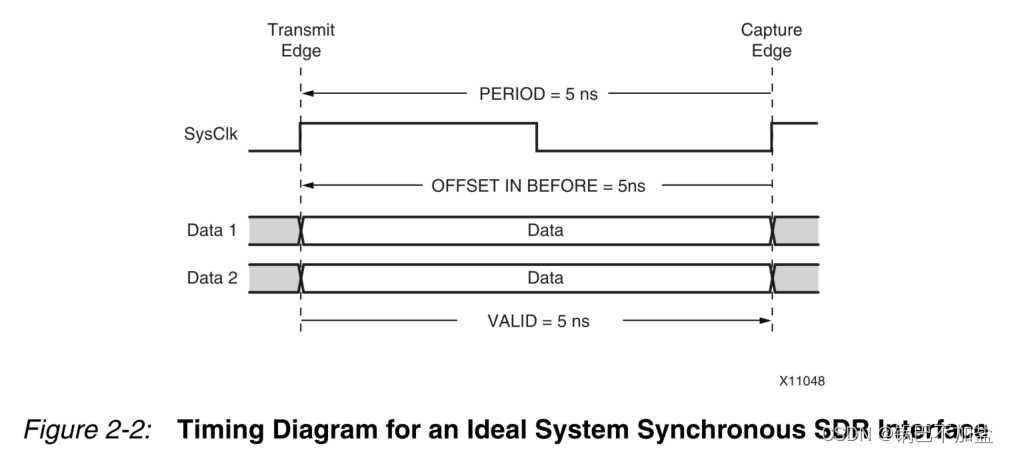

以理想的系统同步SDR接口为例,其接口输入时序图如下,要求接口工作在时钟周期为5ns(时钟频率为200 MHz)的系统下,且要求数据的保持时间为一个周期5ns,即在第一个系统时钟的上升沿处传输数据,在第二系统时钟的上升沿处捕获数据。

那么,我们就可以得到从捕获时钟边缘到数据首次生效的时间为5ns,同时,数据保持的持续时间也为5ns。这里不指定工作在上升沿还是下降沿时,默认为上升沿。于是,我们就可以对该接口的输入进行约束,如下:

NET "SysClk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%; //时钟周期为5ns,占空比为50%

OFFSET = IN 5 ns VALID 5 ns BEFORE "SysClk"; //在时钟SysClk上升沿的前5 ns为数据首次生效时间,且数

//据保有效的保持时间为5 ns

二、源同步输入

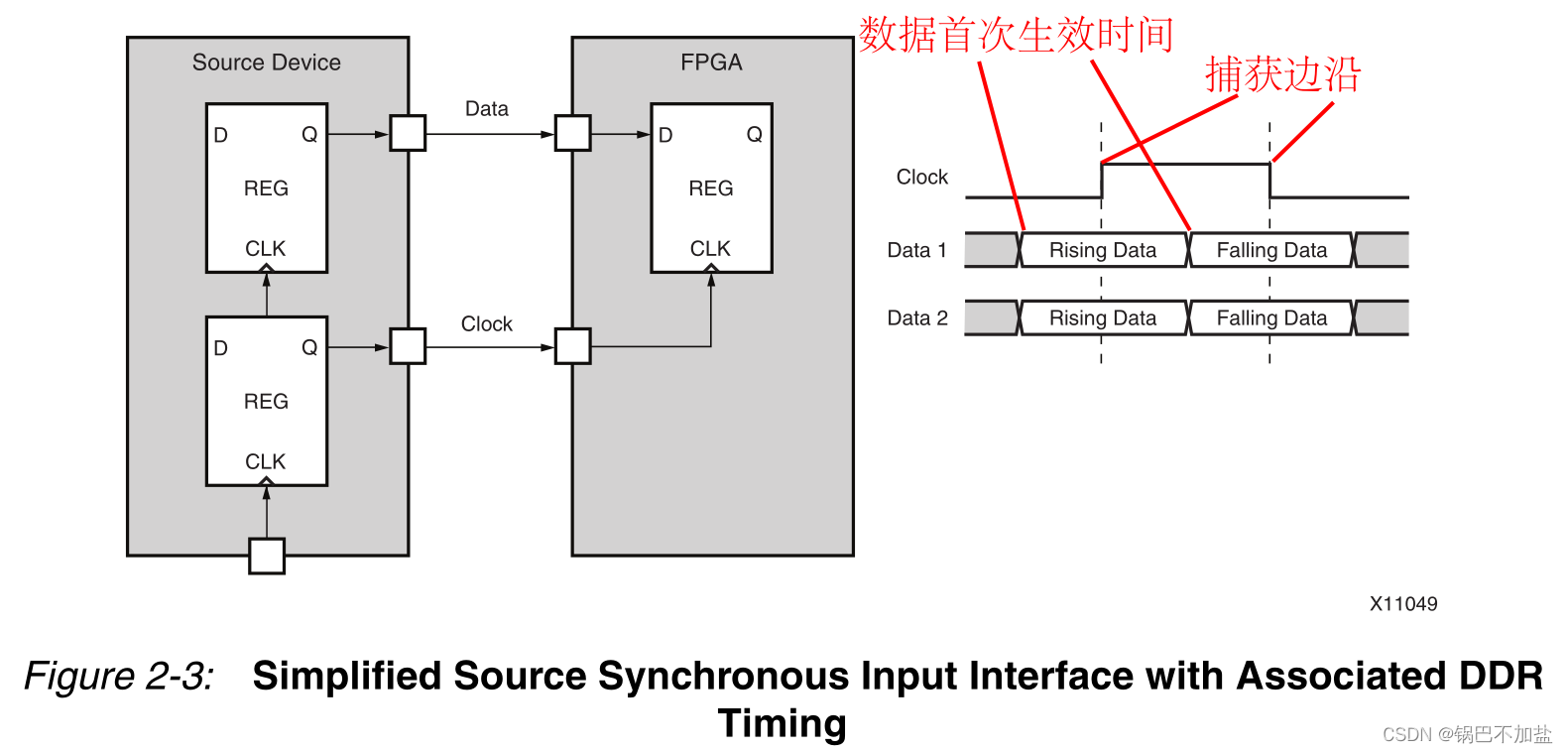

在源同步输入接口中,源设备工作时钟被重新生成并与来自源设备的数据一起进行传输,并用于FPGA器件中作为数据捕获的工作时钟(也就是说源设备发送数据的工作时钟与FPGA捕获数据的工作时钟并非同一个时钟)。于是,电路走线产生的延迟和时钟偏移不再限制接口的工作频率。那么,在双数据速率(DDR,Double Data Rata)中,我们常用源同步输入接口。DDR的应用示意图如下,其中,有两个注意的点:

- 源设备发送数据工作在原时钟的上升沿或者下降沿

- 而FPGA设备捕获数据则工作在重新生成的时钟的上升沿或者下降沿(下图中Clock即根据源设备的工作时钟所重新生成的时钟)

示例

以理想的源同步接口为例,其时序图如下,从图中可以得知,要求时钟周期为5ns,且占空比为50%,总线的两个位的数据在1/2个周期(2.5ns)内保持有效。

那么,对应的偏移输入约束为:

NET "SysClk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%; //时钟周期为5ns,占空比为50%

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" RASING; //在信号SysClk的上升沿的前1.25ns为数据首次有效时间,且

//数据有效的保持时间为2.5ns

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" FALLING; //在信号SysClk的下降沿的前1.25ns为数据首次有效时间,且

//数据有效的保持时间为2.5ns

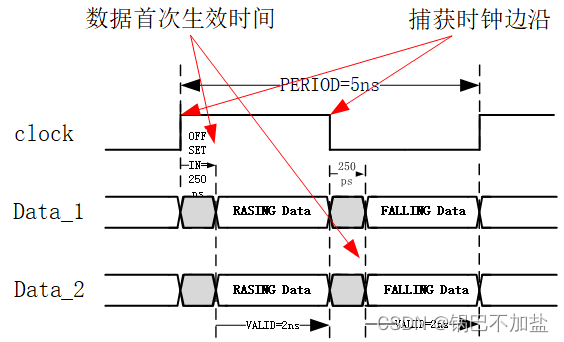

三、UCF源同步DDR边缘对齐示例

对于源同步DDR接口,与二中一致的是,其源设备传输数据工作在原时钟下,而FPGA接收设备捕获数据工作在重新生成的时钟下,并非同一个时钟,因此,需要为捕获数据的上升沿和下降沿进行约束,定义单独的偏移量限制。对于边沿对齐,即从捕获时钟边沿到数据首次生效时间,是关于上升沿或者下降沿对齐的。

以时钟周期为5ns,占空比为50%,数据在上升沿和下降沿的前2ns有效,如下图所示。

那么其对应的偏移输入约束为:

NET "clock" TNM_NET = "CLK";

TIMESPEC "TS_CLK" = PERIOD "CLK" 5 ns HIGH 50%; //时钟周期为5ns,占空比为50%

OFFSET = IN -250 ps VALID 2 ns BEFORE "clock" RASING; //在信号clock的上升沿的后250ps为数据首次有效时间

//且数据有效的保持时间为2ns

OFFSET = IN -250 ps VALID 2 ns BEFORE "clock" FALLING; //在信号clock的下降沿的后250ps为数据首次有效时间

//且数据有效的保持时间为2ns

这里与前面不同的是,-250 ps是负值,也就是说捕获时钟边沿到数据首次生效的时间为-250ps,即”捕获边沿时间值 - 数据首次有效时间= -250ps“,这在上图中不难看出。

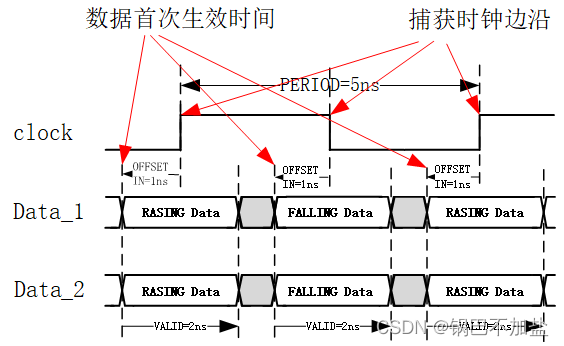

四、UCF源同步DDR中心对齐示例

源同步DDR中心对齐,与三中的源同步DDR边沿对齐大致上是一致的,区别在于这里的数据是中心对齐的,即上升沿数据RASING Data和下降沿数据FALLING Data关于上升沿和下降沿中心对齐。这里要求上升沿数据和下降沿数据在2ns内有效,且要分别关于上升沿和下降沿对齐,这也导致了在数据有效区间的前面和后面都有500ps的余量,如下图所示。

那么其对应的偏移输入约束为:

NET "clock" TNM_NET = "CLK";

TIMESPEC "TS_CLK" = PERIOD "CLK" 5 ns HIGH 50%; //时钟周期为5ns,占空比为50%

OFFSET = IN 1 ns VALID 2 ns BEFORE "clock" RASING; //在信号clock的上升沿的前1ns为数据首次有效

//时间,且数据有效的保持时间为2ns

OFFSET = IN 1 ns VALID 2 ns BEFORE "clock" FALLING; //在信号clock的下降沿的前1ns为数据首次有效

//时间,且数据有效的保持时间为2ns

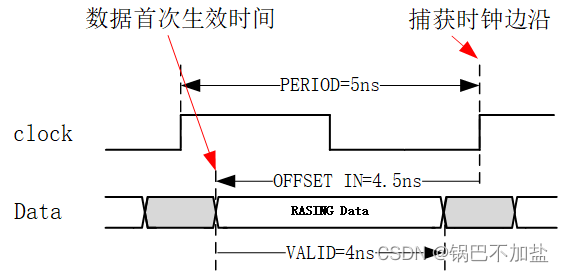

五、UCF系统同步SDR示例

再比如系统同步单数据速率(SDR),其包括一个接口,在该接口中,时钟在一个时钟边沿从发送设备发送,并在下一个时钟边由FPGA捕获。在单数据速率接口中,每个时钟周期发送一次数据,并且在约束中只需要一个偏移。

在本示例中,数据在发送时钟边沿之后500ps或在用于捕获数据的时钟边沿之前4.5ns变为有效。这导致值为正的4.5ns的前向偏移,因为它在时钟沿之前开始。一旦数据开始,它将在4 ns内保持有效。

那么其对应的偏移输入约束为:

NET "clock" TNM_NET = "CLK";

TIMESPEC "TS_CLK" = PERIOD "CLK" 5 ns HIGH 50%; //时钟周期为5ns,占空比为50%

OFFSET = IN 4.5 ns VALID 4 ns BEFORE "clock"; //在信号clock的上升沿的前4.5ns为数据首次有效

//且数据有效的保持时间为4ns

在这里,有一种等价形式

OFFSET = IN 4.5 ns VALID 4 ns BEFORE "clock"; //也可以写成

OFFSET = IN 0.5 ns VALID 4 ns AFTER "clock";

总结

那么,在本节中我们学习了对输入信号进行时序约束方法(这里包含了一部分约束项的约束方法),主要为输入偏移约束的语法,至于在什么情况下,使用相关的约束,也是我需要学习的内容。

注:以上仅为个人学习笔记,如有不妥之处,欢迎评论区探讨交流,如有帮助,请点个赞吧!

最后

以上就是甜甜豆芽最近收集整理的关于时序约束方法——输入时序约束一、系统同步输入二、源同步输入三、UCF源同步DDR边缘对齐示例四、UCF源同步DDR中心对齐示例五、UCF系统同步SDR示例总结的全部内容,更多相关时序约束方法——输入时序约束一、系统同步输入二、源同步输入三、UCF源同步DDR边缘对齐示例四、UCF源同步DDR中心对齐示例五、UCF系统同步SDR示例总结内容请搜索靠谱客的其他文章。

发表评论 取消回复