1.什么是虚拟时钟?

虚拟时钟(virtual clock)是存在但没有clock source(pin/port)定义的时钟,仅作为输入输出端口延时约束的参考时钟。定义方式如下例:

create_clock -name virtual_clock -period 10 -waveform {0 5} ;#虚拟时钟不需要[get_pins /get_ports],不加waveform默认50% duty cycle。所以加不加-waveform {0 5}效果是一样的。

与虚拟时钟相关的端口约束为set_input_delay和set_output_delay。

2.IO端口约束

静态时序分析有四种时序路径,分别是:in2reg,reg2reg,reg2out和in2out,其中三种都与input或output port相关,而工具并不知道input port和output port外部延时,所以需要对其加以约束。

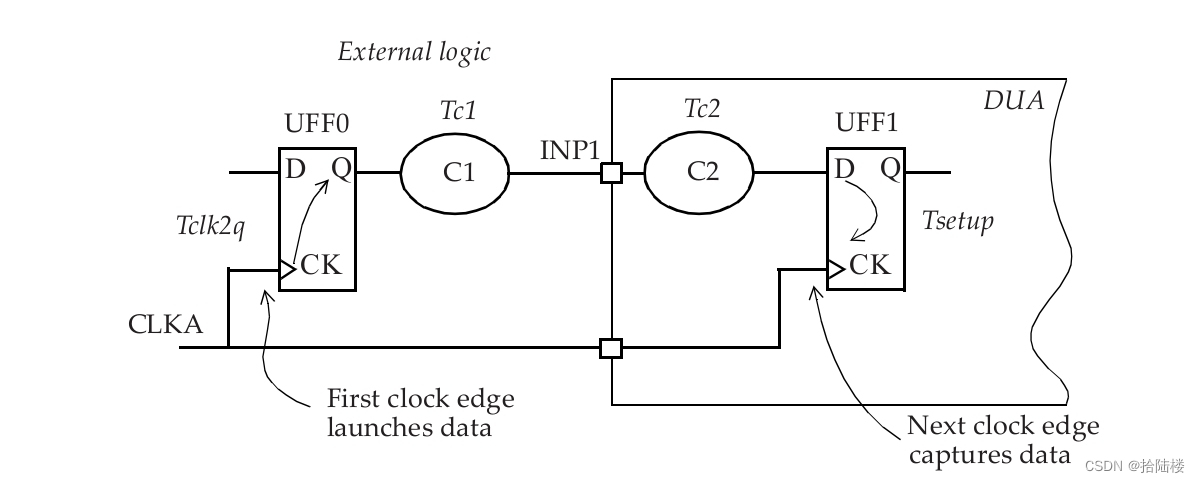

时序分析时,我们把四种时序路径都当做reg2reg来分析,以in2reg为例,如下图,我们在block外设置一个虚拟的寄存器UFF0。

现在INP1 to UFF1的path就变成了UFF0 to UFF1了,只需要设置好外部延迟即可,设置方式如下:

set_input_delay -max (Tclk2q+Tc1) [get_ports INP1] -clock [get_clocks $CLK]

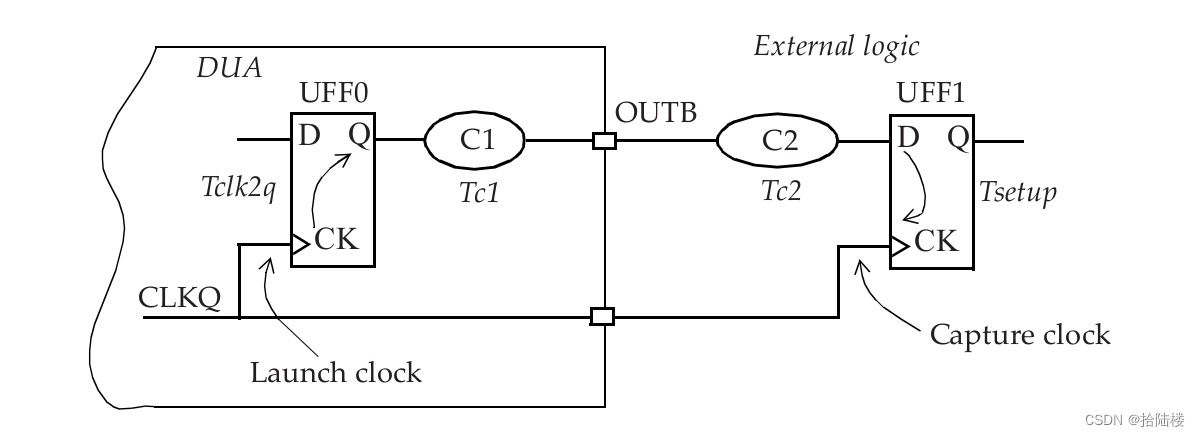

同理,如果是reg2out,就可以在output port后假定一个虚拟寄存器,如下图。

set_output_delay -max (Tc2 + Tsetup) [get_ports OUTB] -clock [get_clocks $CLK]

3.virtual clock VS real clock

问题来了,如上图例,这个$CLK用虚拟时钟好还是用真实时钟好呢?这里先说结论,用真实时钟更好。

我们在CTS之前,clock latency都是0,真实时钟和虚拟时钟都一样,区别就在于CTS之后,真实的reg有network latency了(clock latency分为source latency+network)。而虚拟寄存器的latency还是0。

静态时序分析: clock latency

现在的PR工具都会在CTS之后自动update io latency(ICC2叫compute_clock_latency),所以使用real clock的话会在timing报告里属于input/output port的clock network delay 部分显示:

clock network delay (propagated) xxx

这个值是工具计算的值(应该是取中位数)。

如果使用虚拟时钟的话,这里显示的就是:

clock network delay (ideal) 0

所以,要想使用虚拟时钟,又不至于过分乐观或悲观的话,就需要添加set_clock_latency -source xx [get_clocks CLK_VIRTUAL],这样CTS之后仍会保留io latency的值,只不过这个值就需要人工计算,或者使用经验值了,并没有使用real clock那么好用。

最后

以上就是兴奋飞机最近收集整理的关于静态时序分析—虚拟时钟(virtual clock)与I/O延时约束的全部内容,更多相关静态时序分析—虚拟时钟(virtual内容请搜索靠谱客的其他文章。

发表评论 取消回复