DC静态时序分析之时钟篇

博主微信:flm13724054952,不懂的有疑惑的也可以加微信咨询,欢迎大家前来投稿,谢谢!

引言介绍

在芯片设计或者FPGA设计里面,根据有无时钟,将电路设计分为时序逻辑电路设计跟组合逻辑电路设计两部分。对设计的电路进行时序分析来说,时钟是不可或缺的。本文主要介绍关于在静态时序分析中时钟的基础知识跟常用SDC指令。

基础知识

在介绍时钟的详细指令前,先介绍在静态时序分析中关于时钟的一些基础知识跟概念,例如clock tree(时钟树),clock jitter(时钟抖动),clock latency(时钟延迟),clock skew(时钟偏斜),clock uncertainty(时钟不确定),clock transition(时钟转化),clock gating(时钟门控),clock fanout(时钟扇出)。

clock tree(时钟树)

clock tree时钟树是指从时钟源source出发,经过布局布线通过各种buffer到达不同时序模块(时序器件)而形成类似一种树的网络结构就叫做时钟树。

作用:通常可以通过对时钟的布局布线来达到减少时钟对时序模块的skew影响,使时序更加收敛;也可以通过与clock gating结合,控制模块的打开关闭,起到节省电路功耗的作用。

clock latency(时钟延迟)

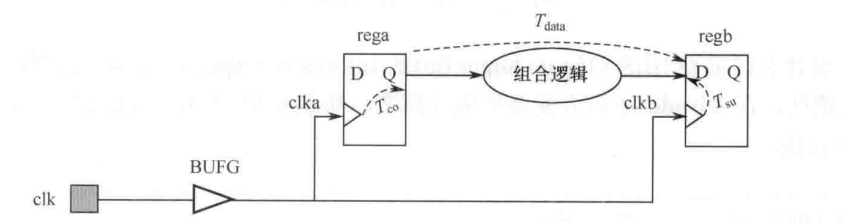

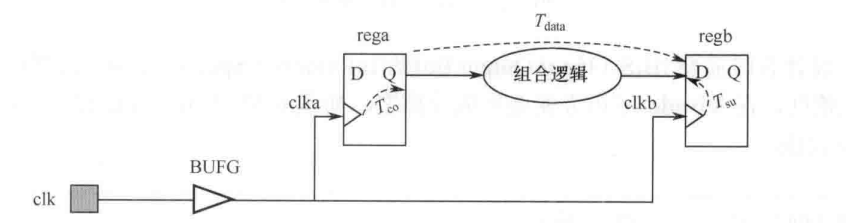

clock latency时钟延迟指的是在时钟源出发到某个时钟器件触发端的延迟,时钟源可以为芯片外部晶振或者芯片内部的PLL锁相环。例如下图所示这里的clock latency为单独指clka或者clkb。

clock jitter(时钟抖动)

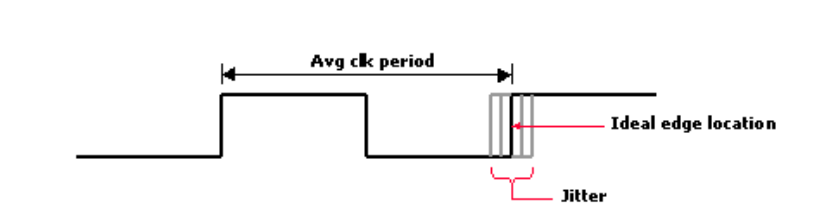

clock jitter时钟抖动是指时钟在周期上存在频率的不确定性,叫做时钟抖动; 通常造成时钟抖动是因为时钟源晶振本身的稳定性,又或者工作环境的温度,电压对其造成了影响。

影响:通常clock jitter跟clock skew是影响时钟信号稳定性的主要因素,对电路的时序分析也存在影响。

clock skew(时钟偏斜)

clock skew时钟偏斜指的是从时钟源出发到不同时序器件之间的延迟。例如下图所示,clock latency单指的是clka或者clkb,而clock skew指的是时钟经过不同buffer跟走线到达不同时序器件rega跟clkb的延迟,这里的clock skew指的是clk到达寄存器触发端的clka与clkb的沿的相位差。

影响:skew 通常是时钟相位上的不确定,造成 skew 的原因很多。由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异,因此就带来了skew。

clock uncertainty(时钟不确定)

clock uncertainty时钟不确定性通常指的是时钟在时序器件引脚的不确定性,可以直接理解为clock skew跟clock jitter的和。

影响:通常来说clock uncertainty越小,时钟的建立时间余量就越大。约容易满足时序路径上的建立时间,一般来说uncertainty一般为时钟周期的10%到30%。

一般可以设置set_clock_uncertainty 10%T(30%T)…

clock transition(时钟转化)

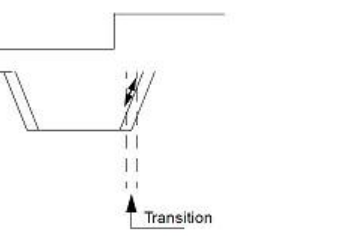

clock transition通常指的是clock 信号的 slew 时间。分为上升沿时间和下降沿时间。

clock gating(时钟门)

clock gating时钟门指的是,从时钟源到模块时钟的时钟树枝里“与”各模块的控制使能信号,通过使能信号来控制各模块的时钟是否打开。从而达到将一些不需要一直工作的模块停掉,达到节省电路功耗的目的。

clock fanout(时钟扇出)

clcok fanout时钟扇出指的是时钟源通过各级buff到达各时序模块的个数。

常用指令set_max_fanout 20 [get_clock clk] ##这里20指的是你电路设计扇出到了多少时序器件。

时钟约束

生成主时钟

create_clock -period 40 -waveform [0 20] -name clk [get_ports clk]

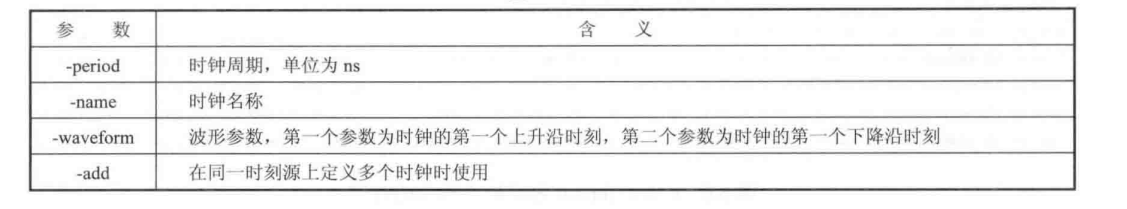

上述指令是生成周期为40ns频率为25MHZ的时钟clk;生成时钟指令的各参数介绍如下图所示:

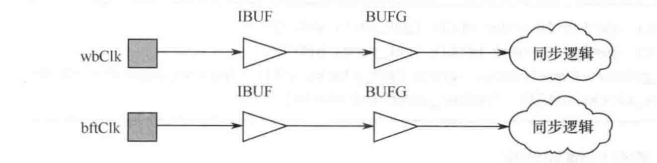

如果生成多个主时钟时的相位是不一致异步的,那么就要用set_clock_groups来对不同主时钟之间的相位约束;

例如下图所示:当时钟wbClk跟bftClk两个主时钟的相位是异步的;应当这样子来进行约束:

create_clock -period 50 wbClk [get_ports wbClk]

create_clock -period 20 bftClk [get_ports bftClk]

set_clock_groups -asynchronous -group wbClk -group bftClk

当如果两个主时钟wbClk跟bftClk的相位是一致的,即可以不用set_clock_groups来进行约束。

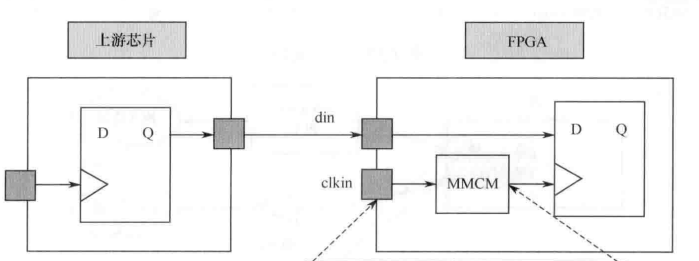

生成同源时钟

正如上面介绍所说create_clock是生成主时钟的(顶层的),工程师也可以通过一种方式来生成自定义时钟给模块电路,好处就是可以使主时钟跟自定义时钟同源同相而避免了上面所说的存在时钟的skew的影响。如下所示apcnt_top为顶层,apcnt_clk为子模块。clkin到顶层跟clkin到子模块,存在skew的延迟。而通过create_generate_clock可以使顶层跟子模块同源同相。减少skew的影响。

module apcnt_top

…

apcnt_clk

u_apcnt_clk

();

…

endmdoule

module apcnt_clk(clkin ,clk_a);

…

always@(posedge clkin or negedge nrst)

begin

if(!nrst)

clk_a <= 0;

else

clk_a <= ~clk_a;

end

always@(posedge clk_a)

…

endmodule

具体约束指令如下所示:

create_clock -period 50 -name clk_in [get_ports clkin]

create_generate_clock -divide_by 1 -source clkin -name clk_in [get_pins u_apcnt_clkclkin]

又或者

create_clock -period 50 -name clk_in [get_ports clkin]

create_generate_clock -multiple_by 1 -source clkin -name clk_in [get_pins u_apcnt_clkclkin]

生成虚拟时钟

一般来说只有在创建输入输出约束的时候才会创建虚拟时钟。与主时钟不同的就是,虚拟时钟是自己内部电路设计产生的捕获时钟,所以没有对应的物理引脚。例如下面代码所示,clkin为有物理页脚的输入主时钟,而clk_a只是我们内部电路设计的捕获虚拟时钟,没有对应的port。

always@(posedge clkin or negedge nrst)

begin

if(!nrst)

clk_a <= 0;

else

clk_a <= ~clk_a;

end

always@(posedge clk_a)

…

也就是来说,对这类虚拟时钟在捕获数据时,应当考虑对他的约束,具体约束指令如下所示:

create_clock -period 10 -name clkin [get_ports clk_in]

create_clock -period 20 -name clk_a

set_input_delay 4 -clock clk_a [get_ports din]

最后

以上就是陶醉高跟鞋最近收集整理的关于DC静态时序分析之时钟篇DC静态时序分析之时钟篇的全部内容,更多相关DC静态时序分析之时钟篇DC静态时序分析之时钟篇内容请搜索靠谱客的其他文章。

发表评论 取消回复