FPGA课设——交通信号控制器的VHDL设计

- 1、设计任务及要求:

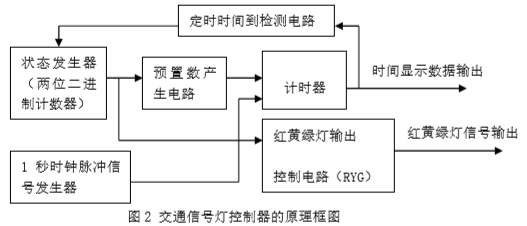

- 2、参考设计方案

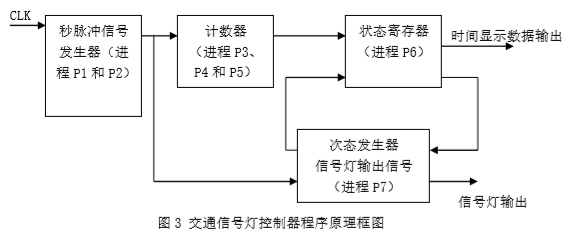

- 3、采用 VHDL 语言输入的方式实现交通信号灯控制器

- 4、设计方案

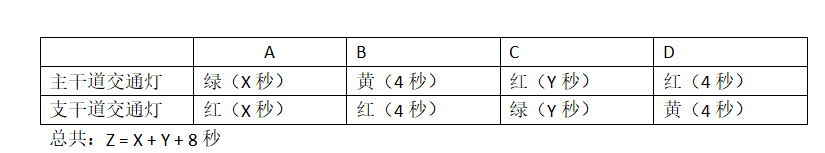

- 5、自定义交通灯主从控制时间

1、设计任务及要求:

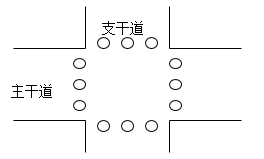

设计任务:模拟十字路口交通信号灯的工作过程,利用实验板上的两组红、黄、绿LED 作为交通信号灯,设计一个交通信号灯控制器。要求:

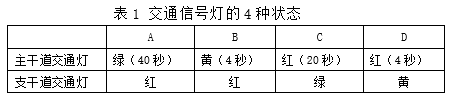

(1)交通灯从绿变红时,有4秒黄灯亮的间隔时间;

(2)交通灯红变绿是直接进行的,没有间隔时间;

(3)主干道上的绿灯时间为40秒,支干道的绿灯时间为20秒;

(4)在任意时间,显示每个状态到该状态结束所需的时间。

设计要求:

(1)采用VHDL语言编写程序,并在QUARTUSII工具平台中进行仿真,下载到EDA实验箱进行验证。

(2)编写设计报告,要求包括方案选择、程序清单、调试过程、测试结果及心得体会。

2、参考设计方案

3、采用 VHDL 语言输入的方式实现交通信号灯控制器

该程序由 7 个进程组成,进程 P1 和 P2 将 CLK 信号分频后产生 1 秒信号,进程 P3、P4、 P5构成两个带有预置数功能的十进制计数器,其中P4 产生允许十位计数器计数的控制信号。 进程P6实现状态转换和产生状态转换的控制信号,进程P7产生次态信号和信号灯输出信号, 以及每一个状态的时间值。

4、设计方案

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY TRAFFIC_LIGHT IS

PORT(CLK,RST: IN STD_LOGIC;

LED: OUT STD_LOGIC_VECTOR(5 DOWNTO 0); --定义6个LED灯

WideSEGH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --主干倒计时的十位

WideSEGL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --主干倒计时的个位

NSEGH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --支干倒计时的十位

NSEGL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); --支干倒计时的个位

END ENTITY TRAFFIC_LIGHT;

ARCHITECTURE bhv OF TRAFFIC_LIGHT IS

TYPE state IS(S0,S1,S2,S3); --枚举状态类型

SIGNAL current_s,next_s:state;

SIGNAL COUNT68:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

COUNT: PROCESS(RST,CLK) --辅助进程

BEGIN

IF RST= '1' THEN --异步清零

COUNT68<="00000000";

ELSIF CLK'EVENT AND CLK='1' THEN

IF COUNT68<"01000011" THEN --B01000011=67设定68进制计数器

COUNT68<=COUNT68+1;

ELSE

COUNT68<="00000000";

END IF;

END IF;

END PROCESS;

REG: PROCESS (RST,CLK) --主控时序进程,用于机械地控制状态转换

BEGIN

IF RST= '1' THEN

current_s <= s0;

ELSIF clk='1' AND clk'EVENT THEN

current_s <= next_s;

END IF;

END PROCESS;

COM:PROCESS(current_s, COUNT68) --主控组合进程,用于设定状态转换的下一个状态

VARIABLE WESEG,NSSEG:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

CASE current_s IS

WHEN s0 => LED<= "010100";--主干绿灯亮,支干红灯亮

WESEG:=39-COUNT68; --主干绿灯倒计时,用于数码管显示

NSSEG:=43-COUNT68; --支干红灯倒计时

IF COUNT68 ="00100111" THEN --B00100111=39 控制状态转变

next_s<=s1;

ELSE

next_s<=s0;

END IF;

WHEN s1 => LED <= "001100"; --主干黄灯,支干红灯

WESEG:=43-COUNT68;

NSSEG:=43-COUNT68;

IF COUNT68 = "00101011" THEN --B00101011=43

next_s<=s2;

ELSE

next_s<=s1;

END IF;

WHEN s2 => LED <= "100010"; --主干红灯,支干绿灯

WESEG:=67-COUNT68;

NSSEG:=63-COUNT68;

IF COUNT68 ="00111111" THEN --B00111111=64

next_s <= s3;

ELSE

next_s <= s2;

END IF;

WHEN s3 => LED <= "100001"; --主干红灯,支干黄灯

WESEG:=67-COUNT68;

NSSEG:=67-COUNT68;

IF COUNT68 ="01000011" THEN --B01000011=67

next_s<= s0;

ELSE

next_s <= s3;

END IF;

WHEN OTHERS=> LED <="100100"; --否则都不能通行

END case;

IF WESEG>39 THEN --译码器的功能:将当前的倒计时转换成十进制,低四位和高四位分别是数码管的个位与十位,

--38+18=56D=38H=00111000B

--使数码管按照当前的计数(十进制)按二进制计数进行倒计时

WESEG:=WESEG+24;

ELSIF WESEG>29 THEN

WESEG:=WESEG+18;

ELSIF WESEG>19 THEN

WESEG:=WESEG+12;

ELSIF WESEG>9 THEN

WESEG:=WESEG+6;

ELSE NULL;

END IF;

IF NSSEG>39 THEN

NSSEG:=NSSEG+24;

ELSIF NSSEG>29 THEN

NSSEG:=NSSEG+18;

ELSIF NSSEG>19 THEN

NSSEG:=NSSEG+12;

ELSIF NSSEG>9 THEN

NSSEG:=NSSEG+6;

ELSE NULL;

END IF;

WideSEGH<=WESEG(7 DOWNTO 4);

WideSEGL<=WESEG(3 DOWNTO 0);

NSEGH<=NSSEG(7 DOWNTO 4);

NSEGL<=NSSEG(3 DOWNTO 0);

END PROCESS;

END ARCHITECTURE bhv;

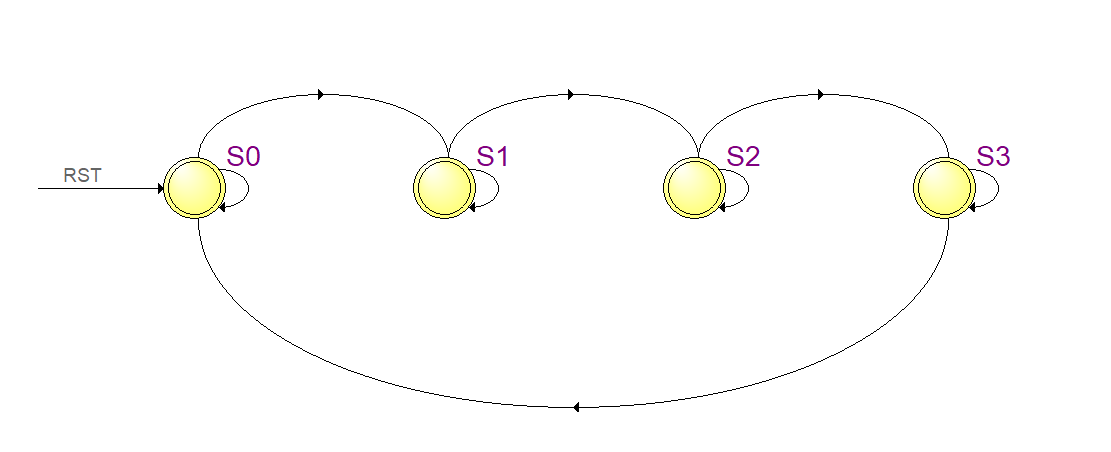

状态图:

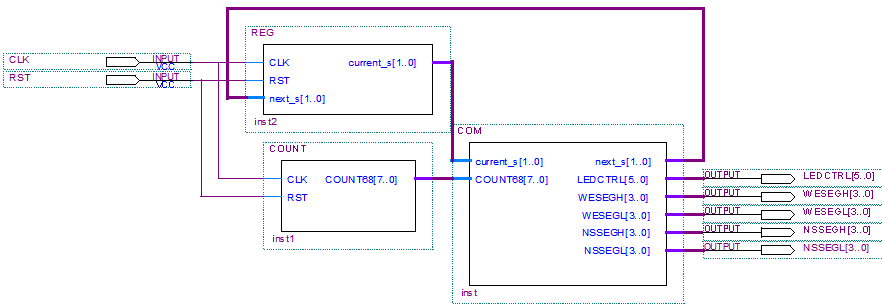

顶层文件图:

顶层文件图:

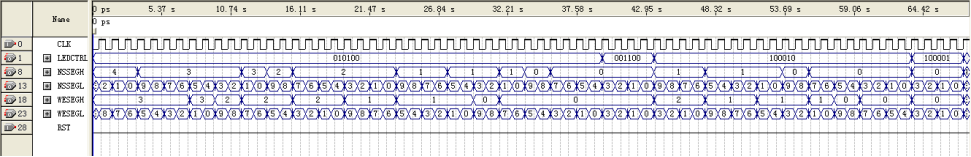

波形仿真图:

波形仿真图:

5、自定义交通灯主从控制时间

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY TRAFFIC_LAMP IS

PORT(CLK,RST: IN STD_LOGIC;

LEDCTRL: OUT STD_LOGIC_VECTOR(5 DOWNTO 0);

WESEGH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

WESEGL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

NSSEGH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

NSSEGL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END ENTITY TRAFFIC_LAMP;

ARCHITECTURE behav OF TRAFFIC_LAMP IS

TYPE FSM_ST IS(S0,S1,S2,S3);

SIGNAL current_s,next_s:FSM_ST;

SIGNAL COUNT68:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

COUNT: PROCESS(RST,CLK) --辅助进程

BEGIN

IF RST= '1' THEN COUNT68<="00000000";--检测异步复位信号

ELSIF CLK'EVENT AND CLK='1' THEN

IF COUNT68<"(z-1变成二进制后代入)" THEN -- 1

COUNT68<=COUNT68+1;

ELSE COUNT68<="00000000";

END IF;

END IF;

END PROCESS;

REG: PROCESS (RST,CLK) --主控时序进程

BEGIN

IF RST= '1' THEN current_s <= s0; --检测异步复位信号

ELSIF clk='1' AND clk'EVENT THEN

current_s <= next_s;

END IF;

END PROCESS;

COM:PROCESS(current_s, COUNT68) --主控组合进程

VARIABLE WESEG,NSSEG:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

CASE current_s IS

WHEN s0 => LEDCTRL<= "010100";

WESEG:=(x-1)-COUNT68;NSSEG:=(x+4-1)-COUNT68; --2,3

IF COUNT68 ="(x-1换算成二进制代入)" THEN next_s<=s1; --4

ELSE next_s<=s0;

END IF;

WHEN s1 => LEDCTRL<= "001100";

WESEG:=(x+4-1)-COUNT68;NSSEG:=(x+4-1)-COUNT68; --5,6

IF COUNT68 = "(x+4-1换算成二进制)" THEN next_s<=s2; --7

ELSE next_s<=s1;

END IF;

WHEN s2 => LEDCTRL<= "100010";

WESEG:=(z-1)-COUNT68;NSSEG:=(z-5)-COUNT68; --8,9

IF COUNT68 ="(z-5换算成二进制)" THEN next_s <= s3;

ELSE next_s <= s2;

END IF;

WHEN s3 => LEDCTRL <= "100001";

WESEG:=(z-1)-COUNT68;NSSEG:=(z-1)-COUNT68;

IF COUNT68 ="(z-1换算成二进制)" THEN next_s<= s0;

ELSE next_s <= s3;

END IF;

END case;

--如果x>40的话,要改下面的内容

--例:x=67

--

--IF WESEG>59 THEN WESEG:=WESEG+36; --后面依次加6

-- ELSIF WESEG>49 THEN WESEG:=WESEG+30;

-- ELSIF WESEG>39 THEN WESEG:=WESEG+24;

-- ELSIF WESEG>29 THEN WESEG:=WESEG+18;

-- ELSIF WESEG>19 THEN WESEG:=WESEG+12;

-- ELSIF WESEG>9 THEN WESEG:=WESEG+6;

-- ELSE NULL;

IF WESEG>39 THEN WESEG:=WESEG+24;

ELSIF WESEG>29 THEN WESEG:=WESEG+18;

ELSIF WESEG>19 THEN WESEG:=WESEG+12;

ELSIF WESEG>9 THEN WESEG:=WESEG+6;

ELSE NULL;

END IF;

--这个修改方法跟上面一样

IF NSSEG>39 THEN NSSEG:=NSSEG+24;

ELSIF NSSEG>29 THEN NSSEG:=NSSEG+18;

ELSIF NSSEG>19 THEN NSSEG:=NSSEG+12;

ELSIF NSSEG>9 THEN NSSEG:=NSSEG+6;

ELSE NULL;

END IF;

WESEGH<=WESEG(7 DOWNTO 4);WESEGL<=WESEG(3 DOWNTO 0);

NSSEGH<=NSSEG(7 DOWNTO 4);NSSEGL<=NSSEG(3 DOWNTO 0);

END PROCESS;

END ARCHITECTURE behav;

其他课设题目:

1、AC-DC数字稳压电源设计与仿真

2、步进式增益调节语音放大器

3、函数发生器课程设计(Multisim仿真+PCB实物)

4、嵌入式+人工智能+物联网开发常用的开发工具

5、数字交通灯设计(Multisim仿真+PCB实物)

6、数字钟—VHDL设计

课设工程代码和报告资料地址:关注公众号:Kevin的学习站,进入后台输入:FPGA交通灯,就OK啦!

创作不易,但你的点赞、关注、收藏就是对我最大的鼓励!

最后

以上就是迅速大地最近收集整理的关于交通灯—VHDL设计的全部内容,更多相关交通灯—VHDL设计内容请搜索靠谱客的其他文章。

发表评论 取消回复