使用set_sense可以人为的制造sink pin和ignore pin,set_sense两种常用方法,-stop_propagation和-clock_leaf。

如下示例,初始sdc的设置:

create_clock [get_ports clk] -name clk -period 2 -waveform {0 1}

create_generate_clock [get_pins FF1/Q] -name gen_clk -source [get_ports clk] -edge {1 2 3}

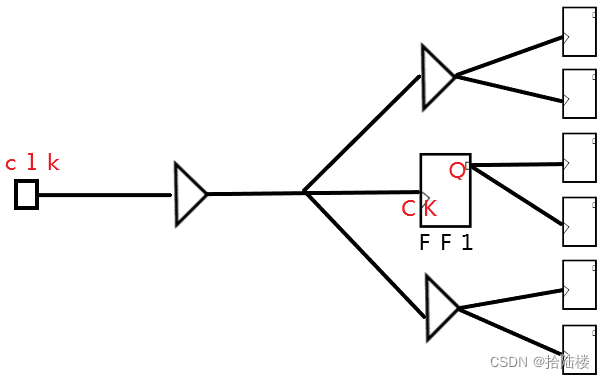

CTS后时钟树结构如图1,FF1/CK作为through pin是不做balance的。

图1.原始sdc在cts后clock tree结构

1、set_sense -stop_propagation

给指定clock设置clock endpoint。

1)如果inst是一个reg/icg,inst/pin是一个output pin。

set_sense -stop_propagation -type clock -clocks [get_clocks clk] [get_pins FF1/Q]

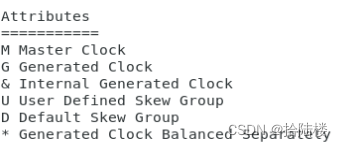

此时FF1/CK就会被当作sink pin,CTS阶段会balance,如果此时FF1后面有generate clock(ICC2的属性描述即不是master clock也不是generate clock,而是*,见图2),那么generate clock仍然会长tree,只不过不会与clk其他的sink pin balance。

图2.ICC2 clock属性

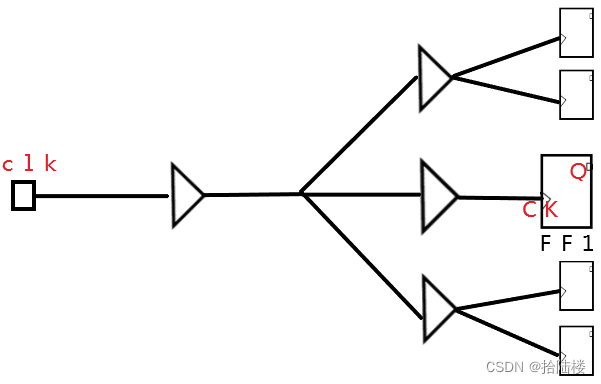

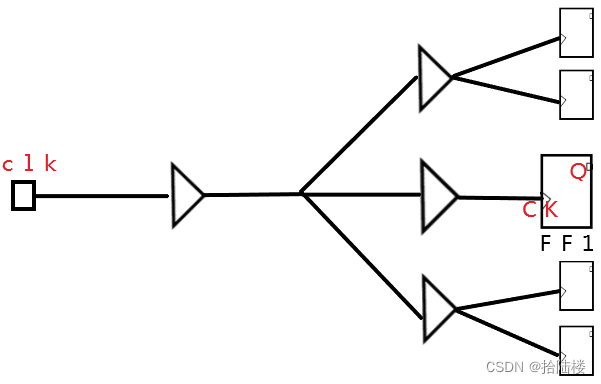

CTS后时钟树结构如图3,此时FF1/CK需要balance,不再是through pin了。

图3

2)如果inst是一个reg/icg,inst/pin是一个input pin。

set_sense -stop_propagation -type clock -clocks [get_clocks clk] [get_pins FF1/CK]

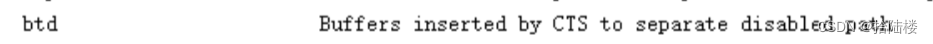

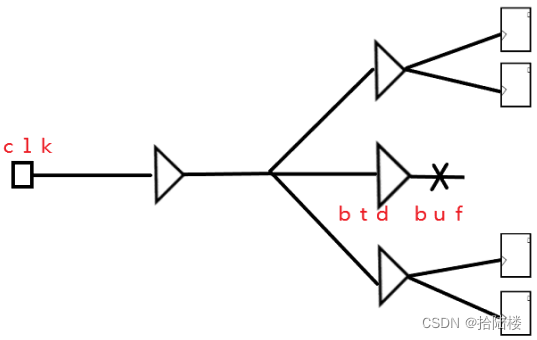

此时FF1/CK会被当做exclude pin,CTS阶段也不会balance,但是会给它前面插一个特殊buf,表示clock clk在这后面的分支不长tree,ICC2中这个特殊的buf命名规则是*btd*(定义见图2),buf前使用clock tree约束修drc violation(max_tran/max_cap),buf后使用data path的约束修drc violation,同样的如果inst后面有generate clock,set_sense也会让它单独长tree,不跟clock clk其他sink pin banlance。

图4.btd buf的定义

CTS之后时钟树结构如图5,此时FF1/CK作为exclude pin。

图5

3)如果inst不是一个reg/icg,可能是个buf,那么结果跟2)的情况一样。

2、set_sense -clock_leaf

给指定clock设置leaf pin(clock endpoint)。

set_sense -clock_leaf -clocks [get_clocks clk] [get_pins FF1/CK]

给clock clk设置leaf pin FF1/CK,FF1/CK是clock pin所以这里作为sink pin,设置在非clock pin上相当于exclude pin。此时CTS结果如图6,此时FF1在clock clk时钟树上需要balance,在FF1/Q之后的generate clock需要自己balance,效果和set_sense -stop_propagation -type clock -clocks [get_clocks clk] [get_pins FF1/Q]是一样的。

图6

3 应用

分频时钟的寄存器不与主时钟或者主时钟下的分频时钟有timing check,则可以使用set_sense -stop_propagation 在分频器定义的寄存器的CK pin上,cts阶段分频时钟单独长tree不与主时钟sink balnace,cts之后可以用remove_sense移出set_sense后做时序分析。set_sense和remove_sense都不需要放到sdc里,在clock_opt前后使用即可。

最后

以上就是伶俐裙子最近收集整理的关于静态时序分析—set_sense1、set_sense -stop_propagation2、set_sense -clock_leaf 3 应用的全部内容,更多相关静态时序分析—set_sense1、set_sense内容请搜索靠谱客的其他文章。

发表评论 取消回复