数字后端流程学习

1.数据准备

2.布局规划

3.布局

4.时钟树综合

5.布线(route)

6.签核(signoff)

Innovus软件使用介绍

encounter到innovus

数据准备:物理文件;时序文件;

物理文件:

网表(RTL代码综合后形成);

LEF(线宽,metal需要满足的路);

DEF(交换的文件,生产第三方工具);

Scan文件(扫描链信息);

时序文件:(下一次课)。

网表Netlist:RTL代码经过综合工具生产Gate level文件,RTL和Gate level 都是verilog代码的形式,经过综合以后会生成门级电路的verilog代码。gate l;evel是门级电路。

LEF:物理库信息:包括metal(几层),via(通孔大小),macro cell,standard cell。

technology LEF提供工艺信息,定义via的大小,每一层金属的具体信息

Macro LEF:整个器件的样子

DEF:设计交换格式。

包括floorplan信息,routing,placement

Innovus数据格式介绍:

enc.dat:

.globals:全局参数设置

.mode:特殊参数设置

viewDefinition.tcl:所有时序文件

.v:网表

lib/:设计库

mmmc/:时序库

.fp,.place等:设计信息

数据导入

source 目标文件的目录

数据保存 save

Block实现:

Floorplan:

1.确定芯片面积;

2.I/O单元的摆放

3.硬核,模块的摆放

box:die,io,core:LL:左下角坐标,UR:右上角坐标

row:规定了自动布局的方向,createrow,deleterow

track:一般无需改变

IO:保存步骤:saveloFile test.io

macro:模块尽量摆在靠近相应输入输出出口的位置,macro和macro之间要留一定空隙,合理摆放角度。先用工具跑个大概,然后进行微调

constraint:向导约束(可进可出),区域约束(可进不可出),限制约束(不可进不可出),

placement blockage,route blockage,

halo:是跟随cell生长的,相当于blockage

instance group:不同modeule中类似的模块形成一个小组。

**partition:**后期会详细介绍。

power plan:电源规划(PPPR)

产生一个满足IR drop EM的供电网络,尽量减少routing track 的资源

ring 可以提供稳定的电源,但是占面积比较大;stripe:电源条线,

power route=sroute

viagen 产生power via

GNC:定义全局电源

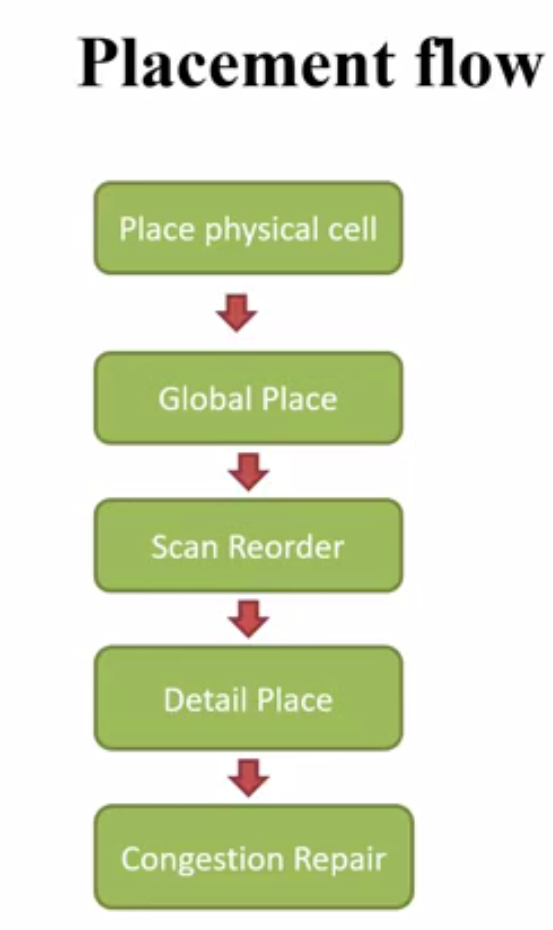

placement:

关键单元应该摆放在核心区域

标准单元必须摆对正确的方向

没有overlap

没有违反floorplan等。

endtap

welltap(防止出现latch_up):一般交错摆放,

global placement;

detail place;

congestion repair:修改局部有violation的地方。

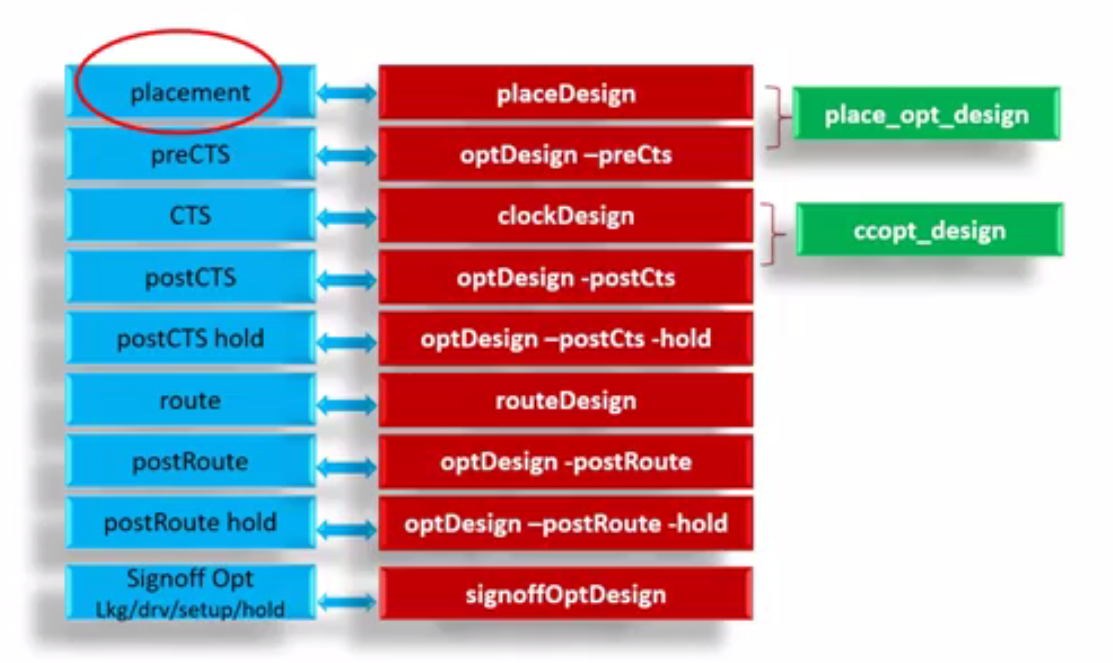

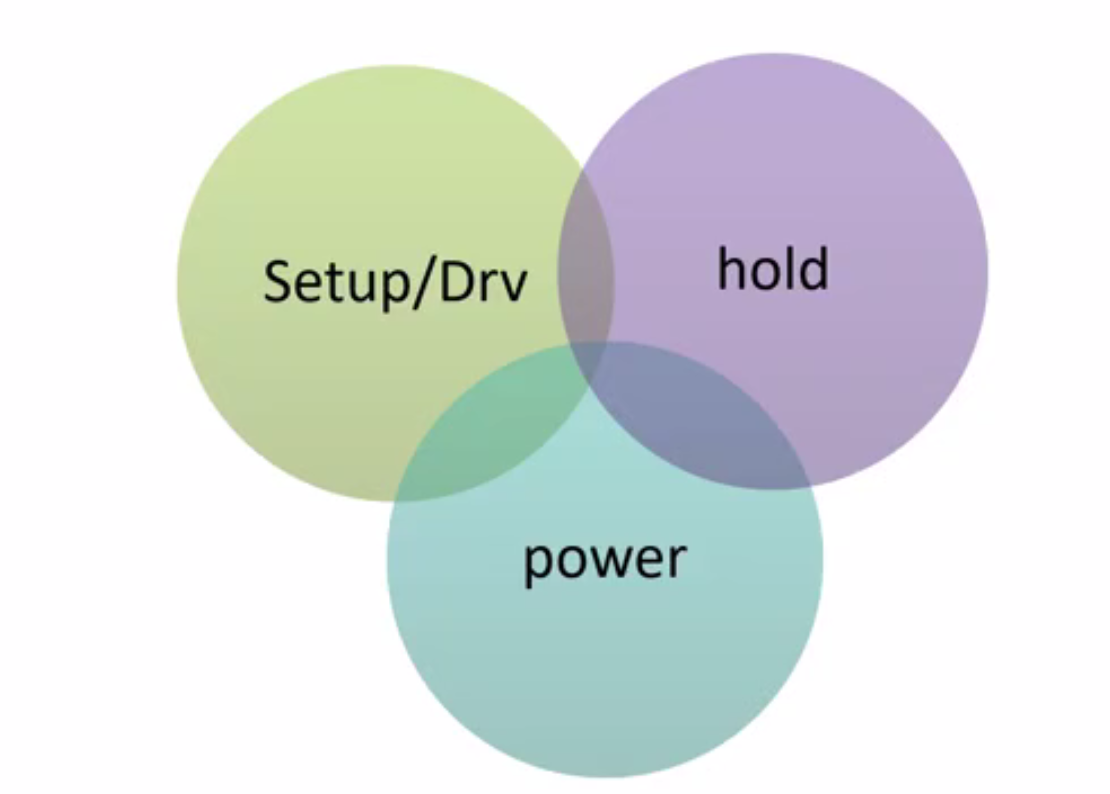

opt:结构示意图

DRV:design rule violation,

power(静态功耗),

hold

修复手段:add buffer:添加Buffer或者invertor

resize:增大或者减小buffer的尺寸

move:移动std cell的位置

pin swap:改变引脚的接入;

restruct:优化一些电路的结构;

layer assignment:改变走线的位置;

运行opt的命令

如何将OPT做的更好:

可以通过输入命令,查看参数的好坏:

sdc:checking_timing,

place_opt_design:同时完成place 与opt

cts:

1.保持信号的完整性:latency,skew,transition,uncertainy,level

2.平衡时钟树节点

latency:1.source latency,2.network latency,

skew:globallocal skew:最大延迟与最小延迟的差值

transition time,slew:

clock uncertainty:

level:root pin,sink pin,leaf pin,trunk pin.

如何运行:

ccopt_design

skew group,

clock tree,每一个clock就是一个skew group,

Ignore pin,stop pin,exclude pin,

spec:工具自己算出来的

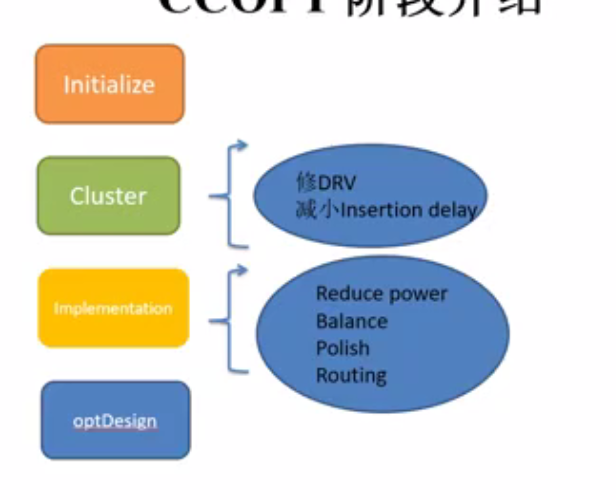

ccopt:阶段介绍 initialize,cluster,implementation,optdesign

ccopt effort:推荐使用low effort

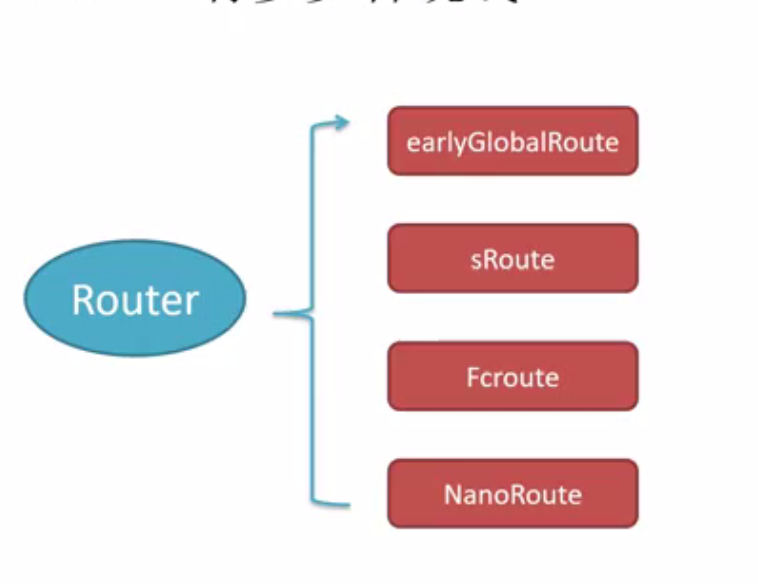

route

earlyglobal route:只关心最基本的spacing rule,速度快

sroute:连接电源布线

fcroute:用于倒装焊设计

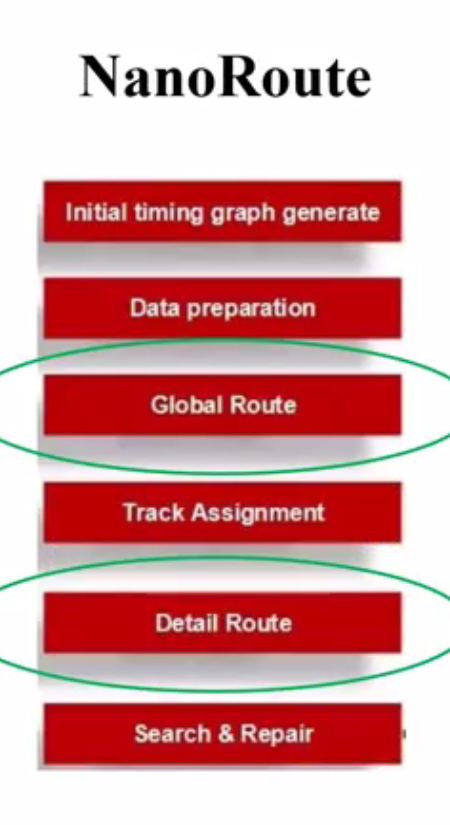

nanoroute:比较重要(smart route)

在route的时候考虑串扰,可制造性的设计,timing-driven

检查placement的合理性,检查power routing,检查LEF,检查Timing libraryconstrain。

track assignment

setup,hold,√

eco:

addrepeater,

changecell(用指令整体操作)

工程更改指令

最后

以上就是温柔大叔最近收集整理的关于数字后端流程学习1的全部内容,更多相关数字后端流程学习1内容请搜索靠谱客的其他文章。

发表评论 取消回复