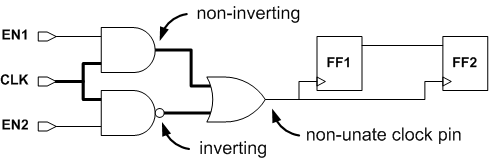

理论上来说,时钟电路只能经过寄存器时钟端、buffer(正相关、inverter(负相关),clock 经过or ,xor等除了与门和非门外的其他逻辑,就会被叫做non_unate。

(1)一种可能是,作为时钟使用时,并不会走导致non-unate的路径。这时候,可以设置clock source 到 non-unate,数据路径的false path;或者对此warning不处理。

(2)第二种可能是,确实经过了non-unate时钟路径。

此时可能报告PTE-070,PTE-070警告是指非UNATE逻辑,而不是非UNATE单元格。

非单调时钟逻辑是指在传播过程中时钟的两种方向(非反转和反转)一起到达同一引脚的情况。

这不需要非unate单元格,也会发生unate logic。

当然,如果时钟逻辑包含具有反转和非反转圆弧的非UNATE单元,则时钟逻辑也将显示相同的特性。

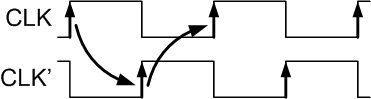

两种时钟感知器都是向下游传播的,这导致一个重要的时序结果。对于两种感觉都被传播的时钟域,每个时序器件都是由上升边缘和下降边缘共同触发的。因此,最保守的设置关系将在两个时钟传感器之间,并将导致半周期设置路径。

两种时钟感知器都是向下游传播的,这导致一个重要的时序结果。对于两种感觉都被传播的时钟域,每个时序器件都是由上升边缘和下降边缘共同触发的。因此,最保守的设置关系将在两个时钟传感器之间,并将导致半周期设置路径。

保持路径也会受到类似的影响。通常,这些检查是无效的,因为在任何给定时间,时钟网络中只有一个时钟感知器。

为了解决歧义可以使用:

set_sense

set_clock_groups (在冲突pin上创建带和不带反转的两个生成时钟,并使用以下命令声明独占时钟关系)

set_case_analysis

set_disable_timing

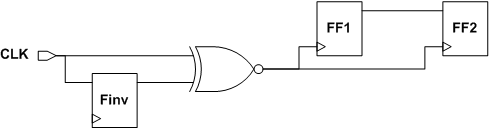

生成时钟技术将允许同时对两种时钟感知进行定时分析,同时智能地抑制交叉感知时序路径。

create_generated_clock -add

-name CLK_noninverted

-combinational

-source [get_ports CLK]

-master CLK

[get_pins UOR/Z]

create_generated_clock -add

-name CLK_inverted

-combinational -invert

-source [get_ports CLK]

-master CLK

[get_pins UOR/Z]

set_clock_groups -physically_exclusive

-group CLK_noninverted -group CLK_inverted

最后

以上就是哭泣月饼最近收集整理的关于non-unate clock即非单调时钟的全部内容,更多相关non-unate内容请搜索靠谱客的其他文章。

发表评论 取消回复