时序约束

###1. clock

# 在设计之初 并不知道设计所能跑的时钟周期能有多小; 根据DC ICC 都是多次迭代 获得最优解的原则 ; 一开始先给自己的估计值;

# 对于180nm 的库来说, 由于IO pad 的限制 , 最多能跑100Mhz左右 当然单独综合core 的频率会更大一些;

#一开始 我们设置5ns 一开始紧一些 可以更快的获得 设计的时钟顶;

# set clock constrians

create_clock -period 5 [get_ports clk]

set_dont_touch_network [get_ports clk]

set CLOCK1 [get_clocks clk]

set_clock_latency -source -max 0.5 $CLOCK1

set_clock_latency -max 0.5 $CLOCK1

set_clock_uncertainty -setup 0.35 $CLOCK1 ;#clock period 5%;skew=0.04,jitter=0.03,margin=0.03

set_clock_transition -max 0.2 $CLOCK1

#max_fanout

#max_fanout是一个设计规则约束;

对于 REG -REG 的path 需要我们提供哪些约束for setup time?

主要是时钟相关的约束;

- 占空比 仅仅在你的设计中寄存器是在时钟的上升沿和下降沿都触发的时候才必须指定,对于都是时钟上升沿触发的路径,仅需要指定时钟周期即可,DC会从工艺库中拿出setup_time进行计算;

- 除非指定了waveform option ,默认的时钟在0时刻上升在50%下降依次重复;时钟的名字必须和时钟引脚的名字一致,除非使用-name选项指定;

- 如果你想知道时钟的单位的话 可以通过report_lib 来查看库里规定的单位;或者get_attribute <lib_name> time_unit_name

input path的约束

- input_daly

- 上一级模块所要保留的最大时间 是 P - input_delay(max)- clock_uncertainty - register setup_time

- 一般预留40%在自己的电路部分

output path的约束

- output_delay

- 下级模块所要保留的时间 就是 P-clock_uncertainty - output_delay;

输入输出延迟默认会继承在set_clock_latency和uncertainty的值

也就是输入输出延迟的计算是在附加clock_latency和clock_uncertainty的时钟的launch &capture计算的;

对于纯组合逻辑电路来说

需要创建虚拟的时钟去分析纯组合逻辑路径的时序,

指定input_delay 和output_delay 也就是说和design 外部的时序同步起来,也就是在comb两边加两个寄存器,使它成为一个带时序的路径,然后估算他的path time;

除了上面的输入输出 delay

那些都是需要的,除此之外还要指定input_transition 和output_load

上面的那些约束只是描述regreg input output path多少时间是可行的;但没有描述在什么样的条件下这些delay必须满足;

门的延迟是它 input_transition和output_load的函数,默认 DC对于output port声明理想的负载(zero),对input port声明理想的transition time(zero);这会导致比较乐观的path timing;为了更加精确的path timing 必须对input_transition和output_load 做精确的建模.

输入转换时间和输出负载的影响

输入端口的上升和下降转换时间影响后边门的cell delay

输出电容负载的大小会影响到transition time 电平的转换时间

set

set_input_transition or set_driver_cell 二选一; 一个是指定确定的transition time的值 一个是通过库中的单元信息估算transition time;

set_driver_cell -max -lib_cell OR3B [get_ports all_inputs]

set_input_delay -max [grt_ports all_inputs]

#output load

set_load -max [expr{30.0/1000}] [get_ports all_outputs]

#或者

set_load -max [load_of my_lib/AN2/A] get_ports [all_outputs]

在输入输出电路结构都不知道的情况下 如何做load budget

- 为input_pins 设置比较小的driving_cell 比如一个反相器

- 为output_load 设置个较大的负载 比如3个与门;

补充 2022 08 13

SDC主要分6部分内容

包括:

- operation condition & wire load mode

- timing constrains

- 设计规则约束

- 时序例外

- logic assignments (设置逻辑确定的约束值 set_case_analysis set_logic_zero)

- 优化用约束 如set_max_delay set_max_area

时钟约束

创建时钟

#使用

create_clock -name clk -period 15 -waveform {5 10} get_clock clk

#其中 waveform 指定的是第一个上升沿和下降沿??yes

#对于 生成时钟

create_generated_clock -divide_by 2 -source clk [get_pins FF1/Q]

#其中source 是源时钟, edge是??

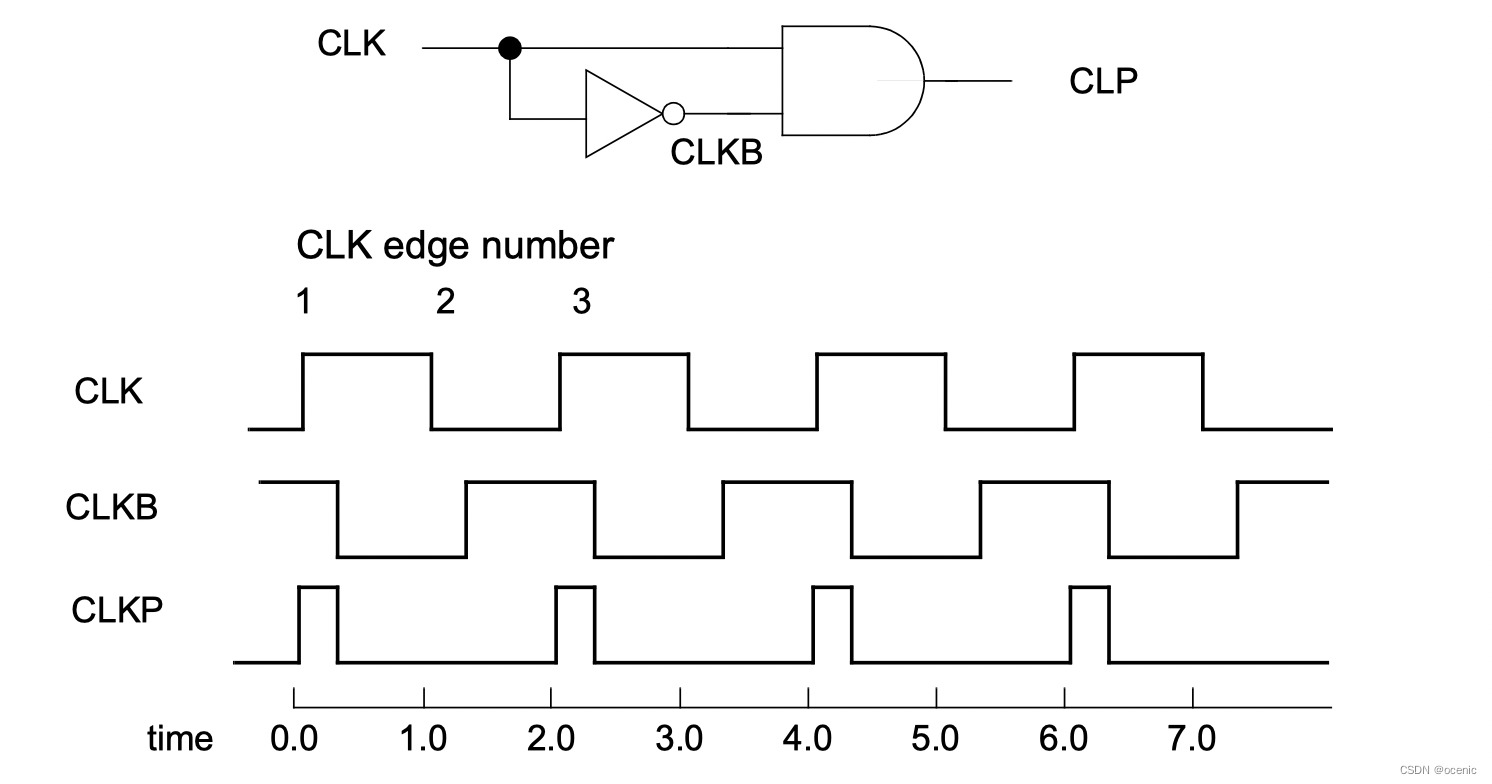

理解eage选项的用法,这里介绍脉冲时钟;

pulse clock

脉冲时钟是由一系列短脉冲组成,脉冲的上升沿和下降沿均来自同一时钟的同一沿生成的,PT为了对这种生成时钟进行分析需要获得这个时钟的一些时序信息;有三种方法:

- 直接使用库中标注了时序信息的 pulse generator;

- 使用 create_generated_clock 去描述pulse与source clock的时序;

- 使用 set_sense -type clock 指定生成时钟对于源时钟的意义??

最好的方法是直接使用 库中做了标注的 pulse generator;

如图,所示同一个沿生成了CLKP的上升沿和下降沿,pulse的宽度取决于inverter的延迟;

create_generated_clok -name CLKP -source CLK -edges {1 1 3} [get_pins and2/z]

-edges 主要有4种搭配

{1 1 3} 源时钟上升沿触发high pulse

{2 2 4} 源时钟下降沿触发high pulse

{1 3 3} 源时钟上升沿触发low pulse

{2 4 4} 源时钟下降沿触发low pulse 凹脉冲

clock skew 和 latency

clock skew 时序单元时钟端时钟到达时间的不同

clock latency是时钟从源到叶子节点总的延迟时间;

在设计周期的较早阶段,会使用理想的时钟树进行静态时序分析;理想时钟树中的clock skew默认为0,可以使用 clock uncertainty指定;latency使用 set_clock_latency来建模;

set_clock_latency 2.2 [get_clocks SYS_CLK]

set_clock_uncertainty -setup

#clock skew 5% + jitter 0.01%

synchronous clock & asynchronous clock

同步时钟

- share a common source

- have a fixed phase relationship

除非你指定, STA工具会假定存在数据launch和capture的路径上的两个时钟是同步的;

异步时钟

两个时钟域的时钟沿没有任何关系,STA工具不会分析launch by one capture by another one的路径;

互斥时钟组

logic exclusive 逻辑互斥

1. do not have a function path

2. but may have coupling interaction

在逻辑上相互排斥,但互相之间可能存在耦合影响,比如两个时钟被MUX选通,但会收到MUX内部coupling upstream影响;

physical exclusive 物理互斥

两个时钟不会同时存在于设计中,例如function clock 和test clock ,例如多个时钟定义在同一个pin上,但同时只有一个可以活跃在设计中.

IO path constrains

对于输入输出端口,假设上一级与本级同步,需要上级寄存器 tcq,寄存器D端到 输入pin中间的组合逻辑时间;

set_input_delay -max 7.4 -clock CLk [get_ports A]

set_input_delay 1.5 -clock CK1 [get_pins IN1]

set_input_delay 2 -clock CK2 [get_pins IN1] -add_delay

#使用add_delay 选项对 同一个输入pin 不同的时钟路径,进行约束;

输出引脚的约束 与输入引脚类似;

输入输出引脚外部的时钟需要通过virtual clock定义

create_clock -那么 VCLK -period 20

false path

false_path 是对于那些实际中不存在,不能被激活的路径且在时序分析中是毫不相干;

设置false_path 可以避免工具不必要的优化; 但是无效的false_path 会掩盖真正的时序违例;

multi-cycle path

一些路径上存在非常负载的组合逻辑,不能在一个周期内完成计算;

默认综合工具会优化这些组合逻辑,通过重新分配单机流水线的宽度,使其满足单周期的要求;

添加multi-cycle path会放松此条路径上的约束;

set_multicycle_path -setup 6 -from -to

set_multicycle_path -hold 5 -from -to

#为啥 hold要比 setup 早一个??

# 暂时理解为 hold 都是在capture 沿进行检查 所以 capture 到 capture 比 launch 到 capture 少一个周期.

set max delay

设置路径的最大延迟,此约束会覆盖掉根据时钟的launch和capture edges到达时间所建立的默认建立时间约束;

设置max min delay之后 在时序分析时 data require time会根据 max_delay 去计算;

最后

以上就是如意戒指最近收集整理的关于创建DC时序约束文件的全部内容,更多相关创建DC时序约束文件内容请搜索靠谱客的其他文章。

发表评论 取消回复