一、有限状态机设计的一般步骤:

1) 逻辑抽象,得出状态转换图

就是把给出的一个实际逻辑关系表示为时序逻辑函数,可以用状态转换表来描述,也可以用状态转换图来描述。这就需要:

• 分析给定的逻辑问题,确定输入变量、输出变量以及电路的状态数。通常是取原因(或条件)作为输入变量,取结果作为输出变量。

• 定义输入、输出逻辑状态的含意,并将电路状态顺序编号。

• 按照要求列出电路的状态转换表或画出状态转换图。这样,就把给定的逻辑问题抽象到一个时序逻辑函数了。

2) 状态化简

如果在状态转换图中出现这样两个状态,它们在相同的输入下转换到同一状态去,并得到一样的输出,则称它们为等价状态。显然等价状态是重复的,可以合并为一个。电路的状态数越少,存储电路也就越简单。状态化简的目的就在于将等价状态尽可能地合并,以得到最简的状态转换图。

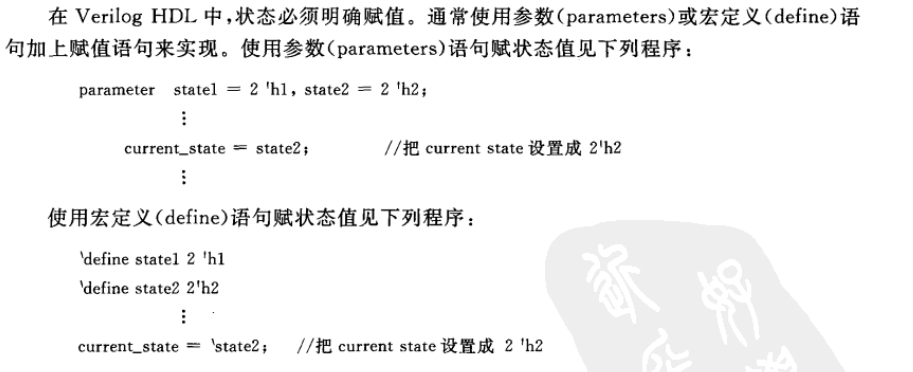

3) 状态分配

状态分配又称状态编码。通常有很多编码方法,编码方案选择得当,设计的电路可以简单,反之,选得不好,则设计的电路就会复杂许多。实际设计时,需综合考虑电路复杂度与电路性能之间的折衷,在触发器资源丰富的FPGA或ASIC设计中采用独热编码(one-hot-coding)既可以使电路性能得到保证又可充分利用其触发器数量多的优势。

4) 选定触发器的类型并求出状态方程、驱动方程和输出方程。

5) 按照方程得出逻辑图

二、可综合状态机知道原则

因为大多数FPGA内部的触发器数目相当多,又加上独热码状态机(one hot state machine)的译码逻辑最为简单, 所以在设计采用FPGA实现的状态机时往往采用独热码状态机(即每个状态只有一个寄存器置位的状态机)。

建议采用case,casex,或casez语句来建立状态机的模型, 因为这些语句表达清晰明了,可以方便地从当前状态分支转向下一个状态并设置输出。

不要忘记写上case语句的最后一个分支default,并将状态变量设为'bx,这就等于告知综合器:case语句已经指定了所有的状态,这样综合器就可以删除不需要的译码电路,使生成的电路简洁,并与设计要求一致。

如果将缺省状态设置为某一确定的状态(例如:设置default:state = state1)行不行呢?

回答是这样做有一个问题需要注意。因为尽管综合器产生的逻辑和设置default:state='bx时相同,但是状态机的Verilog HDL模型综合前和综合后的仿真结果会不一致。为什么会是这样呢?

因为启动仿真器时,状态机所有的输入都不确定,因此立即进入default状态,这样的设置便会将状态变量设为state1,但是实际硬件电路的状态机在通电之后,进入的状态是不确定的,很可能不是state1的状态,因此还是设置default: state='bx与实际情况相一致。

但在有多余状态的情况下还是应将缺省状态设置为某一确定的有效状态,因为这样做能使状态机若偶然进入多余状态后还能在下一时钟跳变沿时返回正常工作状态,否则会引起死锁。

状态机应该有一个异步或同步复位端,以便在通电时将硬件电路复位到有效状态,也可以在操作中将硬件电路复位(大多数FPGA结构都允许使用异步复位端)。

目前大多数综合器往往不支持在一个always块中由多个事件触发的状态机(即隐含状态机,implicit state machines), 为了能综合出有效的电路,用Verilog HDL描述的状态机应明确地由唯一时钟触发。

目前大多数综合器不能综合采用Verilog HDL描述的异步状态机。异步状态机是没有确定时钟的状态机,它的状态转移不是由唯一的时钟跳变沿所触发。

千万不要使用综合工具来设计异步状态机。 因为目前大多数综合工具在对异步状态机进行逻辑优化时会胡乱地简化逻辑,使综合后的异步状态机不能正常工作。 如果一定要设计异步状态机,我们建议采用电路图输入的方法,而不要用Verilog HDL输入的方法。

什么是同步状态机什么是异步状态机?

同步状态机:同步状态机的时钟是由同一时钟产生的,通过特殊设计的全局时钟网络将唯一的时钟连接到每个触发器的时钟端,使得时钟沿到达每个触发器时钟端的时刻几乎完全相同。

异步状态机:异步状态机没有确定的时钟,它的状态转移不是由唯一的时钟跳变沿所触发。

最后

以上就是冷静皮卡丘最近收集整理的关于verilog之状态机详细解释(二)目前大多数综合器不能综合采用Verilog HDL描述的异步状态机。异步状态机是没有确定时钟的状态机,它的状态转移不是由唯一的时钟跳变沿所触发。千万不要使用综合工具来设计异步状态机。 因为目前大多数综合工具在对异步状态机进行逻辑优化时会胡乱地简化逻辑,使综合后的异步状态机不能正常工作。 如果一定要设计异步状态机,我们建议采用电路图输入的方法,而不要用Verilog HDL输入的方法。的全部内容,更多相关verilog之状态机详细解释(二)目前大多数综合器不能综合采用Verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复