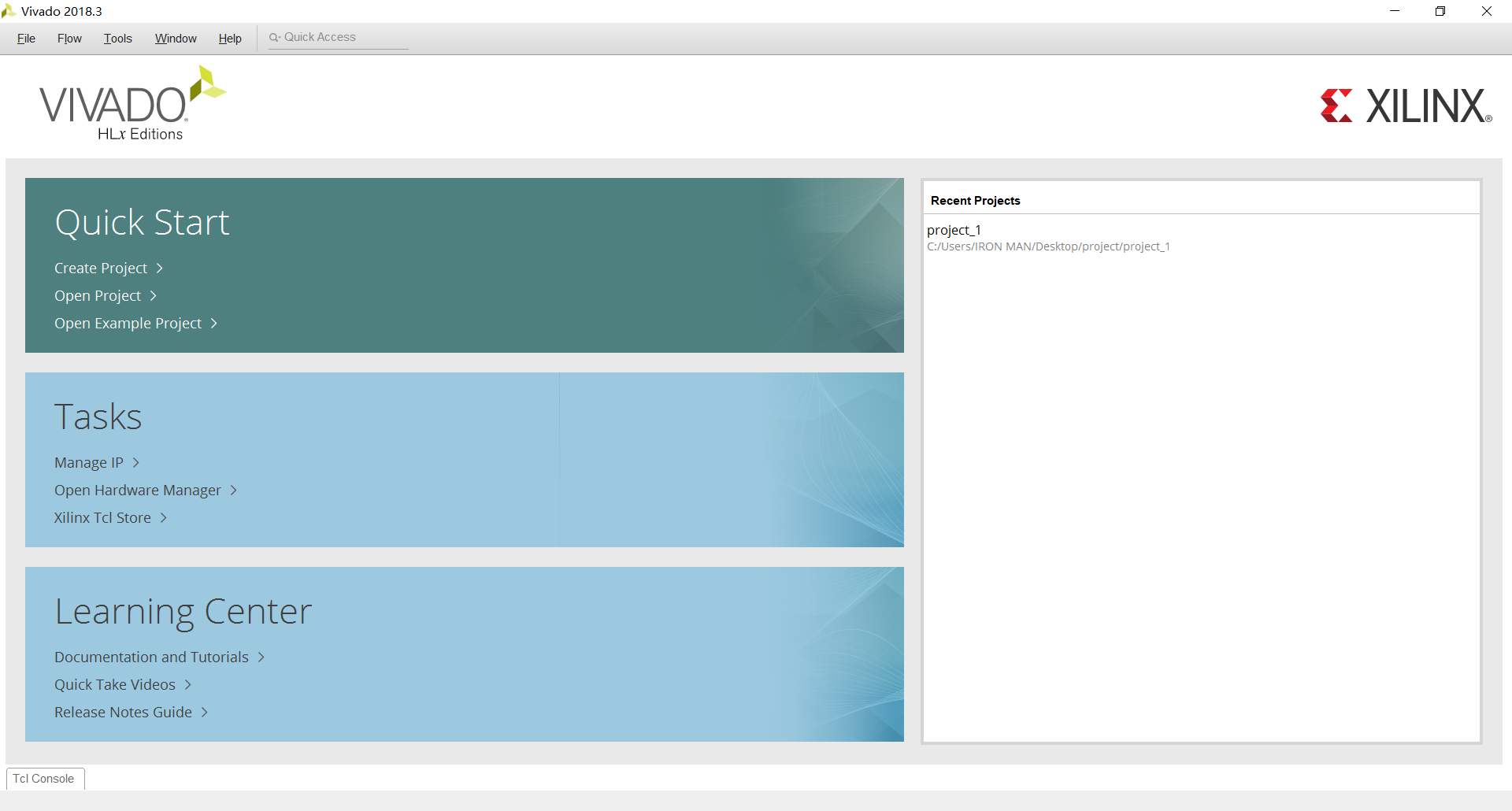

一、项目创建

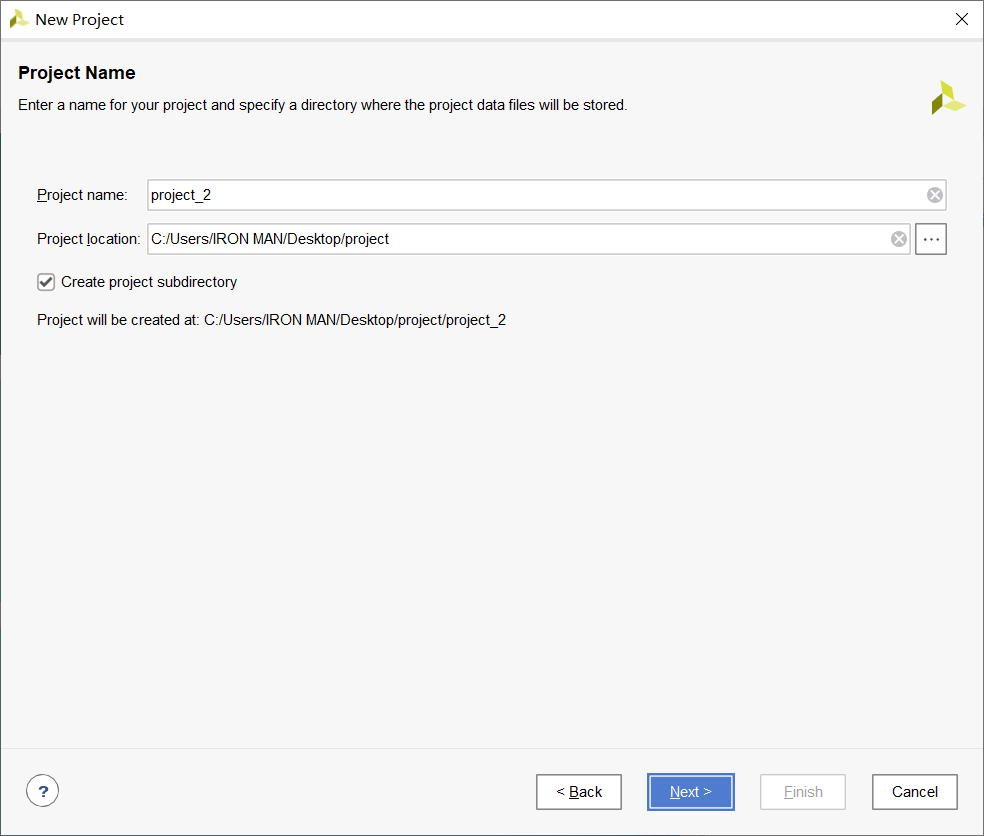

1、creat project 2、确认项目名和项目位置,“√”确认生成子目录

2、确认项目名和项目位置,“√”确认生成子目录

3、生成RTL项目文件,且“√”不添加特殊源文件

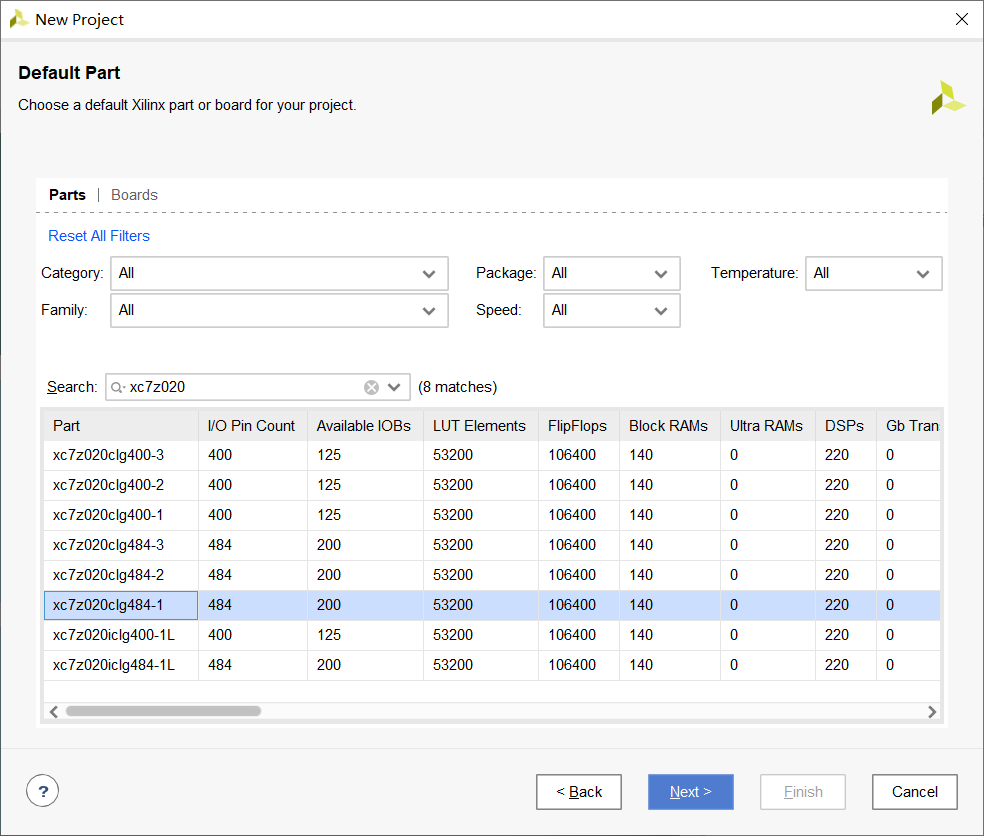

4、根据上面的筛选项或直接输入型号,找到对应FPGA开发板

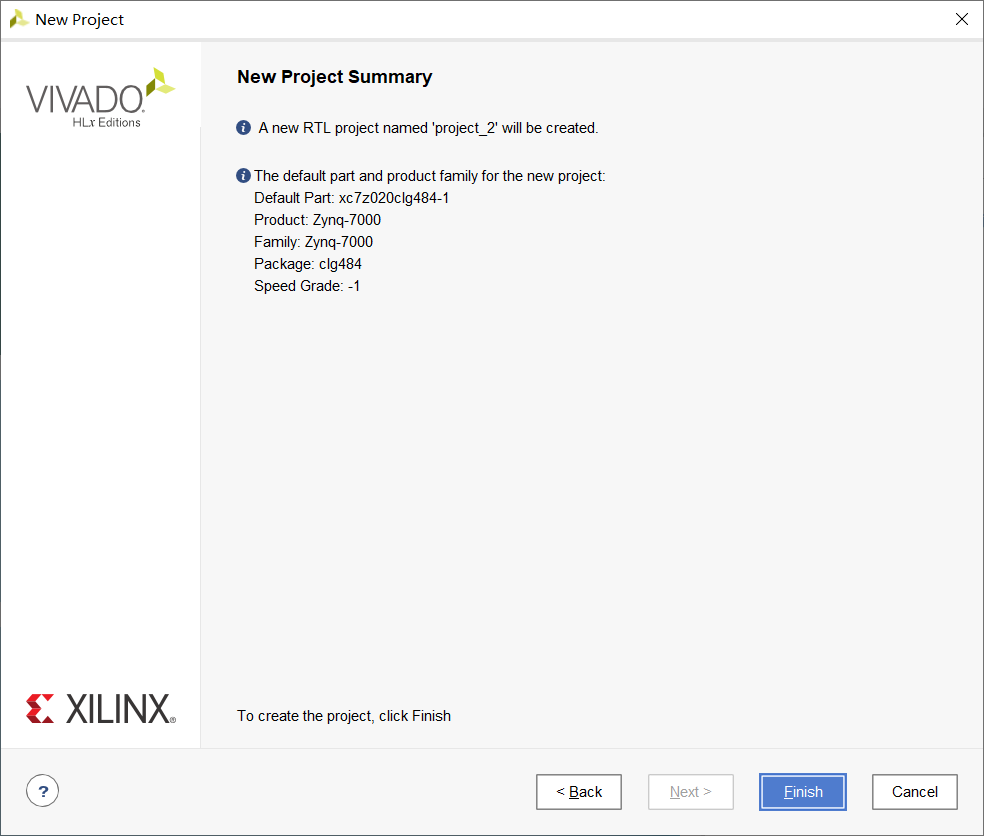

5、确认信息

二、编辑源文件

1、设计源文件

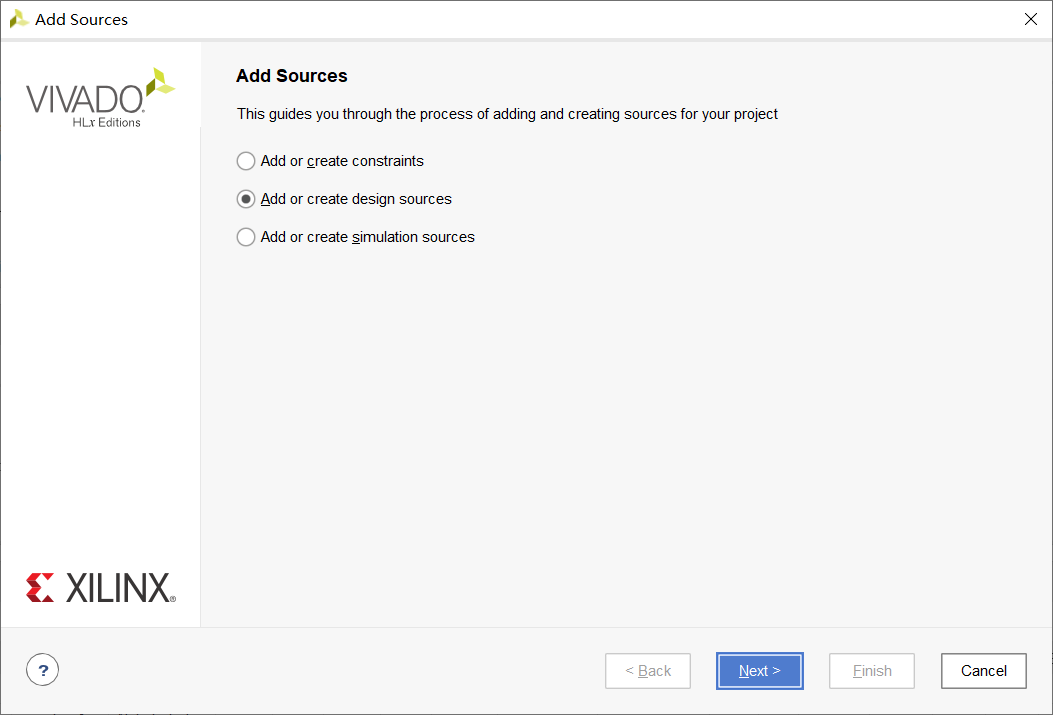

添加源文件(add sources →design sources)

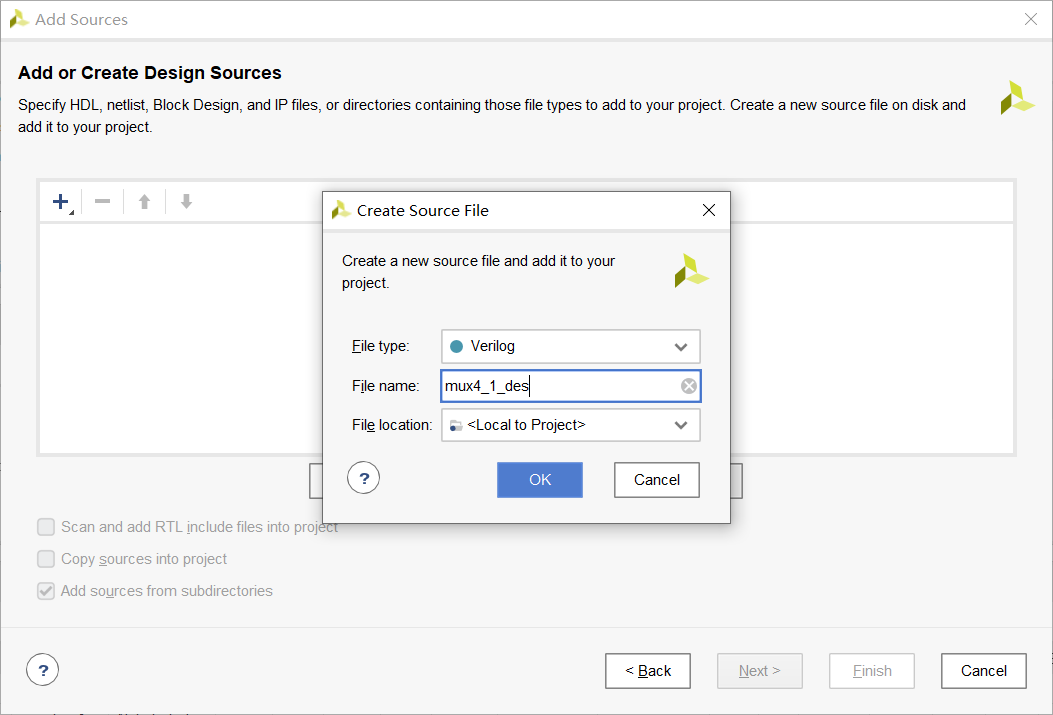

确认源文件名

添加源文件代码

module mux4_1_des(

input wire [1:0]sel,

input wire s1,

input wire s2,

input wire s3,

input wire s4,

output wire led

);

assign led=(!sel[0]&!sel[1]&s1)|(sel[0]&!sel[1]&s2)|(!sel[0]&sel[1]&s3)|(sel[0]&sel[1]&s4);

endmodule

2、添加顶层文件(通过顶层文件调用源文件,养成良好编程习惯)

add sources →design sources→creat source file

添加顶层文件代码

module mux4_1_topdes(

input wire [5:0]sw,

output wire led

);

mux4_1_des m(

.sel(sw[5:4]),

.s1(sw[0]),

.s2(sw[1]),

.s3(sw[2]),

.s4(sw[3]),

.led(led)

);

endmodule

三、行为仿真(提供仿真输入信号)

1、创建仿真文件(add sources→simulation sources)

2、添加仿真文件代码

module mux4_1_sim();

reg s1,s2,s3,s4;

reg [1:0]sel;

wire led;

mux4_1_des test(

.sel(sel),

.s1(s1),

.s2(s2),

.s3(s3),

.s4(s4),

.led(led)

);

initial begin

#0

s1=0;

s2=1;

s3=1;

s4=1;

sel=2'b00;//1

#100

s1=1;

s2=0;

s3=1;

s4=1;

sel=2'b01;//2

#100

s1=1;

s2=1;

s3=0;

s4=1;

sel=2'b10;//3

#100

s1=1;

s2=1;

s3=1;

s4=0;

sel=2'b11;//4

#100

s1=1;

s2=0;

s3=0;

s4=0;

sel=2'b00;//5

#100

s1=0;

s2=1;

s3=0;

s4=0;

sel=2'b01; //6

#100

s1=0;

s2=0;

s3=1;

s4=0;

sel=2'b10; //7

#100

s1=0;

s2=0;

s3=0;

s4=1;

sel=2'b11;//8

#100

$finish;

end

endmodule

3、把仿真源文件设为top模块

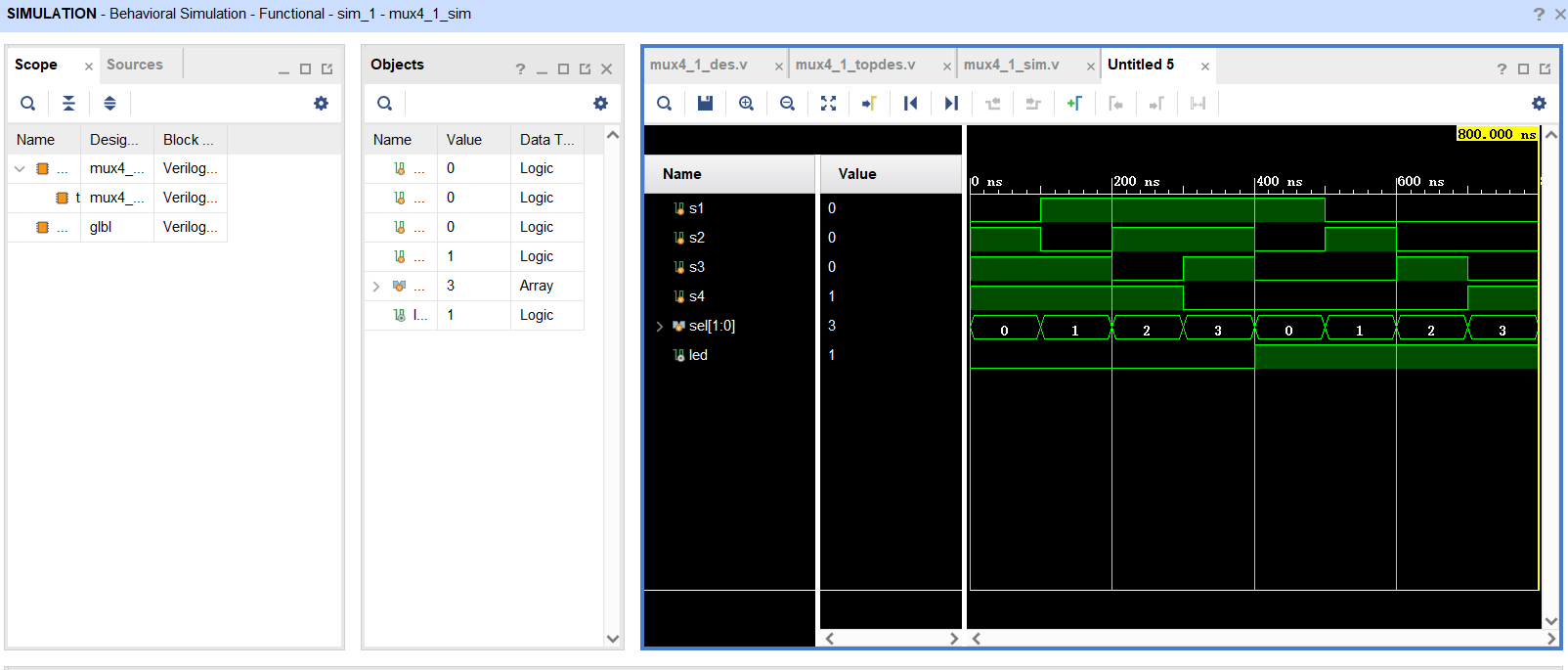

4、运行行为仿真(synthsis→open synthsis→run behavioral simulation),检查仿真结果是否正确

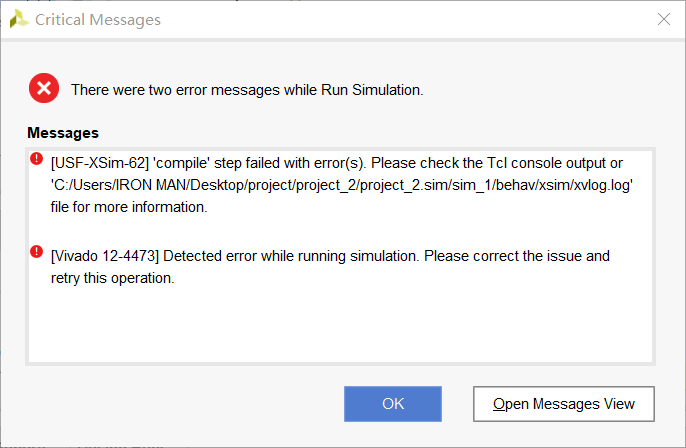

注意可能会出现如下错误,请修改仿真文件里的变量类型(reg wire)

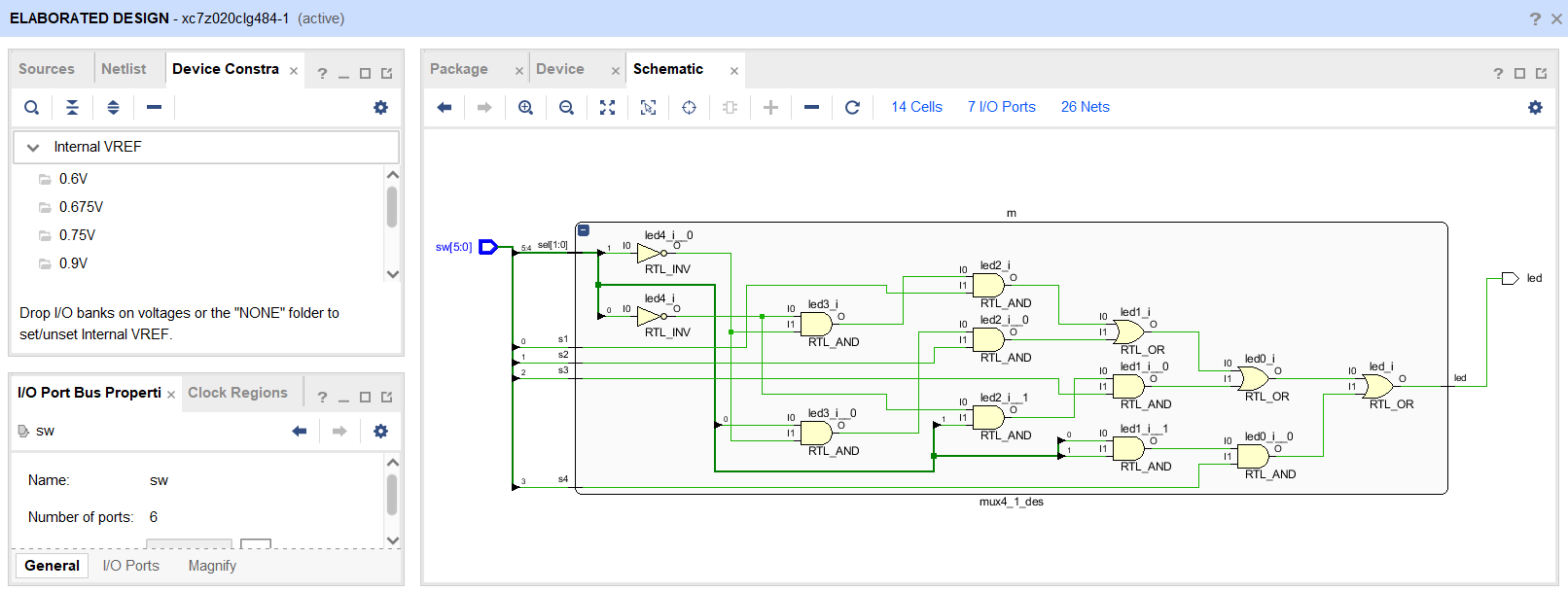

四、RTL分析

在rtl分析中打开原理图(RTL ANALYSIS→open elaborated design),查看设计是否满足要求

五、综合,编写约束文件

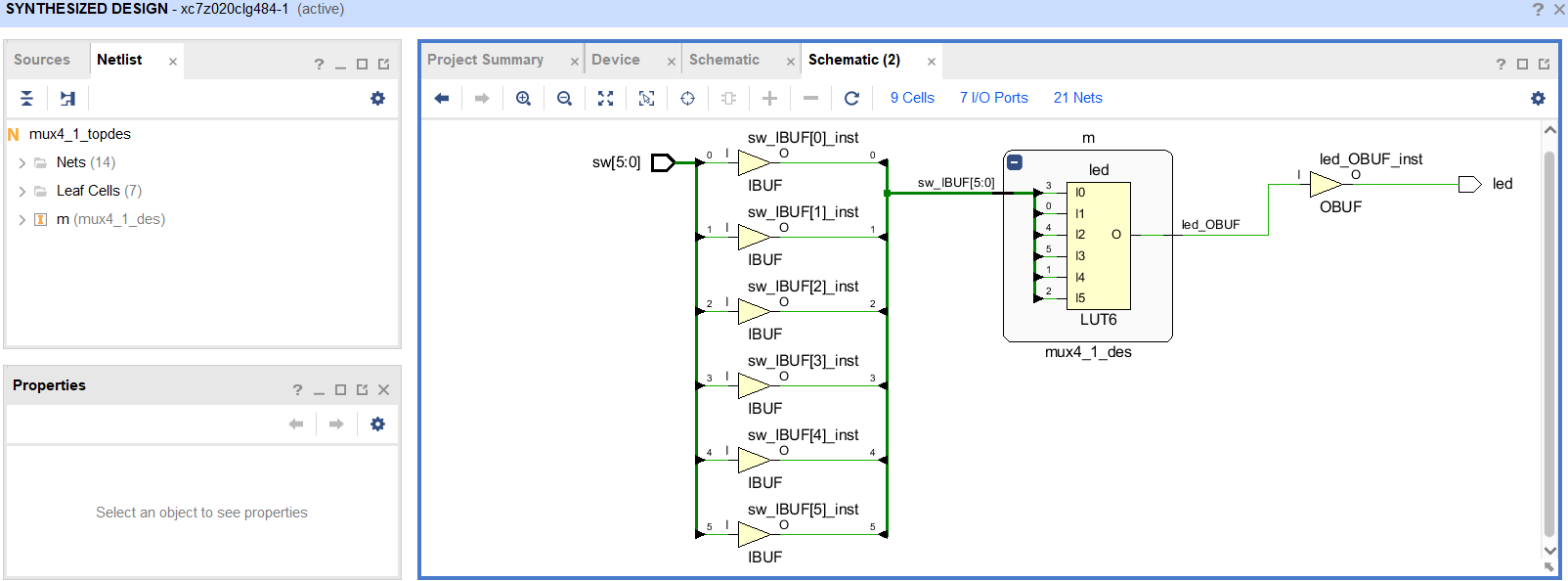

1、综合(run synthsis→open synthsizd design→schematic),

查看原理图,这个原理图跟rtl的原理图不同,这个是与器件相关的,而rtl原理图只是将硬件编程语言用电路图描述出来。

(如果看原理图只能看到device,在左侧菜单栏里寻找schematic点击即可)

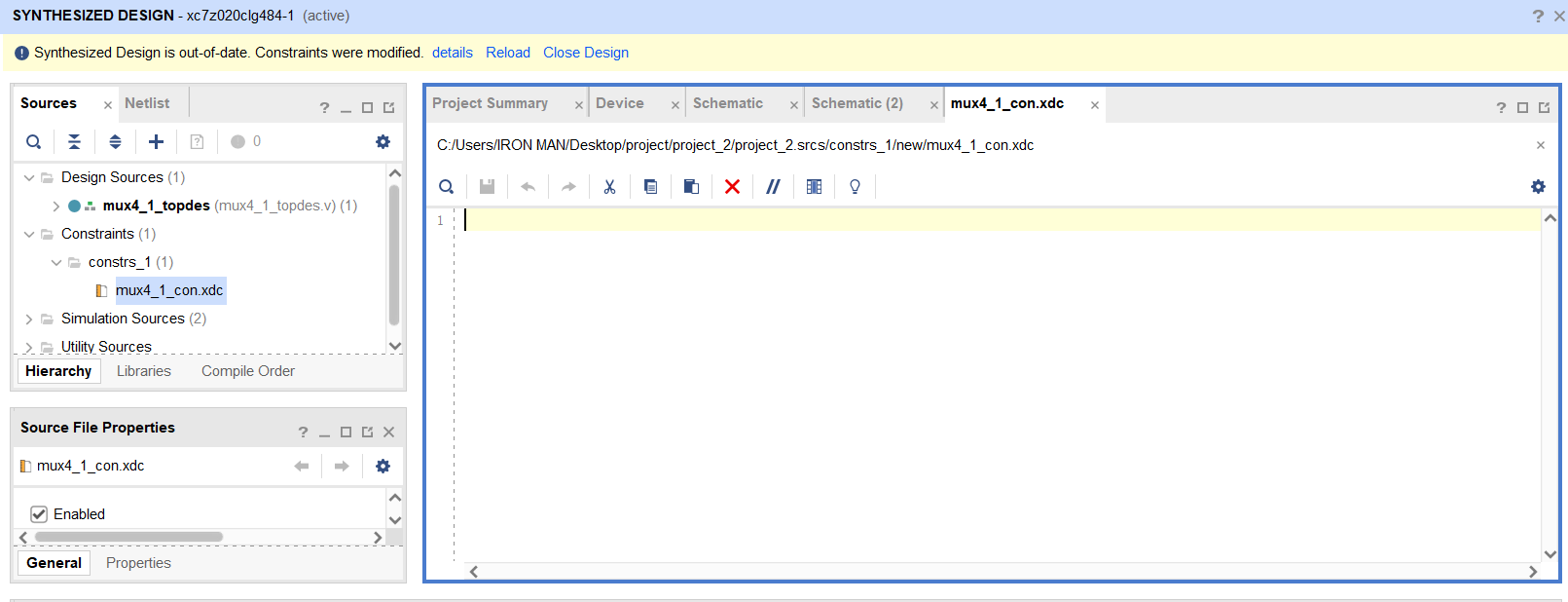

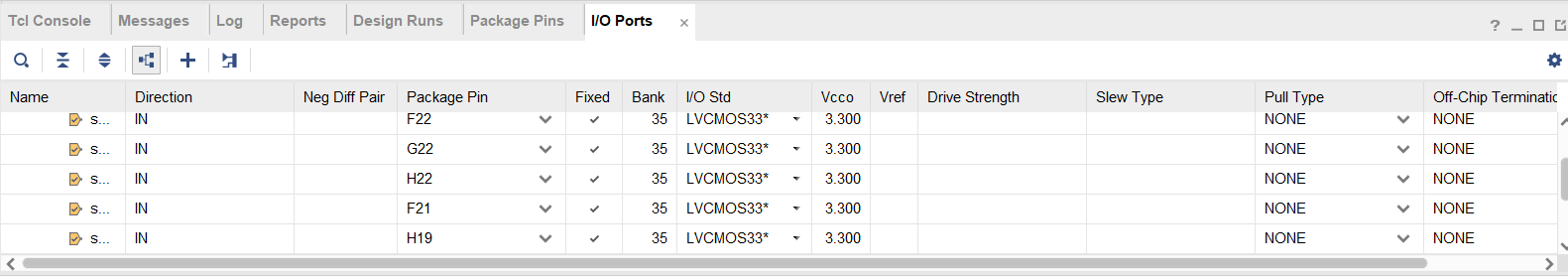

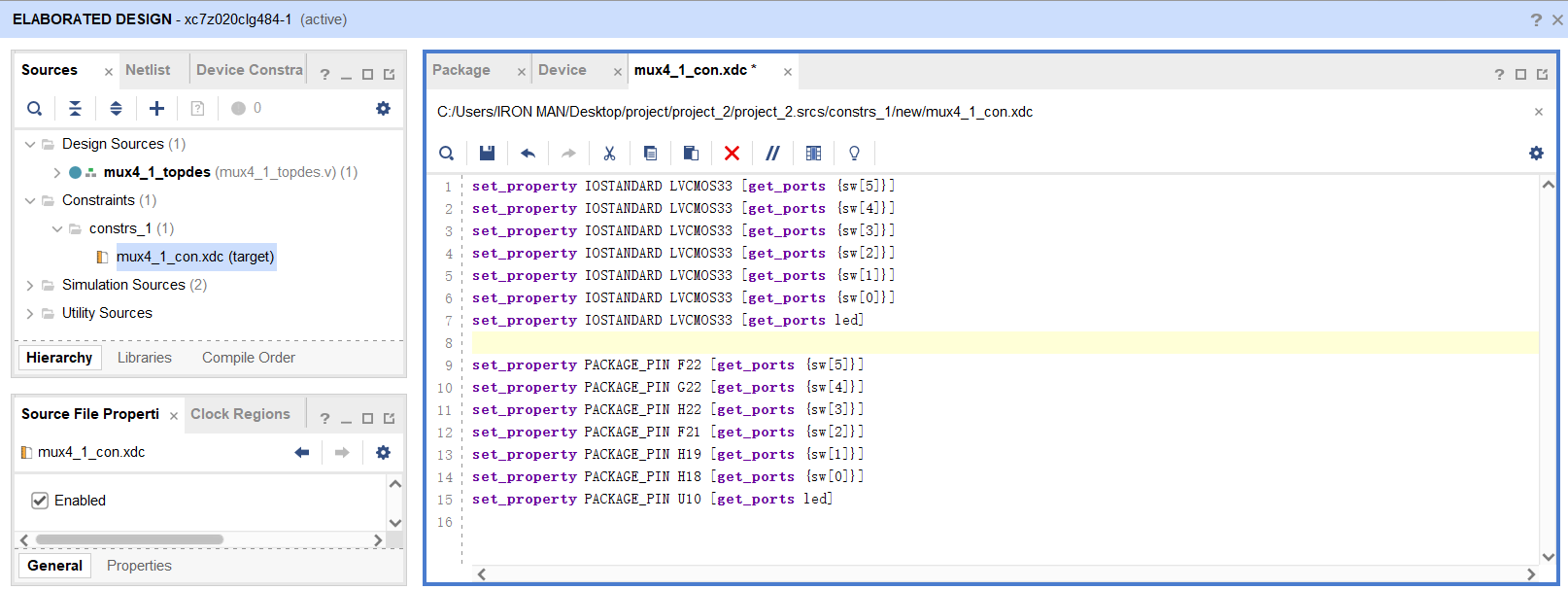

2、约束

创建约束文件(add sources→constraints)

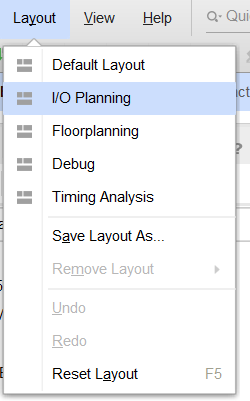

编辑io引脚(layout→I/O planning) ,进行电平约束和引脚约束

然后crtl+s保存至刚刚创立的约束文件

set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports led]

set_property PACKAGE_PIN F22 [get_ports {sw[5]}]

set_property PACKAGE_PIN G22 [get_ports {sw[4]}]

set_property PACKAGE_PIN H22 [get_ports {sw[3]}]

set_property PACKAGE_PIN F21 [get_ports {sw[2]}]

set_property PACKAGE_PIN H19 [get_ports {sw[1]}]

set_property PACKAGE_PIN H18 [get_ports {sw[0]}]

set_property PACKAGE_PIN U10 [get_ports led]

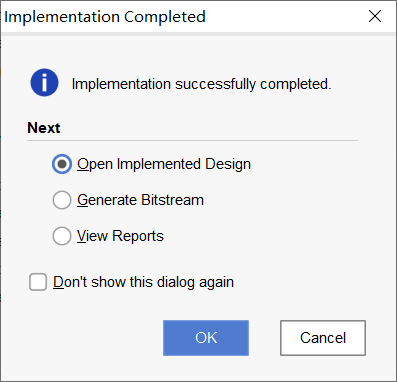

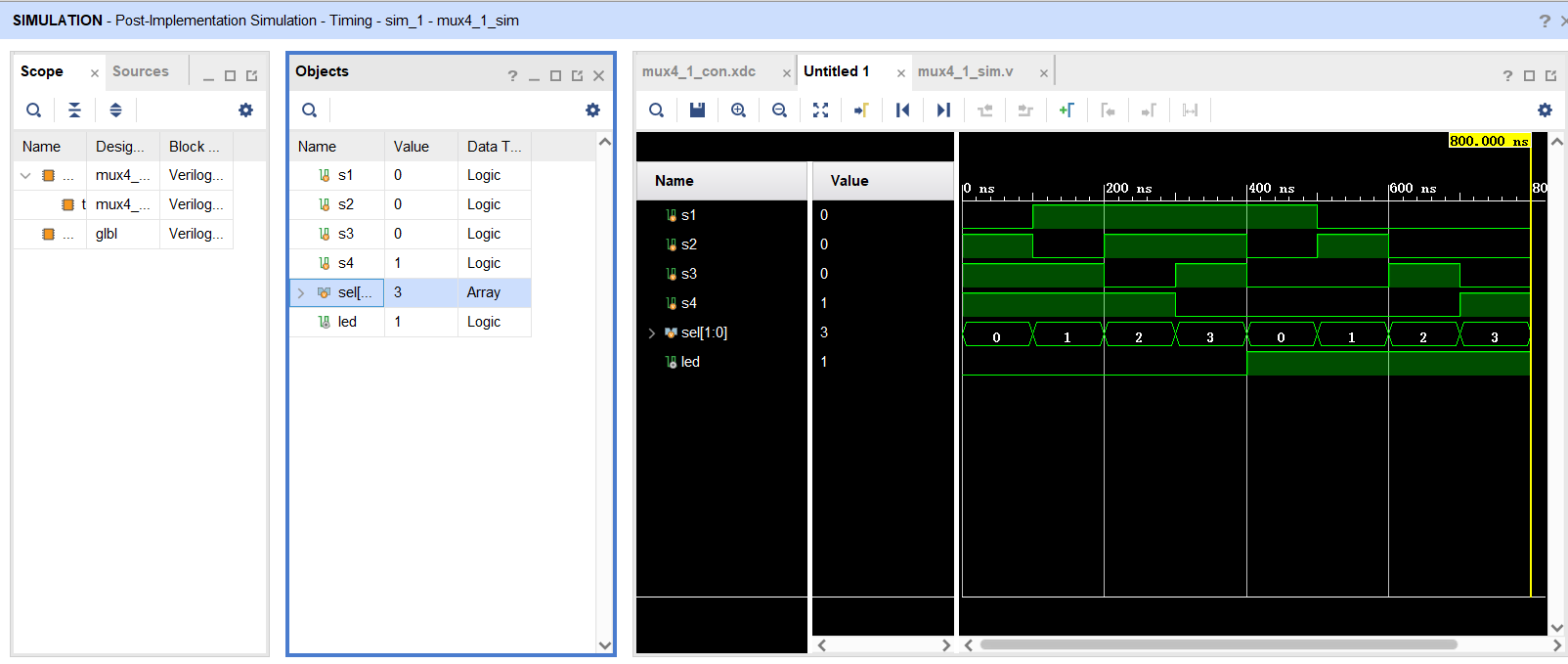

六、实现及时序仿真

1、实现(run implementation)

2、时序仿真(run simulation→run post-implemention timing simulation),时序仿真可以观查延迟,毛刺等,与之前的行为仿真不同。

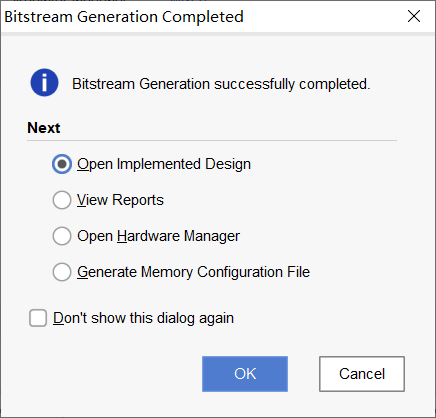

七、下载比特流文件

1、生成比特流文件(generate bitstream)

2、打开硬件管理(Open hardware manager)→打开目标(open target)→自动连接(auto connect)→program device(下载到FPGA核心板上)

3、实物测试

(板子目前还没到,暂时没有做测试)

最后

以上就是可耐猫咪最近收集整理的关于FPGA初识:四选一多路选择器实例练习的全部内容,更多相关FPGA初识内容请搜索靠谱客的其他文章。

发表评论 取消回复