localparam IDLE = 0,

START = 1,

RUN = 2;

STOP = 3;

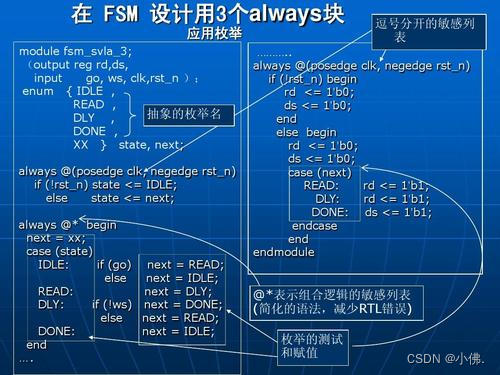

//第一个always块,时序逻辑,描述现态转移到次态

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

current_state <= IDLE;

else

current_state <= next_state;

end

//第二个always块,组合逻辑,描述状态转移的条件

always @(*)//表示综合器根据always里面的输入变量自动添加,不用自己考虑。

begin

case(current_state)

s1:

if(...) next_state = s2;//组合逻辑,采用阻塞赋值

......

default:......;

endcase

end

//第三个always块,时序逻辑,主要描述本模块在各状态下输出信号的值,参考模块的输出信号定义。

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

out1 <= ......;

out2 <= ......;

end

else

case(current_state)

s1: out1 <= ......;

s2: out2 <= ......;

default: ......;

endcase

end最后

以上就是潇洒石头最近收集整理的关于verilog中三段式状态机的全部内容,更多相关verilog中三段式状态机内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复