Zeku2022数字IC验证笔试

2、从综合出电路的电路看第一段代码比第二段代码优化的地方是

第一段代码:

always @(posedge ck clk or negedge rst_n) beign if(-rst_n) D<=1b0; else if(A& B) D<= A+B: end

第二段代码:

always @(posedge clk or negedge rst_n)beign if(-rst_n) D<=1'b0; else if(A&B) D <=A+B; else D<= 1'b0; end

A第一段代码比第二段代码简练,方便综合;

B.第一段代码比第二段代码省功耗;

C.第一段代码比第二段代码的电路简单;

D.第一段代码比第二段代码易于理解和实现;

第一段电路不翻转,综合起来第二段简单,直接ab与门接到输入上

3、logic [1:0] a; logic [1:0] b; logic result; a=2'b1z; b=2'b10; result=(a==b);在sv中,上述代码执行完后,result的值为1'b0

A.正确

B.错误

输出x

4、以下不能抑制异步电路问题的是

A寄存三拍

B.双向握手

C.格雷码转换

D.缓存输出

难道是因为三拍不能解决多bit问题?

5、亚稳态对电路影响极大,下面哪种做法对降低亚稳态发生概率是无效的

A增加异步处理的打拍级数

B使用专用亚稳态寄存器进行替换异步处理逻辑

C.提高异步处理电路的工作时钟

D.缩短异步处理打拍逻辑之间的delay

提高工作时钟降低MTBF

6、无复位寄存器会引入不定态,因此设计中禁止使用无复位寄存器

A正确

B.错误

在IC设计中,处于减少功耗和面积的考虑会存在部分的无复位寄存器和存储单元,而在使用VCS进行后仿真时,无复位的寄存器和存储单元输出会是X态,因此会导致仿真异常,仿真结果不符合预期,因此在仿真时,需要对无复位的寄存器和存储单元进行初始化。

使用$deposit初始化无复位寄存器存储

7、bufif0 # (5:7:9, 8:10:12, 15:18:21)b1 (lo1.1o2, dir).其中第一个5:7:9表示什么

A min typ: max

B. rise; fall turn-off

bufif0三态门原语:bufif0 (output,input,enable) 0 表示低电平使能,en为0时输入等于输出,为1输出高阻。#后三个参数表示,上升延时,下降延时和关断延时,关断延时,就是en作用的时间

8、在时钟上升沿时采样别start有效开始,两个时钟周期后,信号“a”连续或者间断地出现3次为高电平,紧接着信号“stop”在下一个时钟周期为高电平,转换成断言描述。以下哪个是正确的( )

A. property p0: @(posedge clk) $rose (start)1 ##2 (a[=>3]) ##1 stop endpropery

a0 assert property(p0).

B. property p0:

@(posedge clk) $rose(start)|-> ## 2 (a[*3]) ##1 stop.

endproperty

a0 assert property(p0):

C property p0:

@(posedge clk) $rose(star)|-> ##2 (a[=>3]) ##1 stop;

endproperty

a0: assert property(p0),

D. property p0:

@(posedge clk) $rose(start) |-> ##2 (a[=3]) ##1 stop,

endproperty

a0: assert property(p0);

[->n]: go to repetion operator。Indicates there's one or more delay cycles between each repetition of the expression

9、对于FPGA内部的RAM而言,以下哪个说法是错误的?

A配置成伪双端口RAM时,两个端口均有各自独立的读写控制信号

B.配置成伪双端口RAM时,两个端口,可以使用不同的时钟

C.配置成单端口RAM时,仅有一个时钟,用于读操作和写操作

D.配置成单端口RAM时,仅有一组访问地址,用于读操作或写操作

-

单口 RAM 只有一个时钟(clka)(时钟上升沿到来时对数据进行写入或者读出)、一组输入输出数据线(dina & douta)、一组地址线(addra)、一个使能端(ena)(“ena == 1”时可进行读或写的操作,“ena == 0”时无法进行读或写的操作)、一个写使能端(wea)(在“ena == 1”的情况下:“wea == 1”时只写不读,“wea == 0”时只读不写)。单口读、写无法同时进行,只能或读或写。

-

伪双口 RAM 有两个时钟(clka & clkb)、一组输入输出数据线(dina & doutb)、两组地址线(addra & addrb),两个使能端(ena & enb)、一个写使能端(wea)。一个端口只读(Port a),另一个端口只写(Port b)。整体上,读、写可以同时进行。

-

真双口 RAM 有两个时钟(clka & clkb)、两组输入输出数据线(dina & douta & dinb & doutb)、两组地址线(addra & addrb),两个使能端(ena & enb)、两个写使能端(wea & web)。两个端口都可以进行读写操作(Port a 和 Port b 可以一起读或者一起写或者一个读一个写)。整体上,读、写可以同时进行。

10、关于静态时序分析(STA)哪项说法是错误的?

A. B不需要仿真向量

B. C不能验证设计的功能

C. A分析速度快

D. D可以分析同步路径和异步路径

11、验证环境中提到的参考模型(Reference Model)只支持不带时序的功能建模,不支持时序建模

A.错误

B.正确

12、如果该class会被继承,则该class所有定义的function/task都需要加virtual

A.错误

B.正确

父类有virtual即可

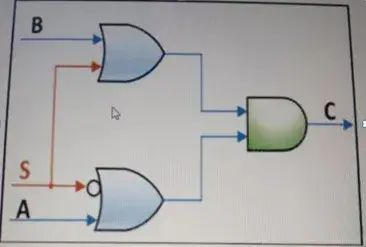

13、下列选项表达式逻辑实现功能,与图中电路实现功能不同的是

A (A+S—) (B+S)

B. A·B+A·S+B·S—+S·S—

C. A·S+B·S—

D. A(B+S—)+5 (B+5S)

选项看不出来...

14、关于下面约束,说法正确的是() constraint ST{ (a==0)-> (b==0) }

A如果a! =0,则b! =0

B如果bl=0,则al=0

C.如果b==0,则a==0

15、有关中断,以下说法不正确的是?

A.芯片中断引脚送出的中断信号一般采用脉冲信号

B.中断读清方式是指在CPU完成对中断指示寄存器的读操作后将中断指示寄存器清零。

C.中断存在边缘触发方式和电平触发方式

D.1根中断管脚可以过度多个芯片内部中断

16、以下低功耗措施中,哪种不是降低电路翻转率的方法?

A重新安排“if-else”表达式,可将毛刺或快变化信号移至逻辑锥体的前部

B.采用Gray码或One-hot码作为状态机编码

C.在不进行算术运算的时候,使这些模块的输入保持不变,不让新的操作数进来.

D.减少电路中的glitch

应该放在后面 应该将毛刺或快变信号移至逻辑椎体的后部,if-else越往后,被选择的概率越小。可以把逻辑延迟大的部分移至逻辑椎体的前部,来减小总的最大延迟,因为在前部意味着最小的选择路径长度。

17、以下SV程序的运行结果为() :

class Test;

bit [31:0] addr;

function void display_addr;

$display("%h", addr);

endfunction

endclass:Test

initial begin

Test t1;

t1 = new();

t1.display_addr();

end

A以上选项均不对

B.1.0

C. X

D.0

18、以下信号命名中不符合Verilog语法的是: ( )

A. 1_2CorrectName

B. CNTO

C. _R1_D2

D. COunT

19、关于三段式状态机的描述,下列说法正确的是( )

A.输出必须是寄存器输出

B.描述状态转移条件和转移规律的逻辑是时序逻辑

C.描述状态转移时,可以不指定default态。

D.描述状态迁移的逻辑为时序逻辑

20、有关功耗,以下说法不正确的是?

A.设计层次越高,功耗优化所能达到的效果越好。

B.电压越大,工作频率越高,其动态功耗越高

C.低功耗设计的目标就是采用各种优化技术和方法,在各个设计目标之间找到最佳

D.芯片单位面积的动态功耗和静态功耗的随着工艺的发展呈下降趋势

21、generate for循环语句中使用的标尺变量可定义为integer

A.正确

B.错误

必须为genvar

22、 Interface 中可以定义信号、函数、任务、class对象;也可以有always,initial语句块

A.错误

B.正确

23、下列不属于动态数组内建函数的是( )

A. delete()

B. size()

C. new[]

D. length()

24、isolation cell是下面哪种低功耗技术必需的

A. Power Gating

B. Clock Gating

C. Mutli_Vdd

D. AVS

25、a1和a2的检查效果完全一样:

property p1:

@(posedge clk) aj=>bj=>c;

endproperty

a1: assert property(p1);

property p2:

@(posedge clk)a ##1 b ##1 |-> c;

endproperty

a2: assert property(p2);

A.错误

B.正确

26、漏电流(Leakage Current)与逻辑电路设计的工作频率无关

A.错误

B.正确

与电压、温度、工艺有关

27、reg signed [0:4]c ; c=8'sh8f; 赋值后c的值是多少?

A. 15

B. 17

C. -15

4‘shx赋值方式是符号位高位扩展 就算赋值给unsigned变量也会扩展符号位

28、在Verilog中,"assign din[31:0]=32'hFF00_ABC4;assign dout[31:0]=(din<2)>4. dou的值是多少?

A 32'h00FF00AB

B.32'hFFFF00AB

C 32'h0x3FC02AF1

D.32'h0FC02AF1

29、假设输入信号X位宽为12bit,InA位宽为6bit,InB位宽为17bit,实现Y=X*InA+InB功能,并要求不损失精度,那么输出信号Y位宽应不小于(所有数据均为有符号数) ( )

A. 12bit

B. 17bit

C. 19bit

D.18bit

30、在Verilog设计中,下列说法不正确的是 ()

A.如果setup时间不满足,可以尝试降低时钟频率解决

B.在边沿敏感时序逻辑代码中,应使用非阻塞赋值(<=)

C.要求always块产生组合逻辑时使用阻塞赋值(=)

D.模运算符"%"是不可综合的

模运算可综合,除法不可综合

31、对于设计中所使用的Pipeline,说法中正确的有

A.使用Pipeline会导致数据延时增加,但如果工作频率不变,系统的吞吐量不会改变。

B.使用Pipeline会对时序有好处,STA更容易通过。

C.使用Pipeline一定可以减少面积。

D.使用Pipeline可能会导致面积增大。

32、下列哪些设计可能会对芯片DFT产生不利影响

A.门控时钟设计

B.使用双沿时钟设计

C.内部三态门总线

D.使用内部产生的时钟

不太会,求解答

33、下列表达式中,哪些可以使用一个或多个二输入与非门器件实现

A.常数1

B. A

C. A+B

D. AB

34、多比特信号A,在时钟域clk_ a存在从8'd100到8'd101到的变化过程中,若在时钟域clk_b直接采用D触发器采样,可能采样到数据是

A.8'h65

B.8'b01100101

C.8'h64

D.8'd100

ABCD 数据线只有一位变化了,其他位不会有亚稳态问题,可能会是8‘d101 或者8’d100

35、2. Formality是由Synopsys公司开发的一种形式验证(Formal Verification)工具,用于两个Design之间的等价性验证。它可以支持如下哪些等价性验证?

A门级网表对门级网表

B. RTL级对RTL级

C. RTL级对门级网表

36、①: always @(posedge clk or negedge rst_n) begin

if(!rst_n)din_ dly <='h0;

else din_dly <= din;

end

②: always @(posedge clk) begin

din_dly <= din;

end

③: always @(posedge clk) begin

If(!rst_n)din_ dly <= 'h0;

else din_dly <= din;

end

上面三段代码,说法正确的是:

A.②属于无复位寄存器,其PPA更优

B.①属于异步复位逻辑

C.同步复位和异步复位都是在复位时将寄存器状态初始化,所以没有区别

D.③属于同步复位逻辑,rst_n可能通过组合逻辑连接到寄存器D端。

37、基于FPGA和ASIC芯片设计的差异需要关注的有

A.时钟复位

B.时钟顿率

C.memory控制

D.上下电流程

哪位大佬帮忙看看华为2021年数字IC笔试题 - 数字IC设计讨论(IC前端|FPGA|ASIC) - EETOP 创芯网论坛 (原名:电子顶级开发网) -

38、报文处理设计规格:

支持的报文长度为36-256字节,其余长度的报文直接丢弃;

接收的报文长度小于64字节时填充PAD (任意数据)使报文长度达到64字节,然后再转发;下面描述错误的是:

A.因为填充PAD是任意数据,因此随便挑一组特殊值,例如全0验证即能够保证功能正确

B.因为大于256B的报文被丢弃了,所以不需要验证该点

C.因为小于36B的报文被丢弃了,所以不需要验证该点

D.该报文处理长度的边界点包含两个值,分别为36和256

不确定

39、下列哪些是必须的,在Post-Layout时序仿真时?

A.Post-Layout网表

B.综合网表

C.标准延时格式文件

D.RTL代码

不确定

40、当模块的代码覆盖率达到100%时,下列说法错误的是

A.并不能确保验证工作已经完成

B.可确认各类用例的激励构造已经完备

C.可确认各种边界点的测试已经足够充分

D.可确认功能验证充分

最后

以上就是腼腆蓝天最近收集整理的关于ZEKU2021数字IC验证笔试题(解析)Zeku2022数字IC验证笔试的全部内容,更多相关ZEKU2021数字IC验证笔试题(解析)Zeku2022数字IC验证笔试内容请搜索靠谱客的其他文章。

发表评论 取消回复