2018.10.05

书目:Verilog HDL数字设计与综合第二版 夏宇闻

门延迟

1、上升下降与关断延迟

2、上升延迟:门的输入发生变化,从0,x,z变化到1所需要的时间

3、下降延时:门的输出从1,x,z变化为0所需时间

4、关断延迟为输出0,1,x变为z所需时间

5、如果值变化到x,则所需时间为以上延迟中最小的那个

6、and #(delay_time)a1(out,i1,i2) 以上三中延迟均为delay_time

7、and #(rise_val,fall_val)a1(out,i1,i2) 描述了上升延迟和下降延迟,关断延迟为二者中较小那个

8、and #(rise_val,fall_val,turnoff_val)a1(out,i1,i2)描述了三种延迟

9、最小、典型、最大延迟

10、最小值:设计者预期逻辑门所具有的最小延迟

11、典型值:设计者预期逻辑门所具有的典型延迟

12、最大值:设计者预期逻辑门所具有的最大延迟

以 out=a·b+c为例进行延迟仿真

`timescale 1 ns/ 1 ps //模块d的说明

module triple_gate(out,in1,in0,s);

output out;

input in1,in0,s;

bufif0 #(1:3:5,3:4:5,5:6:7) b1(out,in0,s);

bufif1 #(1:3:5,3:4:5,5:6:7) b2(out,in1,s);

endmodule

激励模块,testbench

`timescale 1 ns/ 1 ps

module triple_gate_vlg_tst();

// constants

// general purpose registers

reg in0;

reg in1;

reg s;

// wires

wire out;

// assign statements (if any)

triple_gate i1 (

// port map - connection between master ports and signals/registers

.in0(in0),

.in1(in1),

.out(out),

.s(s)

);

initial

begin

in1=1'b0;in0=1'b1;s=1'b0;

#10 in1=1'b1;in0=1'b1;s=1'b0;

#10 in1=1'b1;in0=1'b0;s=1'b1;

#10 in1=1'b0;in0=1'b0;s=1'b1;

#50 $stop;

end

endmodule

注意在.v文件开始加入时间宏定义,否则可能在modesim中无法进行仿真。

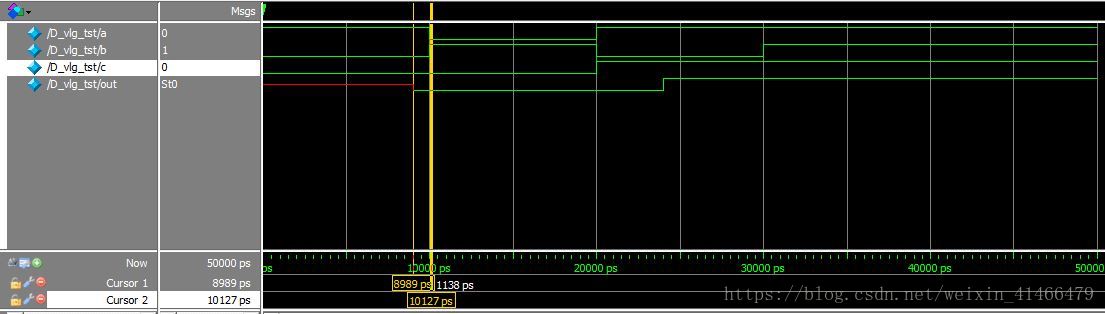

将以上文件利用quartus进行仿真即可得到结果

最后

以上就是纯情樱桃最近收集整理的关于quartus ii 门级延迟仿真的全部内容,更多相关quartus内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复