目录

一、锁存器

二、触发器

三、寄存器

四、移位寄存器

五、总线收发器/缓冲器

六、锁存器与触发器的区别

七、D触发器和D锁存器的区别

八、寄存器与锁存器的区别

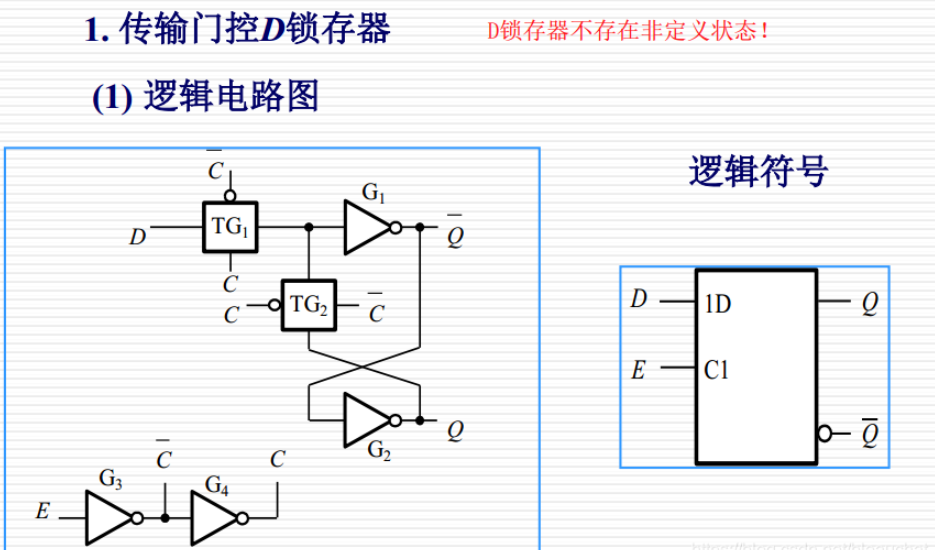

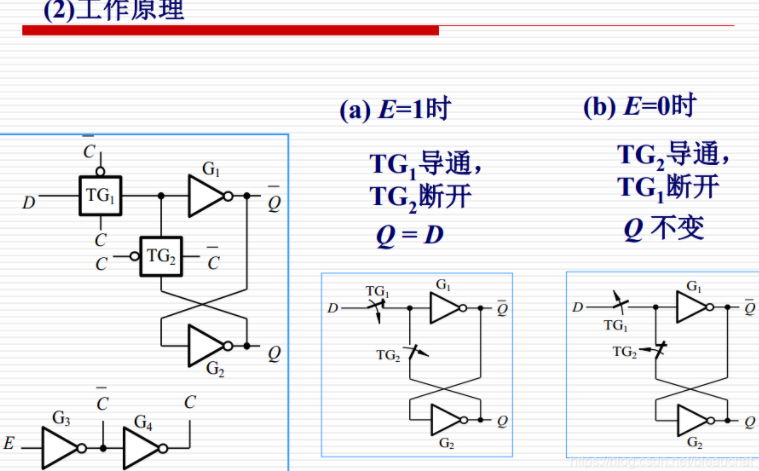

一、锁存器

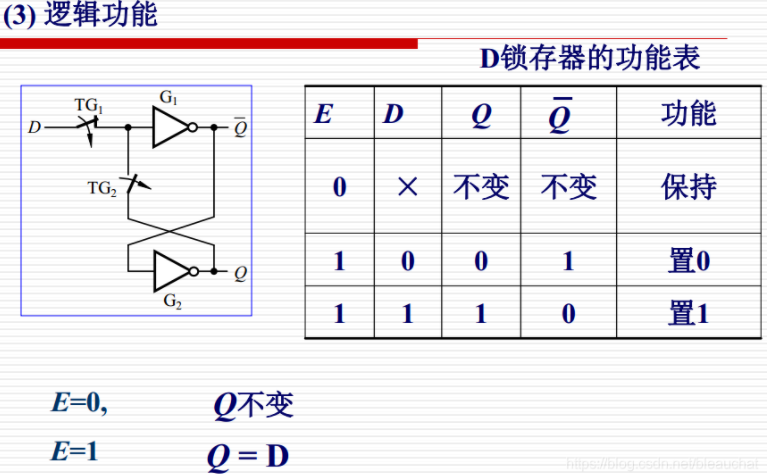

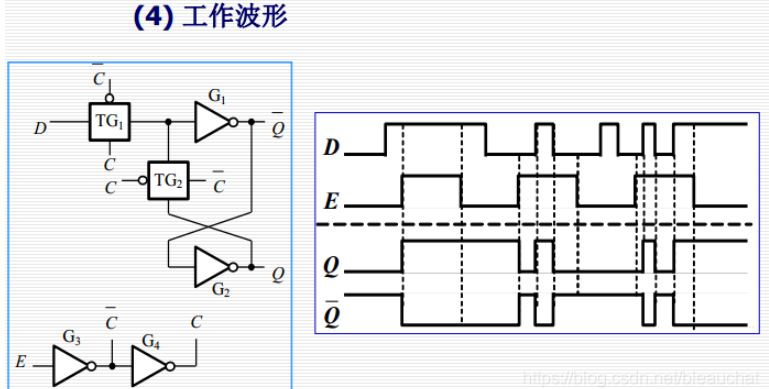

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

锁存器不同于触发器,它不在锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓冲器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。锁存器也称为透明锁存器,指的是不锁存时输出对于输入是透明的。

锁存器(latch):我听过的最多的就是它是电平触发的,呵呵。锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。(简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程)。应用场合:数据有效迟后于时钟信号有效。这意味着时钟信号先到,数据信号后到。在某些运算器电路中有时采用锁存器作为数据暂存器。

缺点:时序分析较困难。

不要锁存器的原因有二:1、锁存器容易产生毛刺,2、锁存器在ASIC设计中应该说比ff要简单,但是在FPGA的资源中,大部分器件没有锁存器这个东西,所以需要用一个逻辑门和ff来组成锁存器,这样就浪费了资源。

优点:面积小。锁存器比FF快,所以用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。(简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程);

应用场合:数据有效滞后于时钟信号有效,这意味着时钟信号先到,数据信号后到。在某些运算器电路中有时采用锁存器作为数据暂存器 ;

优点:面积小、锁存器比FF快,所以用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多;

缺点:时序分析较困难;

不用锁存器的原因有二:1、锁存器容易产生毛刺,2、锁存器在ASIC设计中应该说比FF要简单,但是在FPGA的资源中,大部分器件没有锁存器这个东西,所以需要用一个逻辑门和FF来组成锁存器,这样就浪费了资源;

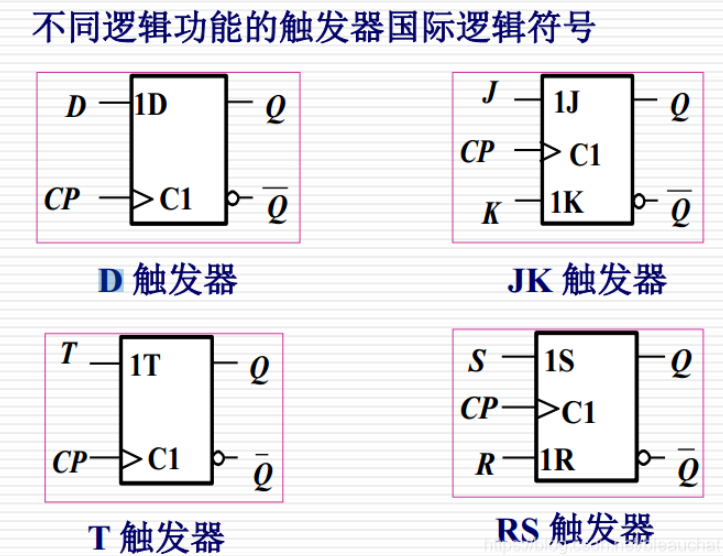

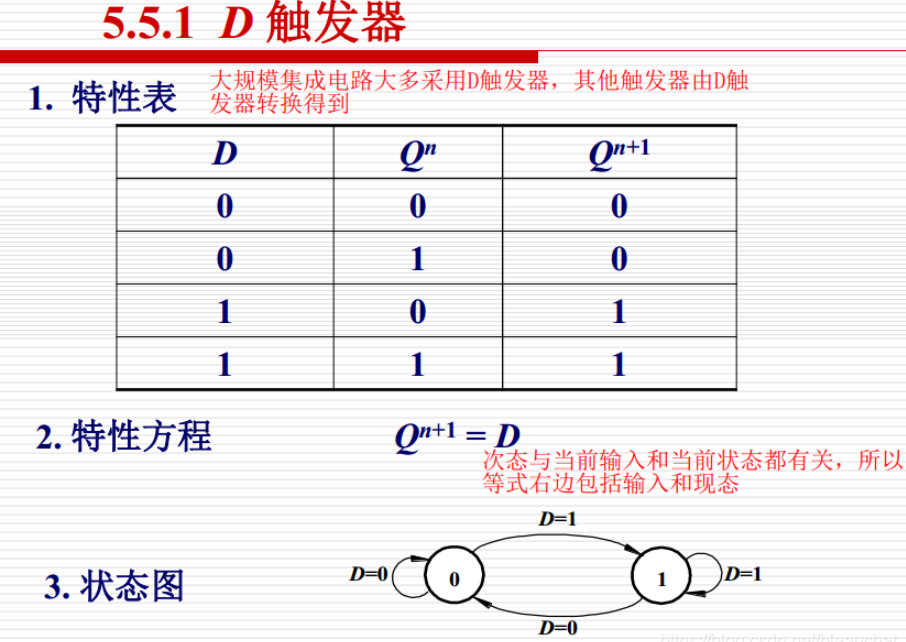

二、触发器

触发器(Flip-Flop,简写为 FF),也叫双稳态门,又称双稳态触发器。是一种可以在两种状态下运行的数字逻辑电路。触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。当收到输入脉冲时,触发器输出就会根据规则改变状态,然后保持这种状态直到收到另一个触发。

触发器(flip-flops)电路相互关联,从而为使用内存芯片和微处理器的数字集成电路(IC)形成逻辑门。它们可用来存储一比特的数据。该数据可表示音序器的状态、计数器的价值、在计算机内存的ASCII字符或任何其他的信息。

触发器(Flip-Flop,简写为 FF)---对脉冲边沿敏感,其状态只在时钟脉冲的上升沿或下降沿的瞬间改变 ;

触发器也叫双稳态门,又称双稳态触发器,是一种可以在两种状态下运行的数字逻辑电路。触发器一直保持它们的状态,直到它们收到输入脉冲,又称为触发。当收到输入脉冲时,触发器输出就会根据规则改变状态,然后保持这种状态直到收到另一个触发 ;

应用场合:时钟有效迟后于数据有效。这意味着数据信号先建立,时钟信号后建立。在CP上升沿时刻打入到寄存器。

三、寄存器

寄存器(register):用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果,它被广泛的用于各类数字系统和计算机中。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。 工程中的寄存器一般按计算机中字节的位数设计,所以一般有8位寄存器、16位寄存器等。

对寄存器中的触发器只要求它们具有置1、置0的功能即可,因而无论是用同步RS结构触发器,还是用主从结构或边沿触发结构的触发器,都可以组成寄存器。一般由D触发器组成,有公共输入/输出使能控制端和时钟,一般把使能控制端作为寄存器电路的选择信号,把时钟控制端作为数据输入控制信号。

寄存器的应用

- 可以完成数据的并串、串并转换;

- 可以用做显示数据锁存器:许多设备需要显示计数器的记数值,以8421BCD码记数,以七段显示器显示,如果记数速度较高,人眼则无法辨认迅速变化的显示字符。在计数器和译码器之间加入一个锁存器,控制数据的显示时间是常用的方法。

- 用作缓冲器;

- 组成计数器:移位寄存器可以组成移位型计数器,如环形或扭环形计数器。

四、移位寄存器

移位寄存器:具有移位功能的寄存器称为移位寄存器。

寄存器只有寄存数据或代码的功能。有时为了处理数据,需要将寄存器中的各位数据在移位控制信号作用下,依次向高位或向低位移动1位。移位寄存器按数码移动方向分类有左移,右移,可控制双向(可逆)移位寄存器;按数据输入端、输出方式分类有串行和并行之分。除了D边沿触发器构成移位寄存器外,还可以用诸如JK等触发器构成移位寄存器。

五、总线收发器/缓冲器

缓冲寄存器:又称缓冲器缓冲器(buffer):多用在总线上,提高驱动能力、隔离前后级,缓冲器多半有三态输出功能。当负载不具有非选通输出为高阻特性时,将起到隔离作用;当总线的驱动能力不够驱动负载时,将起到驱动作用。由于缓冲器接在数据总线上,故必须具有三态输出功能。

它分输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU与慢速工作的外设起协调和缓冲作用,实现数据传送的同步。

Buffer:缓冲区,一个用于在初速度不同步的设备或者优先级不同的设备之间传输数据的区域。通过缓冲区,可以使进程之间的相互等待变少,从而使从速度慢的设备读入数据时,速度快的设备的操作进程不发生间断。

缓冲器主要是计算机领域的称呼。具体实现上,缓冲器有用锁存器结构的电路来实现,也有用不带锁存结构的电路来实现。一般来说,当收发数据双方的工作速度匹配时,这里的缓冲器可以用不带锁存结构的电路来实现;而当收发数据双方的工作速度不匹配时,就要用带锁存结构的电路来实现了(否则会出现数据丢失)。

缓冲器在数字系统中用途很多:

(1)如果器件带负载能力有限,可加一级带驱动器的缓冲器;

(2)前后级间逻辑电平不同,可用电平转换器加以匹配;

(3)逻辑极性不同或需要将单性变量转换为互补变量时,加带反相缓冲器;

(4)需要将缓变信号变为边沿陡峭信号时,加带施密特电路的缓冲器

(5)数据传输和处理中不同装置间温度和时间不同时,加一级缓冲器进行弥补等等。

六、锁存器与触发器的区别

锁存器和触发器是具有记忆功能的二进制存贮器件,是组成各种时序逻辑电路的基本器件之一。区别为:latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;flip-flop受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。当然因为latch和flip-flop二者都是时序逻辑,所以输出不但同当前的输入相关还同上一时间的输出相关。

1、latch由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。DFF由时钟沿触发,同步控制。

2、latch对输入电平敏感,受布线延迟影响较大,很难保证输出没有毛刺产生;DFF则不易产生毛刺。

3、如果使用门电路来搭建latch和DFF,则latch消耗的门资源比DFF要少,这是latch比DFF优越的地方。所以,在ASIC中使用 latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现。latch是电平触发,相当于有一个使能端,且在激活之后(在使能电平的时候)相当于导线了,随输出而变化。在非使能状态下是保持原来的信号,这就可以看出和flip-flop的差别,其实很多时候latch是不能代替ff的。

4、latch将静态时序分析变得极为复杂。

5、目前latch只在极高端的电路中使用,如intel 的P4等CPU。 FPGA中有latch单元,寄存器单元就可以配置成latch单元,在xilinx v2p的手册将该单元配置成为register/latch单元,附件是xilinx半个slice的结构图。其它型号和厂家的FPGA没有去查证。——个人认为xilinx是能直接配的而altera或许比较麻烦,要几个LE才行,然而也非xilinx的器件每个slice都可以这样配置,altera的只有DDR接口中有专门的latch单元,一般也只有高速电路中会采用latch的设计。altera的LE是没有latch的结构的,又查了sp3和sp2e,别的不查了,手册上说支持这种配置。有关altera的表述wangdian说的对,altera的ff不能配置成latch,它使用查找表来实现latch。

一般的设计规则是:在绝大多数设计中避免产生latch。它会让您设计的时序完蛋,并且它的隐蔽性很强,非老手不能查出。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。

锁存器电平触发会把输入端的毛刺带入输出;而触发器由于边沿作用可以有效抑制输入端干扰。

在 CMOS 芯片内部经常使用锁存器, 但是在PCB板级结构上, 建议用触发器在时钟边沿上锁存数据。这是因为在锁存器闸门开启期间数据的变化会直接反映到输出端, 所以要注意控制闸门信号的脉冲宽度,而对于触发器,只考虑时钟的边沿。

门电路是构建组合逻辑电路的基础,而锁存器和触发器是构建时序逻辑电路的基础。门电路是由晶体管构成的,锁存器是由门电路构成的,而触发器是由锁存器构成的。也就是晶体管->门电路->锁存器->触发器,前一级是后一级的基础。锁存器和触发器它们的输出都不仅仅取决于目前的输入,而且和之前的输入和输出都有关系。

它们之间的不同在于:锁存器没有时钟信号,而触发器常常有时钟触发信号。

锁存器是异步的,就是说在输入信号改变后,输出信号也随之很快做出改变非常快。而另外一方面,今天许多计算机是同步的,这就意味着所有的时序电路的输出信号随着全局的时钟信号同时做出改变。触发器是一个同步版锁存器。

触发器泛指一类电路结构,它可以由触发信号 (如: 时钟、置位、复位等) 改变输出状态, 并保持这个状态直到下一个或另一个触发信号来到时。触发信号可以用电平或边沿操作,锁存器是触发器的一种应用类型。

七、D触发器和D锁存器的区别

钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器,钟控D触发器在使能情况下输出随输入变化,边沿触发器只有在边沿跳变的情况下输出才变化。

两个锁存器可以构成一个触发器,归根到底还是dff是边沿触发的,而latch是电平触发的。锁存器的输出对输入透明的,输入是什么,输出就是什么,这就是锁存器不稳定的原因,而触发器是由两个锁存器构成的一个主从触发器,输出对输入是不透明的,必须在时钟的上升/下降沿才会将输入体现到输出,所以能够消除输入的毛刺信号。

八、寄存器与锁存器的区别

寄存器与锁存器的功能是提供数据寄存和锁存。

寄存功能是指把数据暂时保存,需要时取出。锁存功能是指总线电路中,锁定数据输出,使输出端不随输入端变化。

1.本文部分素材来源网络,版权归原作者所有,如涉及作品版权问题,请与我联系删除。

2.未经原作者允许不得转载本文内容,否则将视为侵权;

3.转载或者引用本文内容请注明来源及原作者;

4.对于不遵守此声明或者其他违法使用本文内容者,本人依法保留追究权等。

下面是我的个人微信公众号,关注【一个早起的程序员】精彩系列文章每天不断。

最后

以上就是顺心滑板最近收集整理的关于锁存器、触发器、寄存器和缓冲器的区别的全部内容,更多相关锁存器、触发器、寄存器和缓冲器内容请搜索靠谱客的其他文章。

发表评论 取消回复