基于FPGA的除法器原理介绍及设计实现

引言应用

在FPGA的设计应用领域里,许多电路需要用到除法器,而在硬件描述语言里却没有直接的除法器“%”,“/”可以直接引用运算。许多文献都是单独介绍小数除以大数或者大数除以小数等单一的设计描述,为此本文在参考了许多技术文献之后,提出自己的一种设计方法,不管除数与被除数的大小关系,都可以直接通过算法“减法进位”来推导运算出整数商与余数(小数商)。具有多功效,全方位,可优化,易综合等参考价值。

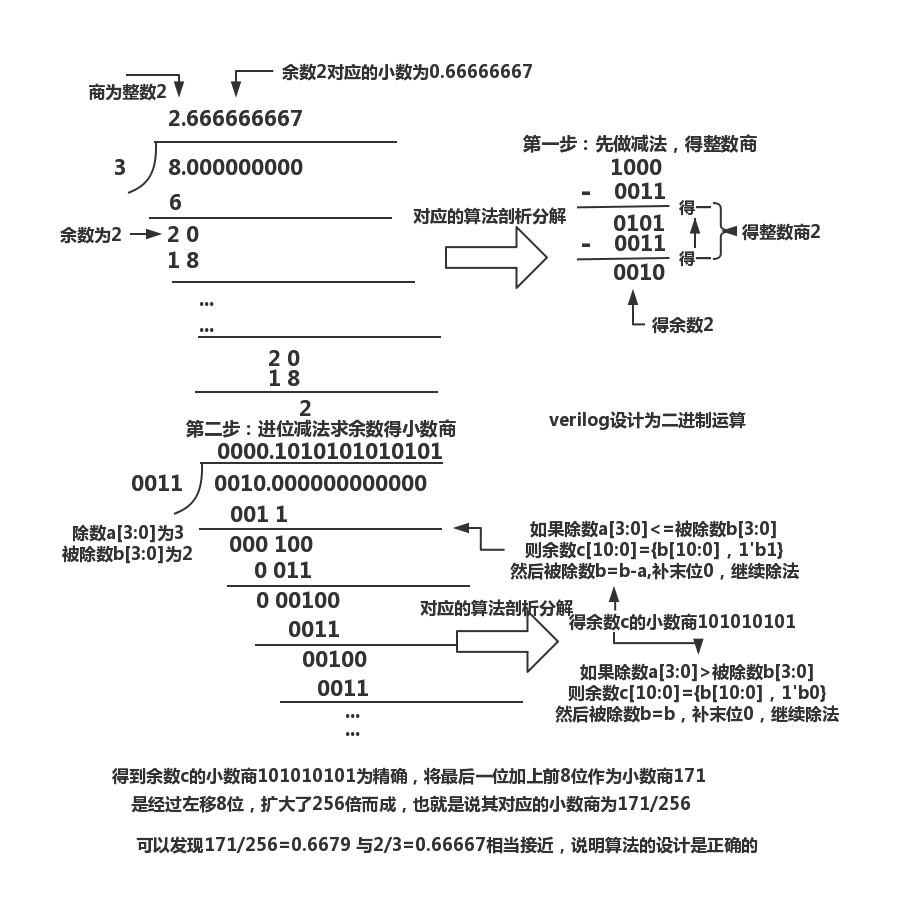

算法原理介绍

算法设计实现

整体设计介绍

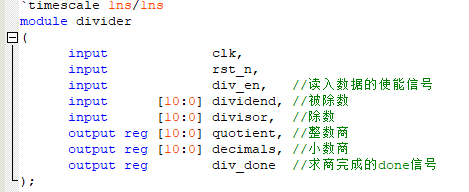

设计端口介绍

dividend为被除数,divisor为除数,quotient为整数商,decimals为小数商

dividend ÷ divisor = quotient.decimals

设计的端口介绍具体如下所示:

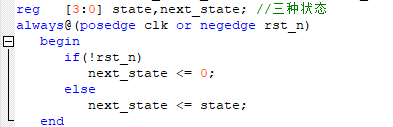

状态机设计

为节省电路面积,使寄存器共用,流程设计更清晰无误,本除法器的设计采用状态机的设计。

状态1:读入除数与被除数;

状态2:进行求整数商的运算;

状态3:进行求小数商的运算;

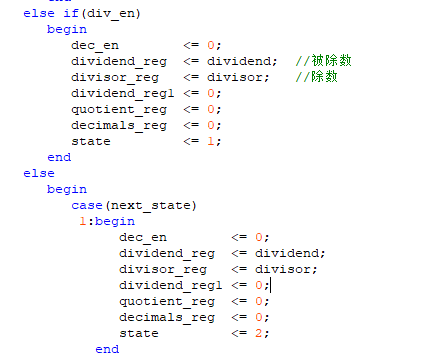

状态1读入除数与被除数

当div_en读入使能信号打开为1,数据读入,state为1,开始读入数据验证。

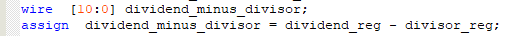

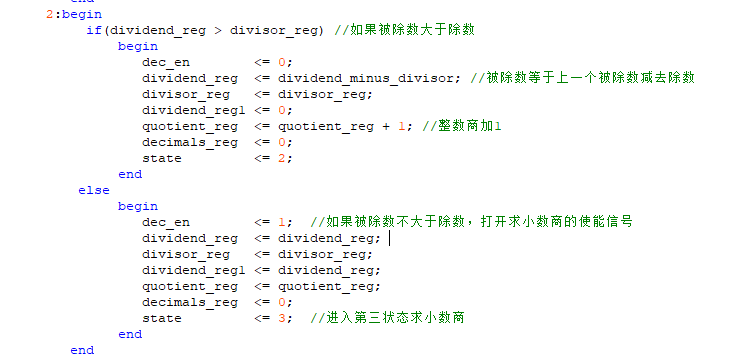

状态2求整数商的设计

在上面所描述到的,如果被除数一开始是大于除数的话,那么在求整数商时,就应该进行减法操作。

状态2求整数商的设计:

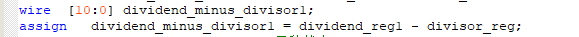

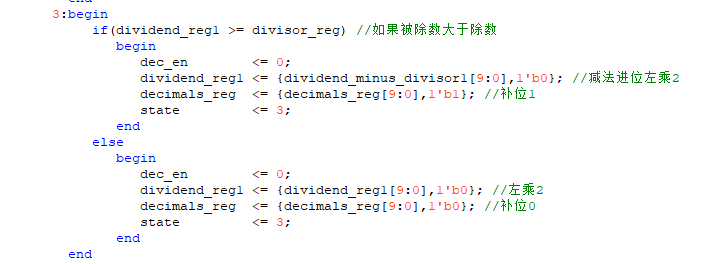

状态3求小数商的设计

在上面的描述到了,如果补位进位后的被除数大于除数,就需要再一次进行减法操作。

状态3小数商的设计:

算法设计验证

算法的设计仿真验证,以被除数165,除数28为验证数据,我们可以自己先计算一下。

165/28=5.8929,也就是说相对于的我们仿真的数据应该是整数商quotient=5,decimals = 0.89286。

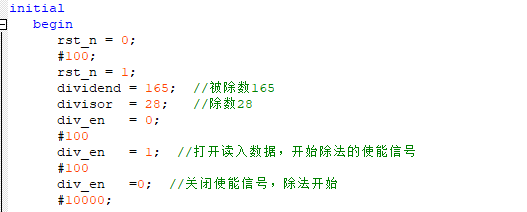

具体的仿真是否符合预期结果,建立仿真环境验证开始:

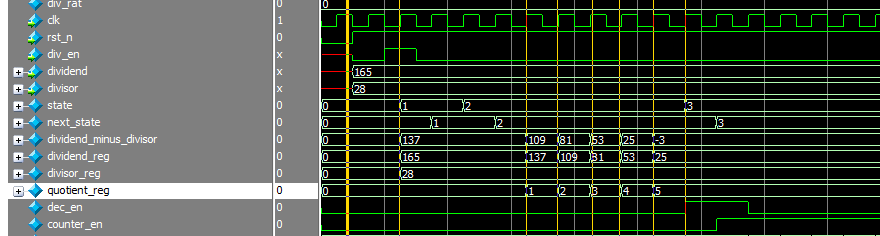

从下面的仿真波形图1可以看得出,在div_en被拉高之后,被除数165,除数28开始读入,进入求整数商操作。

一直在判断被除数dividend_reg是否大于除数divisor_reg,是则整数商quotient-reg一直在加1直到5。—符合我们的设计预期

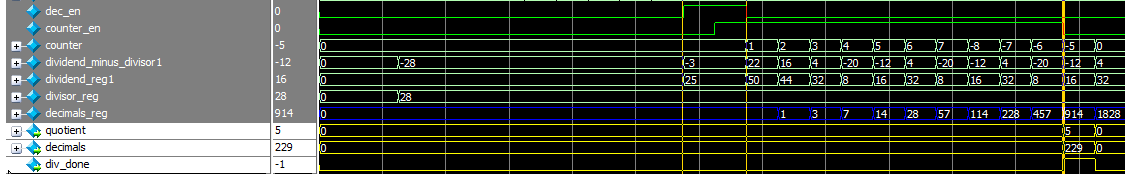

从下面的仿真波形图2可以看到,如上面设计描述所述,在求完整数商后拉高dec_en信号,开始进入状态3求小数商的设计。

得到的小数商decimals=229,在上面的算法原理描述时已经说过,因为被左乘了256倍,所以换算成小数,需再除以256。

因此:229/256=0.8945,与上面预期的165/28=5.8929来说是相当接近的,误差在可控范围内。—符合我们的设计预期

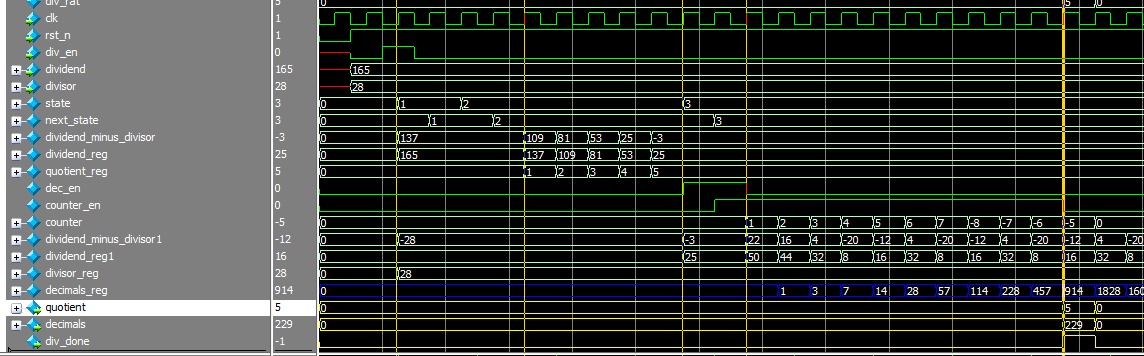

整体的功能仿真波形图如下:

设计总结

到这里除法器的算法设计就已经介绍完毕了,正如前文引言里所描述的,本文的除法器设计具有多功效,全方位,可优化,易综合等参考价

值。其全方位体现在可以提高被除数除数的位宽,扩大其除法范围,另外可以扩展小数商的位宽,这样子求导得到的小数商其误差就会更

小,可适应不同场合误差要求。

本文的设计描述如果有什么地方描述的不清晰的,有不明白的地方都可以加博客发信息询问。后续将介绍平均滤波器的FPGA设计实现,还

有数字后端设计DC,PR,PT,FM等流程,如果有想投稿或者想要我写什么题材的,欢迎提出建议。

最后

以上就是洁净枫叶最近收集整理的关于基于FPGA的除法器原理介绍及设计实现基于FPGA的除法器原理介绍及设计实现的全部内容,更多相关基于FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复